当前位置:网站首页>[2023 Fudan Microelectronics written examination questions in advance] ~ questions and reference answers

[2023 Fudan Microelectronics written examination questions in advance] ~ questions and reference answers

2022-07-27 13:31:00 【AI is very good】

Contents of this chapter :

0. the front

This written examination can only be described in one word — miscellaneous . How dare you believe it ? There are all kinds of questions in a set of papers , Not only have IC Design direction , also IC Verify directional , The most terrible thing is that there is back-end knowledge , It can be described as the selection of all-round talents , It's really a drunken man's intention, not wine !

There are three parts in the exam paper : Base part 、 Optional part 、 Verification part .

There are ten questions in the basic part ; It seems that the optional part is also ten questions ; Five questions in the verification part .

The following is a specific topic , Just memories , Ha ha ha !!!

1. Base part

The first question is

problem

What is? RTL Class design ?

answer

RTL(Register-Transfer-Level), It refers to a way to describe the data flow of a circuit by using the description mode of register . It can be integrated , Therefore, its programming style should be code recognizable by comprehensive tools , Net list can be generated directly through comprehensive tools . It is the upper level of behavior level description , Behavior level description focuses more on algorithms , Generally, the realization and integrability of the circuit are not considered , Only define the input-output relationship , It is more abstract than behavior level description .

Knowledge development

RTL What is the difference between level and gate level ?

RTL It describes the function you want to achieve with hardware description language , Gate level uses specific logic units ( Rely on the manufacturer's Library ) To realize your function , Gate level can finally be processed into actual hardware in semiconductor factory . All in all ,RTL And gate level are different stages of design and implementation ,RTL After logical synthesis , Get the door level .

RTL The description can be expressed as a finite state machine , Or a more general sequential state machine that can transfer registers on the boundary of a predetermined clock cycle , Usually VHDL/verilog Describe in two languages .

To be specific , Soft core can be integrated HDL describe , Hard core is chip layout , Solid core is gate level HDL describe .

The second question is

problem

What is competition ? What is adventure ? How to eliminate ?

answer

Before written , Portal

Third question

problem

Design flow in integrated circuit ? Used in all links EDA Tools ?

answer

Just wrote an article , You can see , Portal

Fourth question

problem

latch and DFF The difference between ?

answer

Before written , Portal

Fifth question

problem

The difference between blocking assignment and non blocking assignment ?

answer

Before written , Portal

Sixth question

problem

DMA The advantages of ?

answer

Question seven

problem

Gave a circuit diagram , Let's talk about how to test a signal for errors ?

answer

This can't be written , Let's talk about my thoughts , I think we have to write the logical expression , After simplification , Give other signals all valid , Just observe the signal that needs to be detected .

The eighth question

problem

Whether the two-level synchronization code is correct ?

answer

Code question , Just brush more questions , Portal

Question 9

problem

Code question : The width of the detection input signal is greater than one clock clock cycle ?

answer

At present, I haven't thought of a good method for this problem , Update later !

Question 10

problem

use CMOS Telephone circuit diagram ?

answer

This question is not within my ability , Ha ha ha , Learn first and then update !

2. Optional part

This part is the last one , Not impressive , Because the time is short , There is no time to finish reading .

3. Verification part

The first question is

problem

What is the coverage of validation ? What's the point ?

answer

The second question is

problem

The verification platform has several parts ?UVM What are the components ? What is factory mode ? What are the key signals ?

answer

Third question

problem

Simulation cannot continue ,stuck In a bit , What is the reason ?

answer

I said it in combination with my personal situation

Fourth question

problem

I forgot this ?

answer

Fifth question

problem

I didn't remember this , Time is too urgent ?

answer

reference

Statement

All my series of articles , Just for learning , Not for commercial use , If there is any infringement , Please inform , To delete !!!

I mainly record the learning process , For myself to review , Then it is to provide reference for future generations , No joy, no spray. !!!

If it's useful to you , Remember to collect + Comment on !!!

边栏推荐

- 利用eBPF探测Rootkit漏洞

- Getting started for beginners: build your own blog with WordPress

- Feign client automatic assembly of three clients

- Feign's dynamic proxy

- Optimization Practice of Flink OLAP job scheduling and query execution based on ByteDance

- PAT乙级 1109 擅长C(详解)

- 52:第五章:开发admin管理服务:5:开发【分页查询admin账号列表,接口】;(Swagger的@ApiParam(),对方法参数进行注释;PageHelper分页插件;拦截器拦截检查登录状态)

- 能说一说 Kotlin 中 lateinit 和 lazy 的区别吗?

- JNI程序如何进行参数传递

- Go语言系列:如何搭建Go语言开发环境?

猜你喜欢

libevent 之 evconnlistener_new_bind

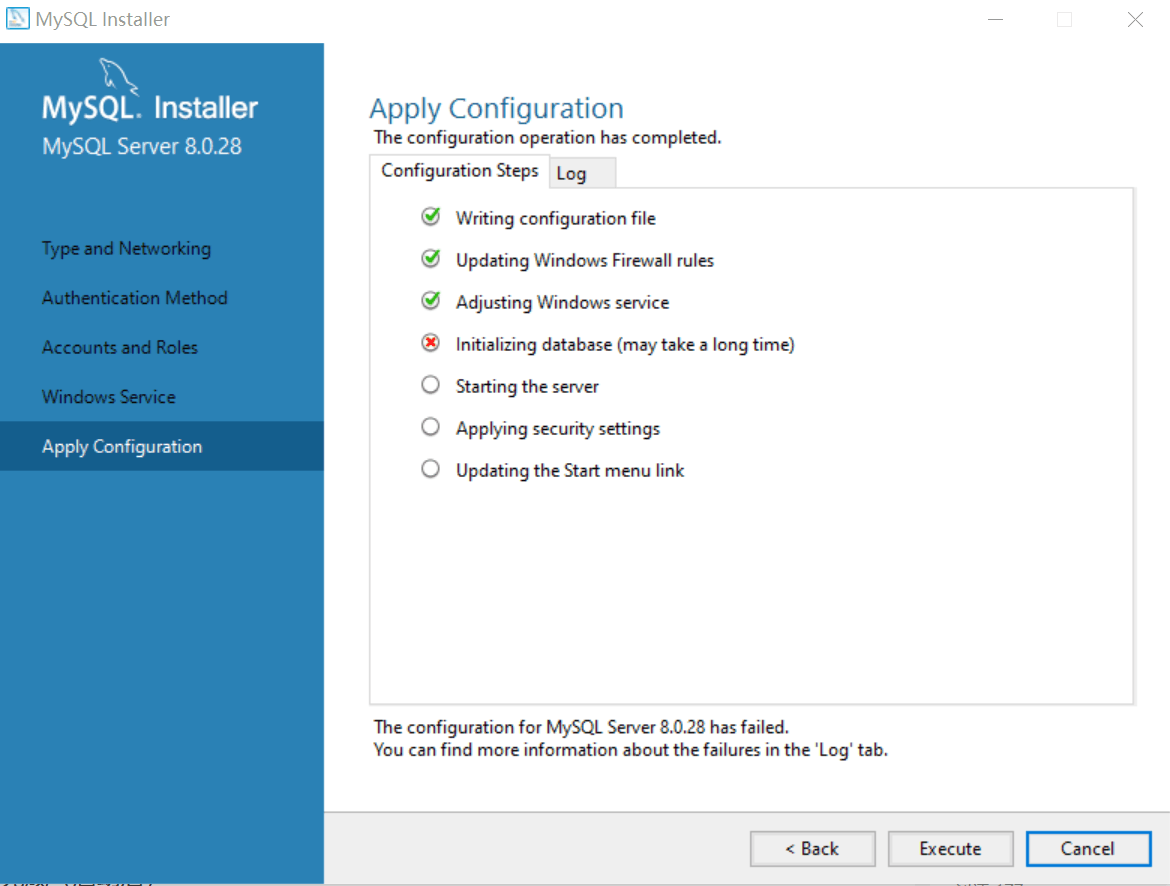

Initializing database error after reinstalling MySQL

Amd adrenalin 22.7.1 driver update: double the performance of OpenGL and support Microsoft win11 22h2 system

v-show

腾讯云联合中国工联院发布工业AI质检标准化研究成果加速制造业智能化转型

初学者入门:使用WordPress搭建一个专属自己的博客

eBPF/Ftrace

leetcode——83,24;机器学习——神经网络

电滑环的常用类型

52:第五章:开发admin管理服务:5:开发【分页查询admin账号列表,接口】;(Swagger的@ApiParam(),对方法参数进行注释;PageHelper分页插件;拦截器拦截检查登录状态)

随机推荐

Amd adrenalin 22.7.1 driver update: double the performance of OpenGL and support Microsoft win11 22h2 system

[300 + selected interview questions from big companies continued to share] big data operation and maintenance sharp knife interview question column (IX)

592. Fraction addition and subtraction: introduction to expression calculation

责任链模式在转转精准估价中的应用

Fixed positioning

双料第一!

【2023复旦微电子提前批笔试题】~ 题目及参考答案

Getting started for beginners: build your own blog with WordPress

How about the strength of database HTAP

libevent 之 evconnlistener_new_bind

52: Chapter 5: developing admin management services: 5: developing [paging query admin account list, interface]; (swagger's @apiparam(), annotate the method parameters; PageHelper paging plug-in; Inte

【基础知识】~ 集成电路设计流程,以及各阶段所使用的EDA工具

C语言犄角旮旯的知识之数组与函数

元素的层级

[node+ts] build node+typescript project

粘制定位

eBPF/Ftrace

clear

Qt优秀开源项目之十三:QScintilla

初探基于OSG+OCC的CAD之任意多个子模型进行netgen以及gmsh网格划分