当前位置:网站首页>Basic structure of arithmetic unit

Basic structure of arithmetic unit

2022-06-12 19:28:00 【Solitary meow】

List of articles

The basic structure of the arithmetic unit

One . Arithmetic logic unit (ALU)

Arithmetic logic unit (arithmetic and logic unit) It can realize multiple groups of arithmetic operations and logical operations Combinational logic circuit , abbreviation ALU.

Through a set of control signals S 0 S 1 S 2 S 3 S_0S_1S_2S_3 S0S1S2S3 Take different values , Can be controlled ALU Do different kinds of arithmetic / Logical operations .

Two . Structure classification of arithmetic unit

Most of the arithmetic units are interconnected by bus . According to the connection mode of the internal bus of the arithmetic unit , The basic structure of the arithmetic unit can be divided into single bus , Dual bus and three bus structure .

1. Single bus structure

The characteristic of single bus structure arithmetic unit is that all components are connected to the same bus , At the same time , Only one operand can be transferred on the bus . Data can be between any two registers , Or in any register and ALU To transmit between . When a double operand instruction is executed , The two operands need to be entered twice ALU, And you need two registers . That is to say, three-step operation control is required ( Corresponding to three clock cycles ) To obtain the operation result . When the operation is over , The operation result is stored in the destination register through the single bus .

The characteristic of single bus structure is that the control circuit is relatively simple , The disadvantage is that the operation speed is relatively slow .

2. Dual bus structure

The characteristic of the dual bus structure arithmetic unit is that the arithmetic related components are connected to two buses , Two data can be transmitted at the same time . When a double operand instruction is executed , Two operands can be loaded into at the same time ALU Carry out operations . But because two buses are occupied by two operands , The operation result cannot be directly added to the bus , So you need to ALU The output end is provided with a register to store the operation results , The operation result can only be written to the destination register in the next clock cycle . in other words , Two operations required ( Two clock cycles ) To get the result of the operation . obviously , The double bus structure arithmetic unit is faster than the single bus structure arithmetic unit .

3. Three bus structure

The characteristic of the three bus structure arithmetic unit is that the operation related components are connected to two buses , Three data can be transmitted at the same time . When a double operand instruction is executed , Two operands can be loaded into at the same time ALU Carry out operations , The third bus outputs the operation result , Just one step ( One clock cycle ) You can complete the operation . In addition, the three bus structure arithmetic unit also has the function of direct transmission , An operand that does not need to be modified can be directly transferred from the input bus to the output bus through the bus switch . Compared with single bus and dual bus structure , The three bus structure arithmetic unit has the fastest operation speed , But the hardware circuit is very complicated .

3、 ... and .ALU Bus data transmission analysis :

1. Analysis of two block diagrams of single bus structure :

(1) Single bus structure 1:

- First bus cycle : Operands 1 Transfer from general register to register via bus 1 in

- Second bus cycle : Operands 2 Transfer from general register to register via bus 2 in

- The third bus cycle : stay ALU After completing the operation , The result is obtained from... Via the bus ALU Transfer back to the general register

(2) Single bus structure 2:

- First bus cycle : Operands 1 Transfer from general register to register via bus 1 in

- Second bus cycle : Operands 2 Transfer from general register to ALU in

- The third bus cycle : stay ALU Complete the operation and store the result directly in the register 2 after , The result is from the register via the bus 2 Transfer back to the general register .

2. For the dual bus structure block diagram analysis :

- The first clock cycle : Operands 1 And operands 2 It is transferred from the general register to... Through two different buses ALU in .

- The second clock cycle : stay ALU After the operation is completed and the result is stored in the register , The result is transferred from the register back to the general register through the bus .

3. For the three bus structure block diagram analysis :

- The first clock cycle : Operands 1 And operands 2 It is transferred from the general register to... Through two different buses ALU in , In a very short time ,ALU The operation is completed and the result is obtained , As a result, the third bus is used to transfer data from ALU Is transferred back to the general register . All the steps are completed in one clock cycle .

A simple block diagram of a computer

边栏推荐

- synchronized下的 i+=2 和 i++ i++执行结果居然不一样

- CVPR 2022 oral Dalian Institute of technology proposed SCI: a fast and powerful low light image enhancement method

- Original introduction to Jenkins' configuration options

- 模塊八作業

- 基于微信电子书阅读小程序毕业设计毕设作品(4)开题报告

- 合理地配置线程池

- [today in history] June 12: the United States entered the era of digital television; Mozilla's original developer was born; 3com merges with American Robotics

- Report on market demand trends and future strategic planning recommendations of the global and Chinese smart financial solutions industry 2022-2028

- [generation confrontation network learning III] reading notes of Bigan paper and its principle understanding

- 基于微信电子书阅读小程序毕业设计毕设作品(6)开题答辩PPT

猜你喜欢

![[0008] unordered list](/img/16/7525d963e68757558dd55ff4d1a23a.png)

[0008] unordered list

【观察】华为下一代数据中心,为广西低碳高质量发展“添动能”

什么是数据驱动

ISCC2022

![leetcode:98. Count the number of subarrays whose score is less than k [double pointers + number of calculated subsets + de duplication]](/img/97/67d74ae93be2cd4c0153a764cbe4c1.png)

leetcode:98. Count the number of subarrays whose score is less than k [double pointers + number of calculated subsets + de duplication]

RT-Thread 模拟器 simulator 搭建 LVGL 的开发调试环境

In 2021, the global revenue of chlorinated polyvinyl chloride (CPVC) was about $1809.9 million, and it is expected to reach $3691.5 million in 2028

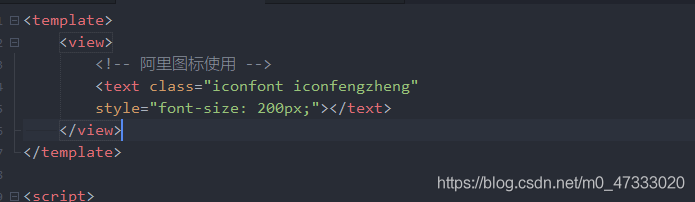

uniapp使用阿里图标

基于分布式数据库本身的定时备份方法

负数取余问题

随机推荐

Wireshark basic commands

typescript的装饰器(Decorotor)基本使用

Lua record

基于微信电子书阅读小程序毕业设计毕设作品(6)开题答辩PPT

leetcode:5289. Distribute cookies fairly [see data range + DFS pruning]

"As a service", the future has come, starting from the present | new mode of it consumption, FOD billing on demand

What is data driven

什么是数据驱动

VC Hacon Joint Programming genimage3extern writeimage

数据库全量SQL分析与审计系统性能优化之旅

Module 8 operation

3D object detection

Start with no place to live

存储体系概述

mysql的增删改查,mysql常用命令

Mysql database experiment I data definition

3GPP RAN第一次F2F会议,都干了些啥?

leetcode:5259. Calculate the total tax payable [simple simulation + see which range]

选电子工程被劝退,真的没前景了?

uniapp使用阿里图标