当前位置:网站首页>【数字IC验证快速入门】7、验证岗位中必备的数字电路基础知识(含常见面试题)

【数字IC验证快速入门】7、验证岗位中必备的数字电路基础知识(含常见面试题)

2022-07-05 20:06:00 【luoganttcc】

导读:作者有幸在中国电子信息领域的排头兵院校“电子科技大学”攻读研究生期间,接触到前沿的数字IC验证知识,旁听到诸如华为海思、清华紫光、联发科技等业界顶尖集成电路相关企业面授课程,对数字IC验证有了一些知识积累和学习心得。为帮助想入门前端IC验证的朋友,思忱一二后,特开此专栏,以期花最短的时间,走最少的弯路,学最多的IC验证技术知识。

前言

本节将会主要介绍以下几个板块的内容:

- 数字电路基础:CMOS器件

- 数字电路功耗

- 摩尔定律:22nm FinFET工艺

- 数字组合电路逻辑器件:与门、或门、非门

- 数字时序电路逻辑器件:寄存器、锁存器

- 数字电路数值表示

- 数字电路的补码表示

- 数字布尔逻辑

坦白讲,这部分内容对于日后的验证岗位用的并不是很多,但是对于面试很有用,并且这些也是一个职业验证工程师应具备的基本素养,也是区分是否科班出身的关键之一。还有一点要说的是,通常应届生面试,设计和验证并不会区分太明显,所以要尽可能扩充自己知识体系的广度,同时也要有验证知识体系的深度!

一、数字电路基础:CMOS器件

COMS(Complementary Metal Oxide Semiconductor)通常指的是互补金属氧化物半导体。

1.1、MOS晶体管

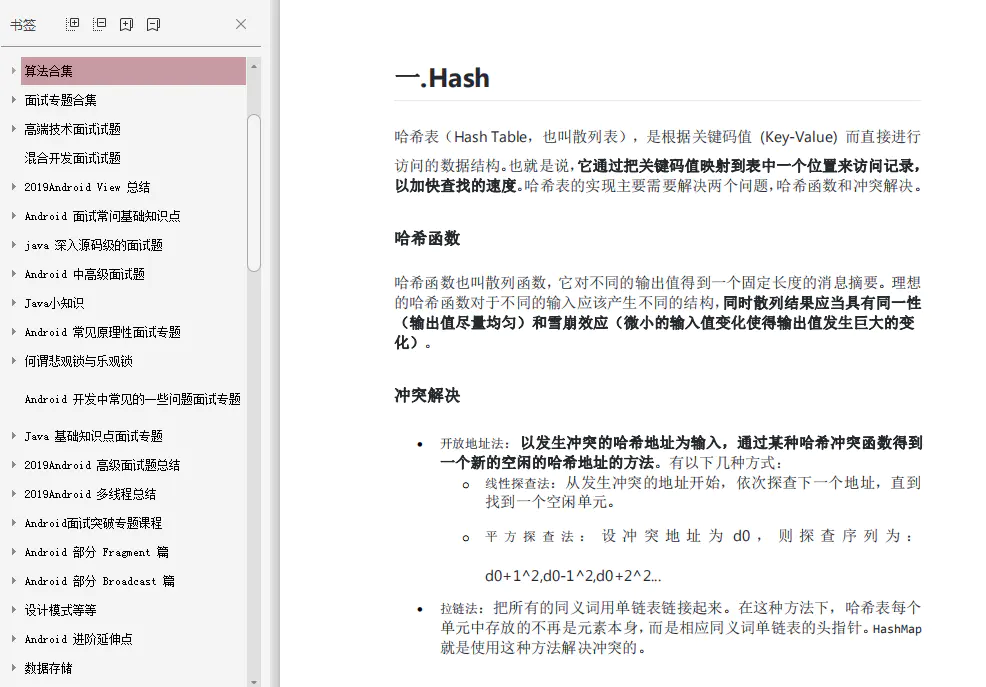

MOS晶体管的立体结构示意图如下:

一个管子可以看做是0和1的基本单元!

1.2、CMOS反相器

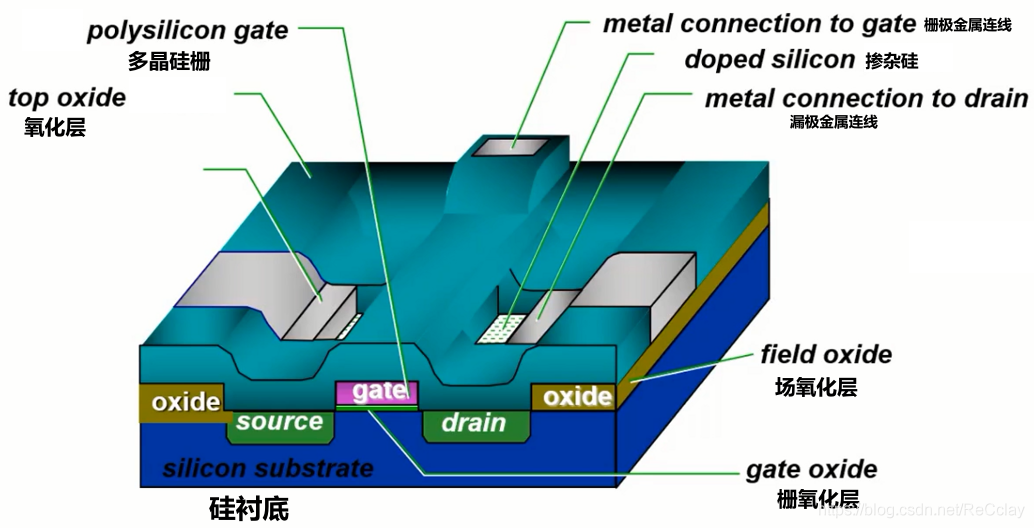

通常会把MOS管做成PMOS(P表示Positive)和NMOS(N表示Negative)两种类型,这两种管子是互补的,合起来称为CMOS(C表示Complementary,即互补)。

1.2.1、CMOS反相器组成

PMOS和NMOS会构成电路基本的逻辑单元,如下图所示是反相器的构造(需要重点掌握)。

- 若In输入0,NMOS的Gate是0,NMOS处于关闭状态;PMOS的Gate经过反相器(图中小圆圈)是1,PMOS处于打开状态;此时Out与PMOS的Source端状态一样,即Out被拉至VDD,输出1。

- 若In输入1,NMOS是打开状态,PMOS是关闭状态,Out与NMOS的Drain端状态一样,即Out被拉至GND,输出0。

- 综上,该逻辑实现的是一个反相器。

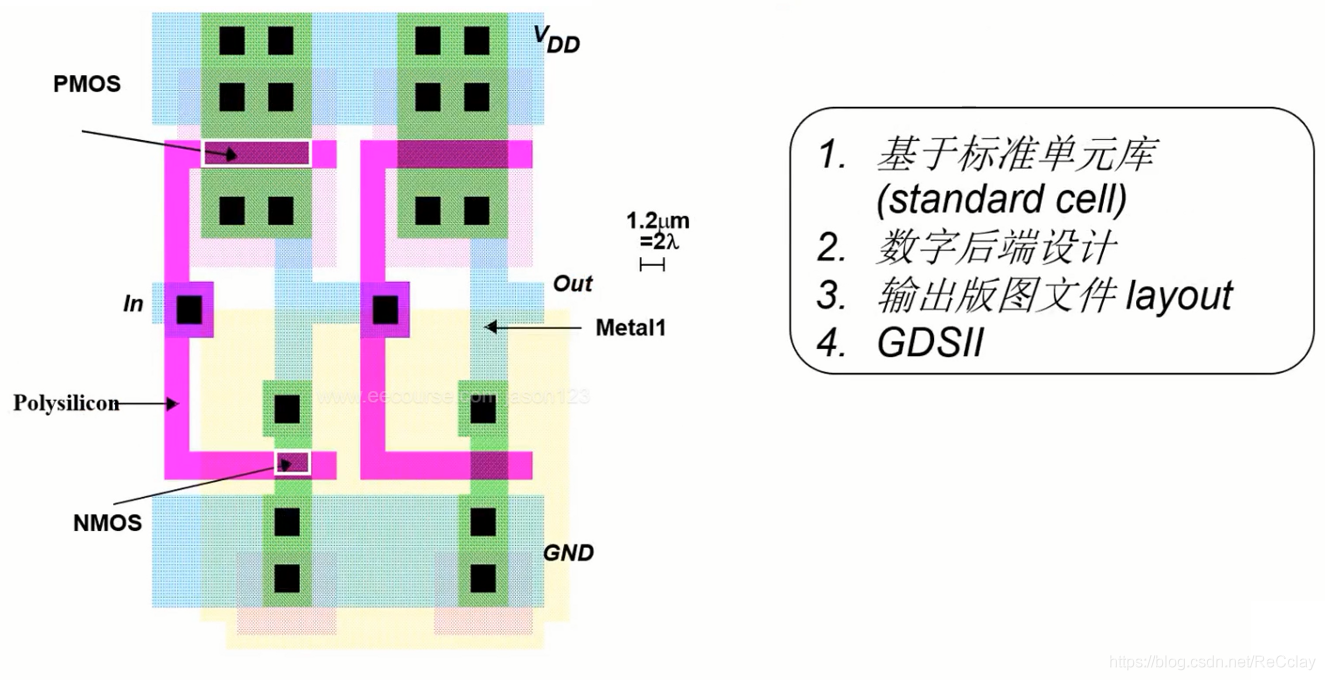

CMOS对应的标准单元(Standard Cell)工艺图(或称版图Layout),如下所示:

常见笔试题:PMOS管比NMOS管宽的原因是什么?

- 答:PMOS是空穴导电,NMOS管是电子导电,电子的迁移率约是空穴的2倍。

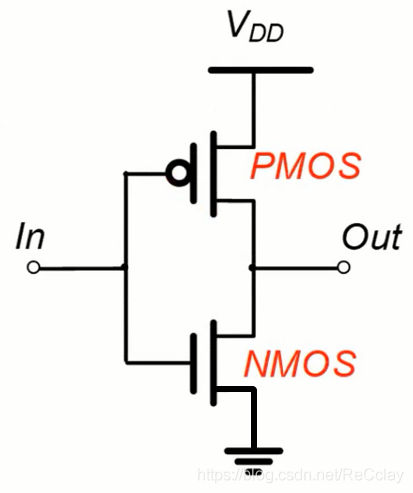

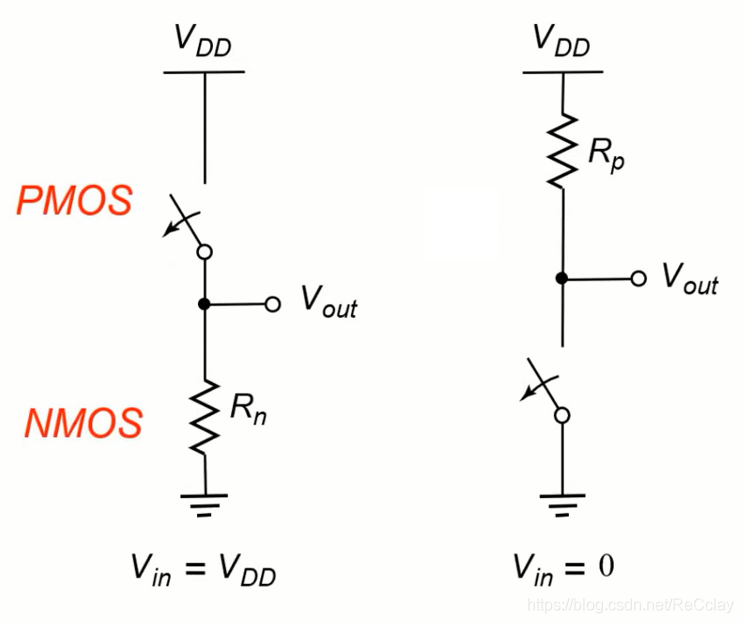

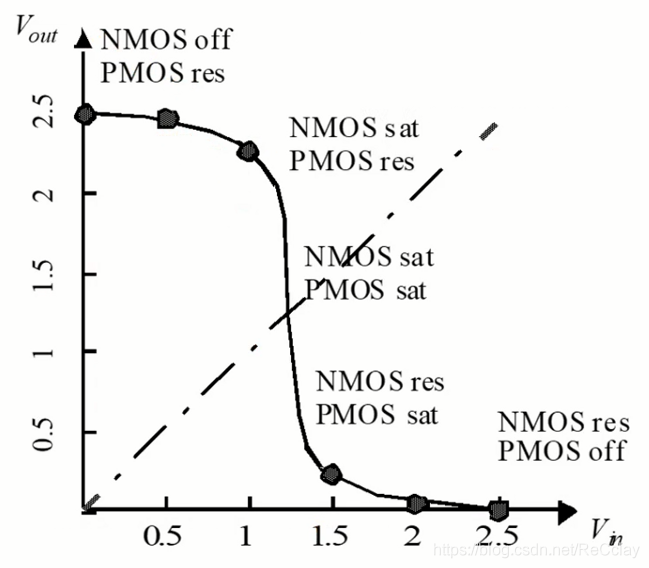

1.2.2、CMOS反相器一阶直流分析

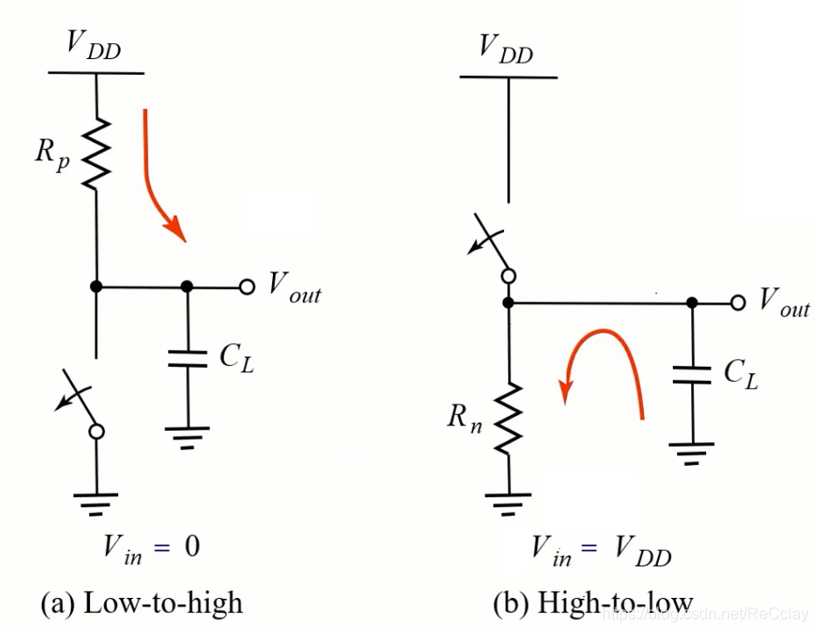

- 左侧:Vin = VDD,即输入为1,N管导通,P管断开,N管会有一个导通电阻。

- 右侧:Vin = 0,即输入为0,N管断开,P管导通,P管会有一个导通电阻。

1.2.3、CMOS反相器瞬态响应

不管是从1到0,还是从0到1,两个都有一个过渡时间,即transient time,并不是理想的垂直跳变。尽管如此,我们前端在做分析的时候还是按理想的垂直跳变进行分析。因为我们更多关注的是高层的逻辑功能,尽量不要与底层的工艺库选型牵扯到一起,这要是耦合在一起分析直接把人搞崩溃了。

transient time跟晶体管的工艺有关系,即跟

R

O

n

R_On

</span><span class="katex-html"><span class="base"><span class="strut" style="height: 0.83333em; vertical-align: -0.15em;"></span><span class="mord"><span class="mord mathdefault" style="margin-right: 0.00773em;">R</span><span class="msupsub"><span class="vlist-t vlist-t2"><span class="vlist-r"><span class="vlist" style="height: 0.328331em;"><span class="" style="top: -2.55em; margin-left: -0.00773em; margin-right: 0.05em;"><span class="pstrut" style="height: 2.7em;"></span><span class="sizing reset-size6 size3 mtight"><span class="mord mathdefault mtight" style="margin-right: 0.02778em;">O</span></span></span></span><span class="vlist-s"></span></span><span class="vlist-r"><span class="vlist" style="height: 0.15em;"><span class=""></span></span></span></span></span></span><span class="mord mathdefault">n</span></span></span></span></span>和<span class="katex--inline"><span class="katex"><span class="katex-mathml">

C

L

C_L

</span><span class="katex-html"><span class="base"><span class="strut" style="height: 0.83333em; vertical-align: -0.15em;"></span><span class="mord"><span class="mord mathdefault" style="margin-right: 0.07153em;">C</span><span class="msupsub"><span class="vlist-t vlist-t2"><span class="vlist-r"><span class="vlist" style="height: 0.328331em;"><span class="" style="top: -2.55em; margin-left: -0.07153em; margin-right: 0.05em;"><span class="pstrut" style="height: 2.7em;"></span><span class="sizing reset-size6 size3 mtight"><span class="mord mathdefault mtight">L</span></span></span></span><span class="vlist-s"></span></span><span class="vlist-r"><span class="vlist" style="height: 0.15em;"><span class=""></span></span></span></span></span></span></span></span></span></span>有关系。<span class="katex--inline"><span class="katex"><span class="katex-mathml">

V

o

u

t

V_out

</span><span class="katex-html"><span class="base"><span class="strut" style="height: 0.83333em; vertical-align: -0.15em;"></span><span class="mord"><span class="mord mathdefault" style="margin-right: 0.22222em;">V</span><span class="msupsub"><span class="vlist-t vlist-t2"><span class="vlist-r"><span class="vlist" style="height: 0.151392em;"><span class="" style="top: -2.55em; margin-left: -0.22222em; margin-right: 0.05em;"><span class="pstrut" style="height: 2.7em;"></span><span class="sizing reset-size6 size3 mtight"><span class="mord mathdefault mtight">o</span></span></span></span><span class="vlist-s"></span></span><span class="vlist-r"><span class="vlist" style="height: 0.15em;"><span class=""></span></span></span></span></span></span><span class="mord mathdefault">u</span><span class="mord mathdefault">t</span></span></span></span></span>到后面会去驱动很多的CELL,这些CELL简化下来就等效于一个电容模型。而管子本身也是有电阻的,故transient time跟所选的工艺(管子电阻)和输出负载(等效电容)有关系!</p>

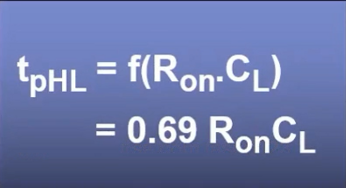

1.2.4、CMOS反相器的transient time

更接近实际的transient time(容抗效应)

一个简化版本的transient time

1.2.4、CMOS反相器小结

左侧是后端设计的一个版图,上面是一个PMOS连接到VDD,下面是一个NMOS连接到GND。

二、数字电路功耗

2.1、Dynamic Power Consumption 动态功耗

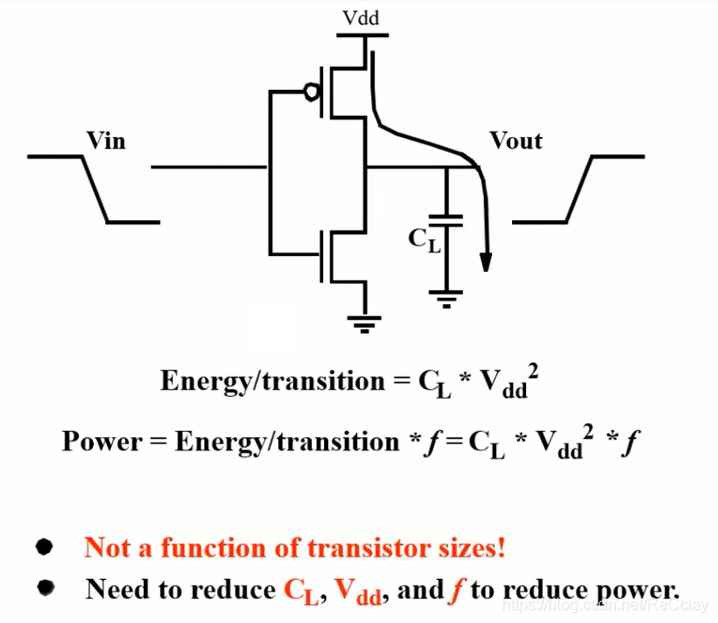

2.1.1、Charging and discharging capacitors 翻转功耗

管子的翻转,导致的管子的开和关形成的功耗!

- 升压可提高性能(CELL的延时会变短,transient 会变短,翻转频率可以跑的更高些),但同时功耗增加

- 温度升高时,功耗增加

- 从上述动态功耗公式可以看出,动态功耗和晶体管大小无关,和电压的平方成正比(

V d d 2 ) Vdd^2) </span><span class="katex-html"><span class="base"><span class="strut" style="height: 1.06411em; vertical-align: -0.25em;"></span><span class="mord mathdefault" style="margin-right: 0.22222em;">V</span><span class="mord mathdefault">d</span><span class="mord"><span class="mord mathdefault">d</span><span class="msupsub"><span class="vlist-t"><span class="vlist-r"><span class="vlist" style="height: 0.814108em;"><span class="" style="top: -3.063em; margin-right: 0.05em;"><span class="pstrut" style="height: 2.7em;"></span><span class="sizing reset-size6 size3 mtight"><span class="mord mtight">2</span></span></span></span></span></span></span></span><span class="mclose">)</span></span></span></span></span>),和翻转率成正比(<span class="katex--inline"><span class="katex"><span class="katex-mathml"> f f </span><span class="katex-html"><span class="base"><span class="strut" style="height: 0.88888em; vertical-align: -0.19444em;"></span><span class="mord mathdefault" style="margin-right: 0.10764em;">f</span></span></span></span></span>),和Vout接的负载有关系(<span class="katex--inline"><span class="katex"><span class="katex-mathml"> C L C_L </span><span class="katex-html"><span class="base"><span class="strut" style="height: 0.83333em; vertical-align: -0.15em;"></span><span class="mord"><span class="mord mathdefault" style="margin-right: 0.07153em;">C</span><span class="msupsub"><span class="vlist-t vlist-t2"><span class="vlist-r"><span class="vlist" style="height: 0.328331em;"><span class="" style="top: -2.55em; margin-left: -0.07153em; margin-right: 0.05em;"><span class="pstrut" style="height: 2.7em;"></span><span class="sizing reset-size6 size3 mtight"><span class="mord mathdefault mtight">L</span></span></span></span><span class="vlist-s"></span></span><span class="vlist-r"><span class="vlist" style="height: 0.15em;"><span class=""></span></span></span></span></span></span></span></span></span></span>)</li></ul>

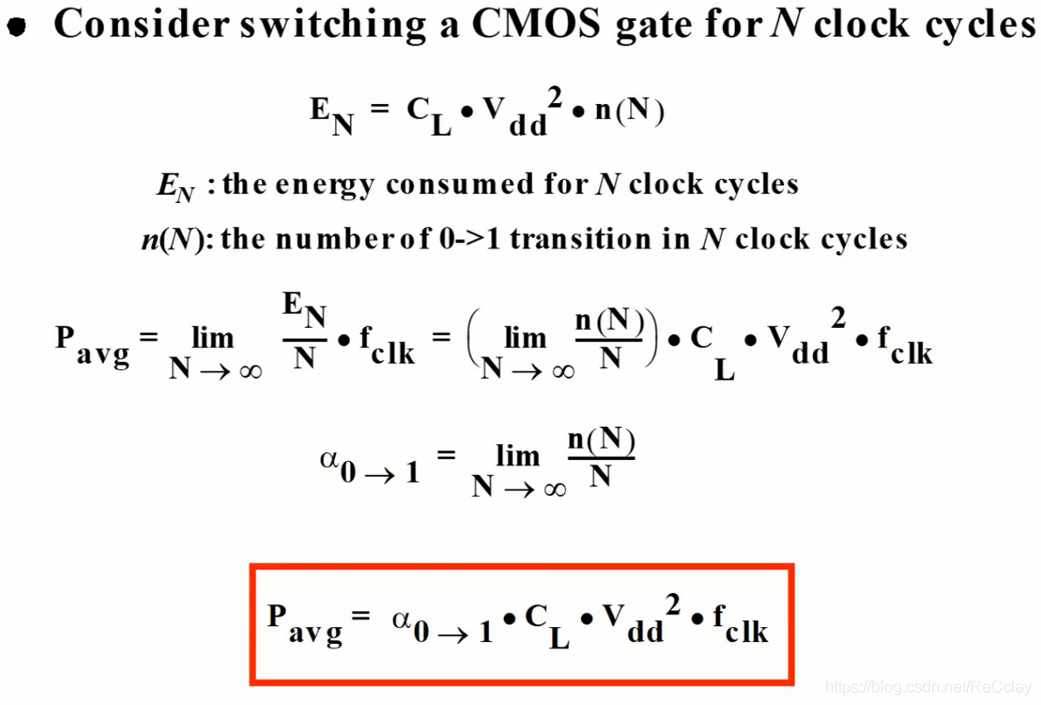

Node Transition Activity and power 节点转换活动和功率

- 做工程的话最终用的还是推导的结论,即上图中红色框住的部分。从结论不难得出,功耗的Average主要与电压的平方、跟时钟频率有关系。

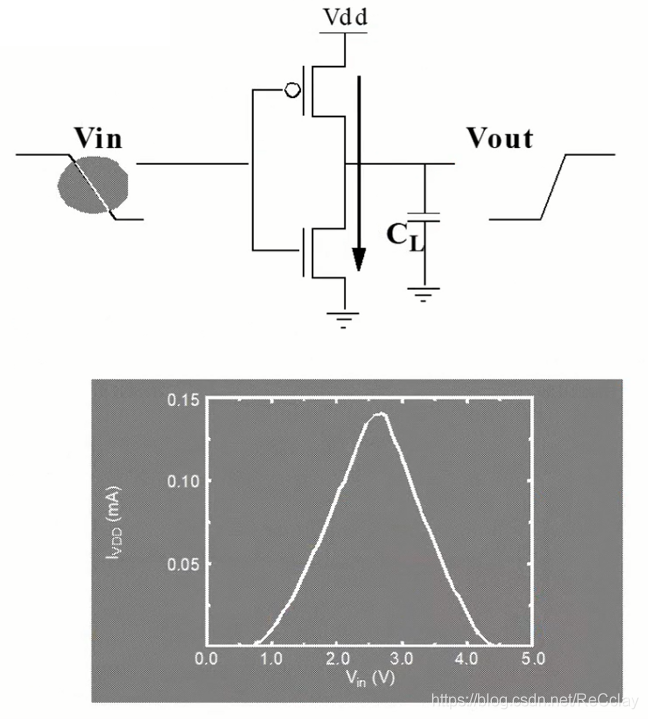

2.1.2、Short Circuit Currents 短路功耗

Short circuit path between supply rails during switching 开关导通瞬间的电源和地之间形成短路(eg:CMOS反相器两个管子同时导通的情形)

- 上图中的第二幅图,假设电压Vdd是5V,当电压是2.5V左右时,短路电流达到最大!

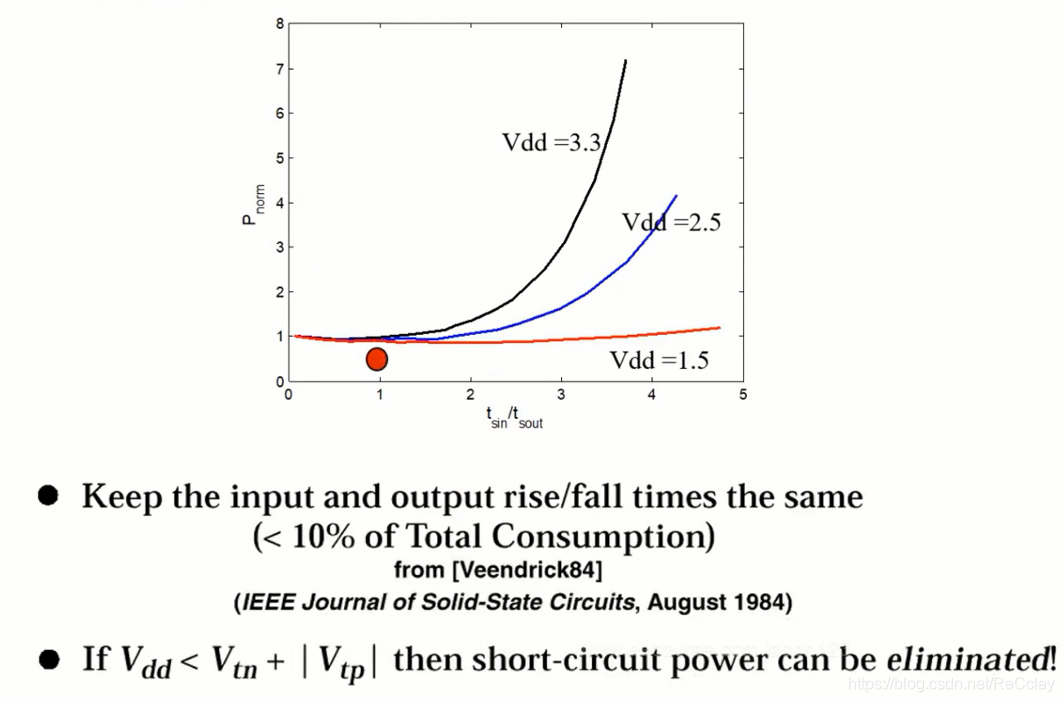

Minimizing Short-Circuit Power 最小化短路功耗

- 从上图不难看出,电源电压Vdd是决定短路功耗的一个重要因素。

2.2、Static Power Consumption 静态功耗

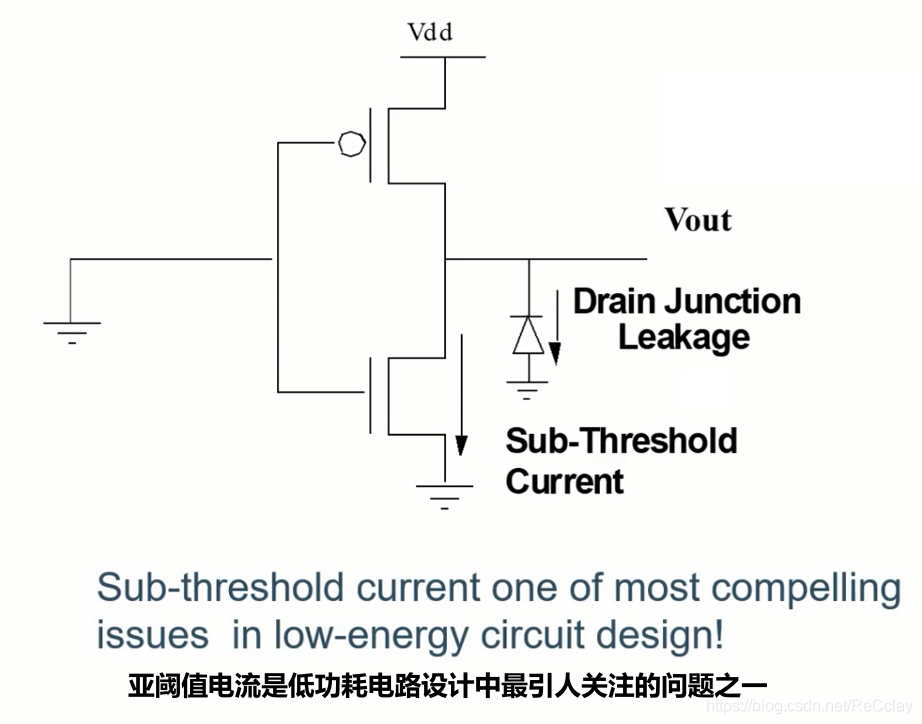

2.2.1、Leakage 漏电功耗

Leaking diodes and transistors 二极管和晶体管漏电(与地之间形成通路,不过电流很小)

- 器件本身的原因必然会产生漏电电流

- 要解决漏电功耗是把它的Sub-Threshold做一些变化,供应商会提供多种不同的库,不同的库Sub-Threshold不一样。Sub-Threshold高,频率会高一些,延时会短一些,对应的漏电功耗就越大。

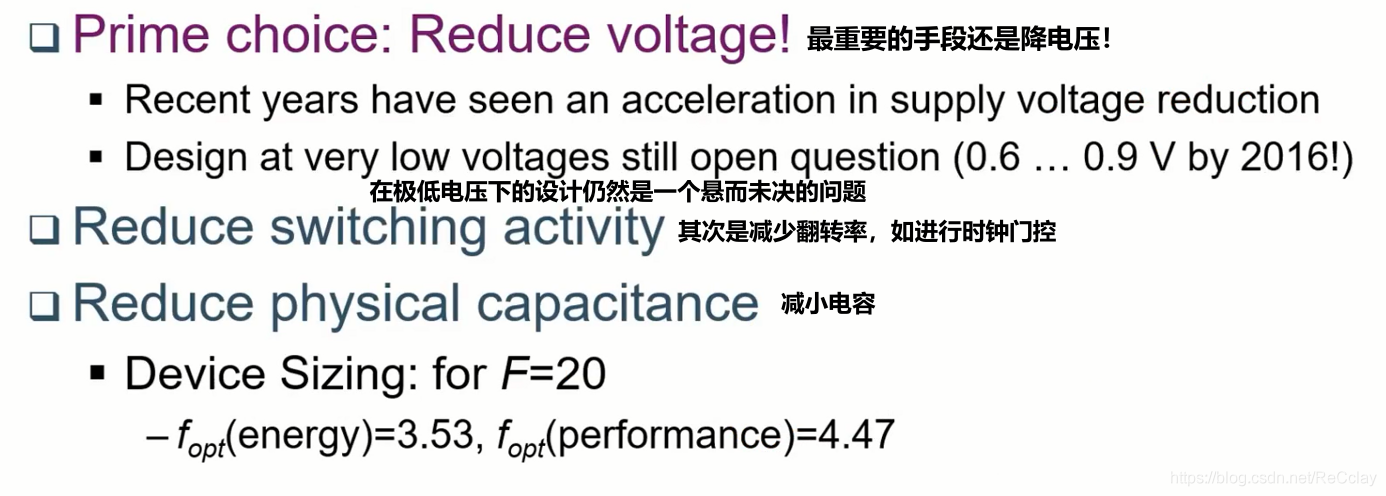

2.3、Principles for Power Reduction 降低功耗的原则

- 降功耗最主要的是降电压,其次是减少反转率(如进行时钟门控),最后是减少电容!

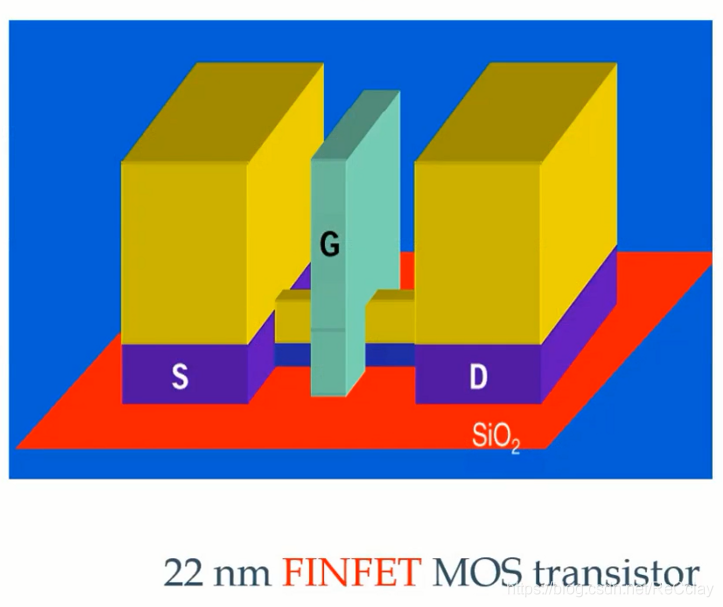

三、摩尔定律:22nm FinFET工艺

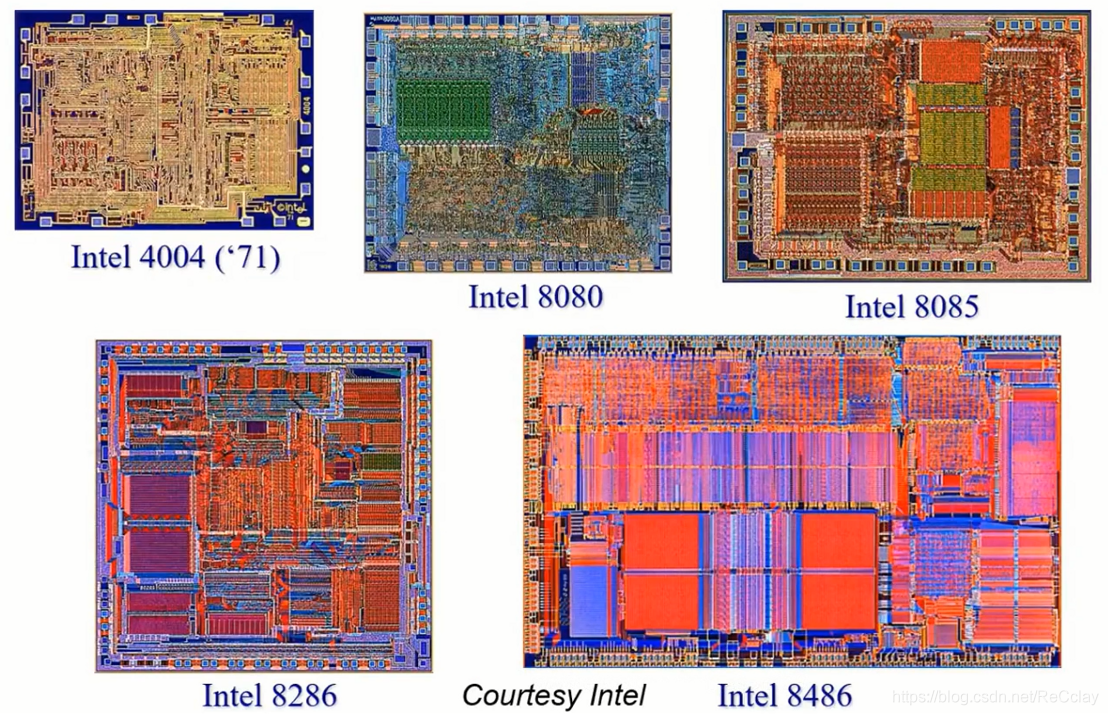

摩尔定律:当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。

3.1、3D MOS 晶体管 22nm

- FINFET(鳍式晶体管)的结构是类似鱼翅一样的东西,是加州大学胡正明教授带领团队发明的,主要为突破芯片25nm进程,解决mosFET由于制程缩小伴随的隧穿效应。

四、组合电路和时序电路

上面介绍了基本的标准单元内部结构,包括实现基本逻辑的原理,以及它的电气特性,包括它的容抗阻抗特性,也介绍了一下功耗相关的内容,最后介绍了业界有名的摩尔定律。下面要学习的是数字中的逻辑,跟上述电气特性的相关性并不是很大。电气特性更多的是在后端物理实现上去考虑的(eg:容抗效应导致从0到1跳变需要一定的时间,跳变会引起管子的翻转会引起功耗),而数字验证更多的需要了解前端的逻辑(eg:纯粹的0到1跳变,不会有中间的跳变过程)!

4.1、数字组合电路逻辑器件:与门、或门、非门

组合电路的意思就是输出是及时响应的,当前时刻的输出只与当前输入有关系,与之前输入无关!组合逻辑实现的电路叫组合电路。

组合电路的缺陷:组合逻辑由于走线延迟的差异可能会产生毛刺,这种现象叫竞争,产生的结果叫做冒险。为了解决这个问题,于是就引出了时序逻辑(把时间点分成一个个时钟周期,按照时钟周期去采集数据,在稳定的状态采的数据。)

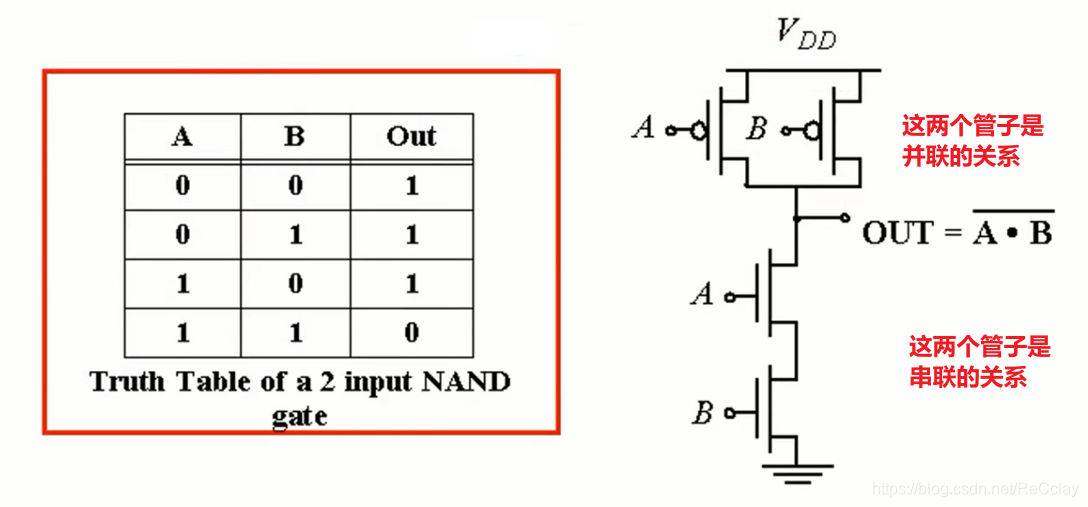

4.1.1、组合电路(门级电路):与非门 NAND

- 逻辑最基本的东西叫真值表(Truth table):把逻辑信号代表的逻辑范围值全部遍历。有n位的话就有2的n次方种状态

- 真值表中,1位叫做1个bit,在逻辑里面用的是一个二进制的方式。用cmos管来搭我们的电路。一个CMOS管的输入只能代表一位或者一个bit,只有两种状态0或1,即管子的开和关,正好和数学中的二进制匹配上。有几位就有2的几次方种状态。

- 与非(在与的基础上取非):A和B都为1,out才是0

常见笔试题:使用与非门设计一个电路,画出CMOS的电路图!

- 答:上图的右边那个图。

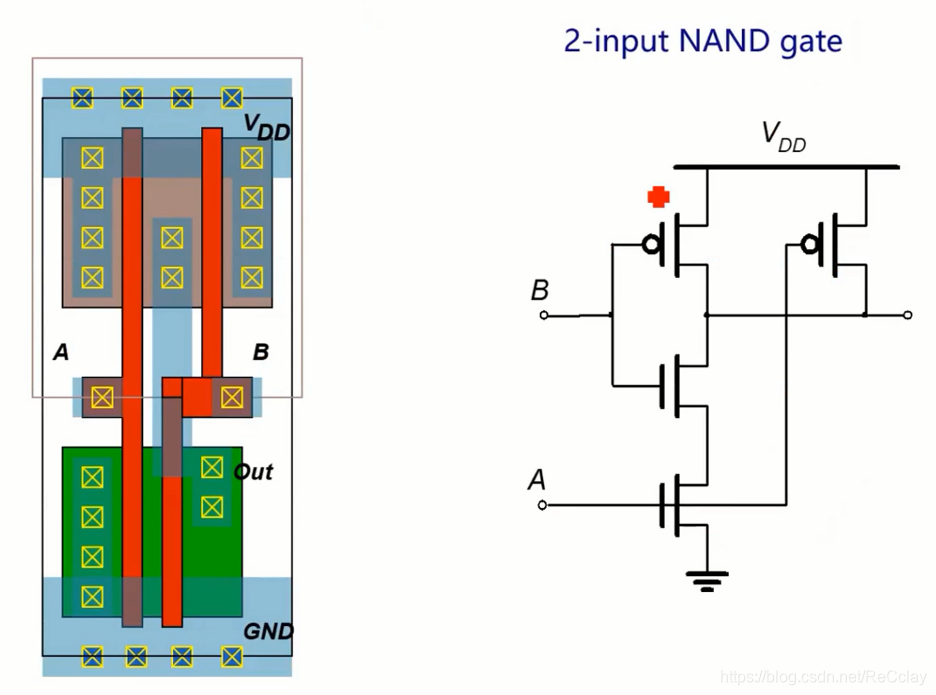

与非门(NAND)对应的标准单元(Standard Cells)

- 上图的右侧电路图是工业界实现的电路图,原理与之前的电路图一样,只不过把两个A/B的输入接到了一起。

- 左侧是版图Layout!

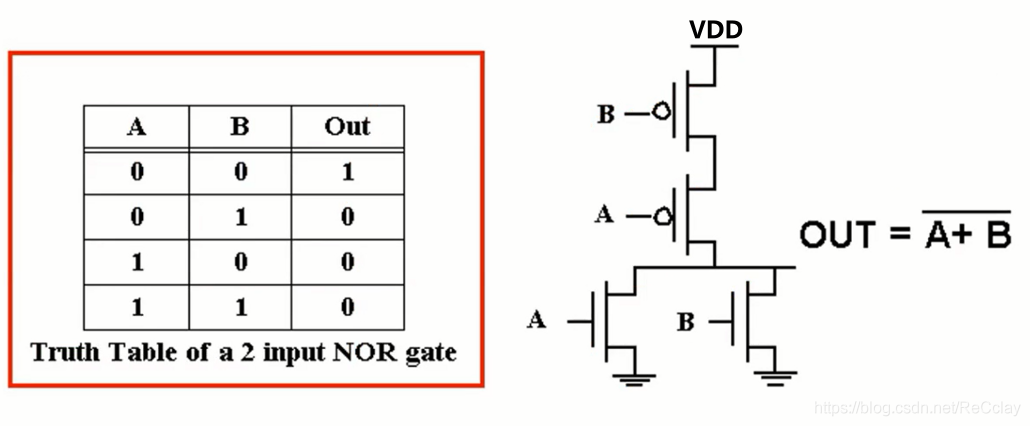

4.1.2、组合电路(门级电路):或非门 NOR

- 或非(在或的基础上取非):A和B都为0,out才是1

4.2、数字时序电路逻辑器件:寄存器、锁存器

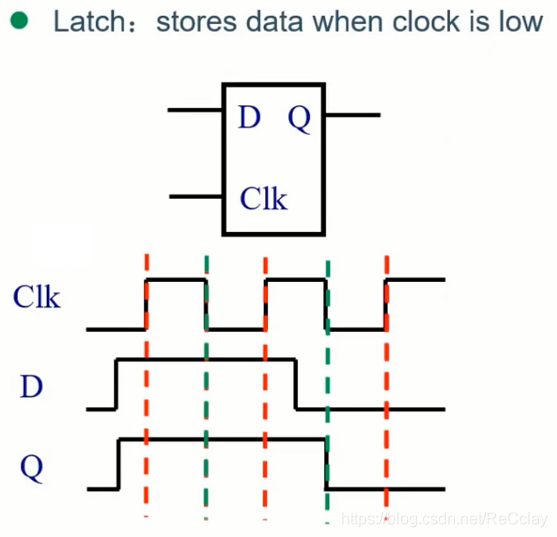

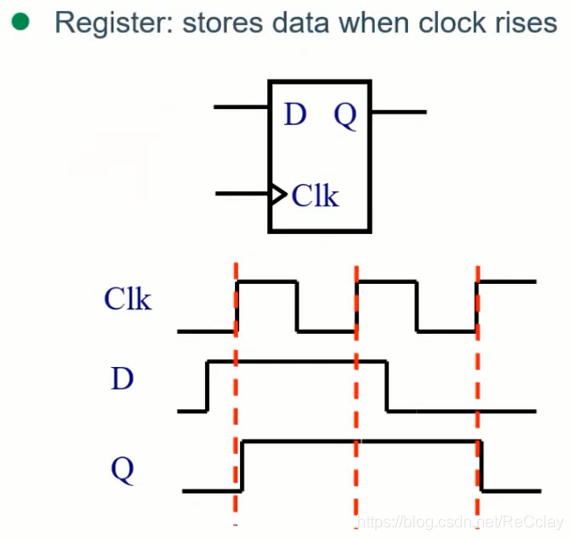

- Latch:锁存器是电平敏感器件

- Register:寄存器是边沿触发敏感器件

- Flip-Flop:触发器类似寄存器

- 时序电路少不了时钟clk,时钟采集数据分为两种:Latch 和 Register。Register是用的最多的,用的是时钟的上升沿去采(0->1的叫上升沿,1->0的叫下降沿)。

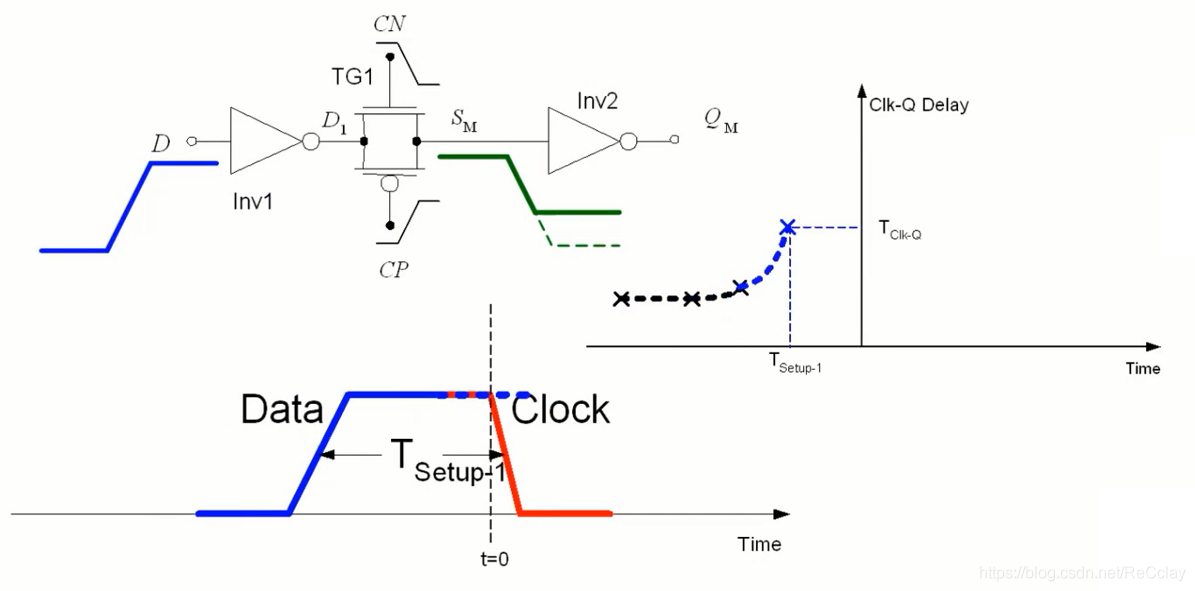

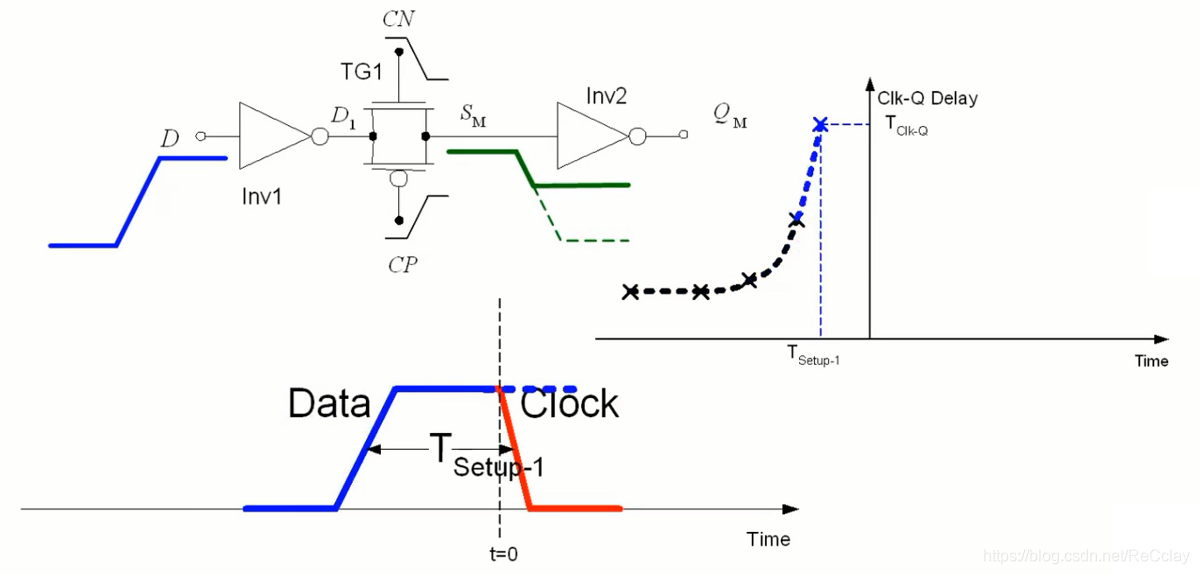

- 用时钟的上升沿去采,会一直保持住上一个点采集的数据,这也是时序电路的特点。这里要求输入D是不能有一个沿到沿的变化的,因为Clk也是上沿采集,由此引出了setup的概念,即建立时间,相当于时钟上沿之前的数据要保持稳定。

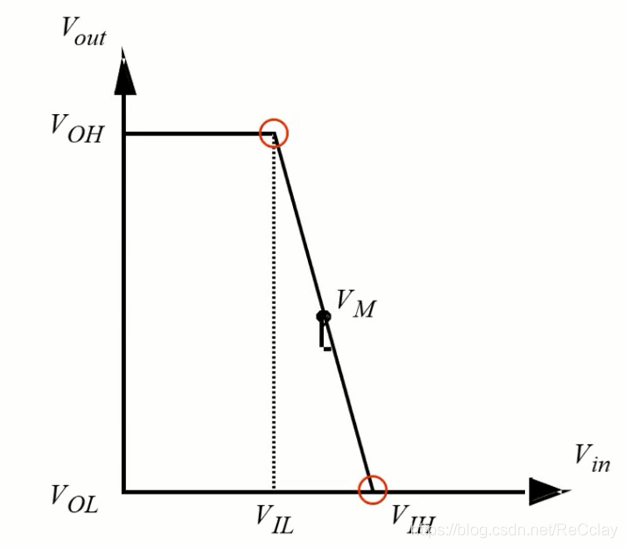

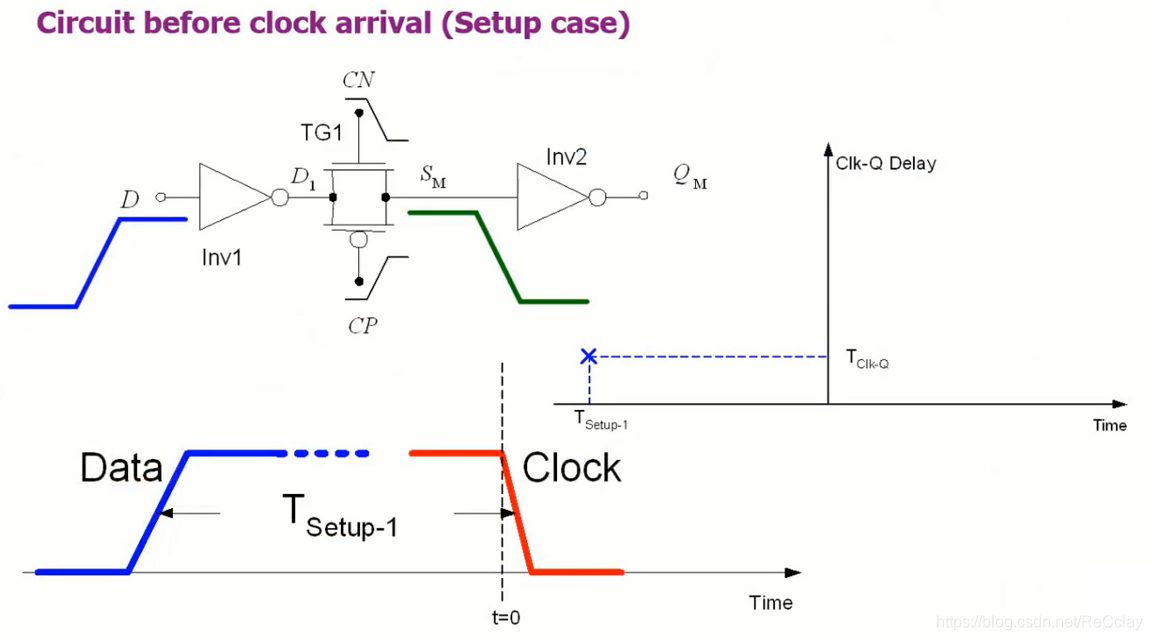

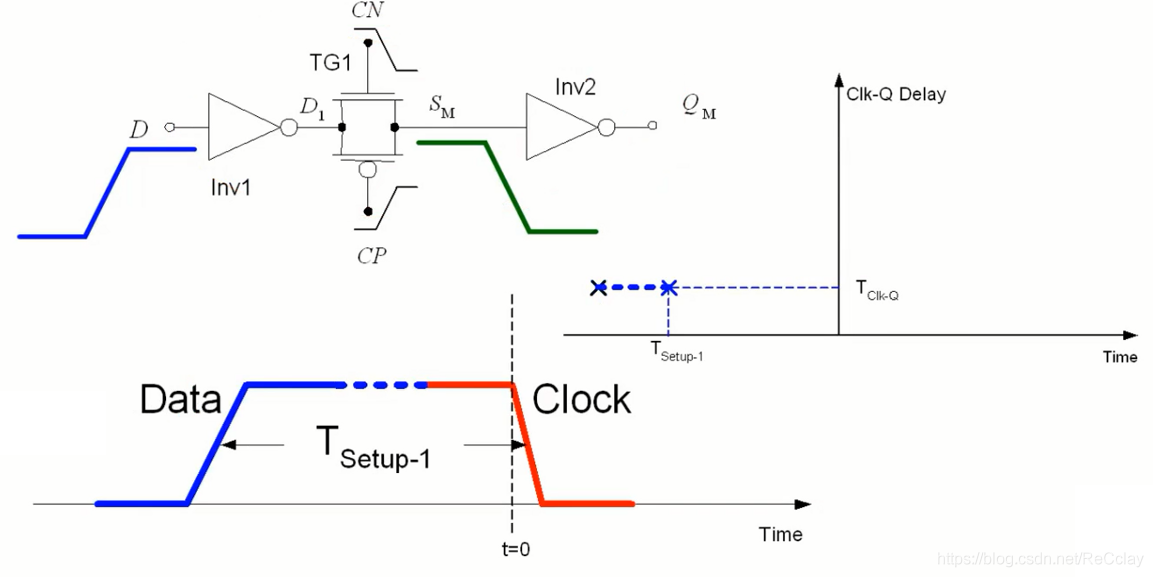

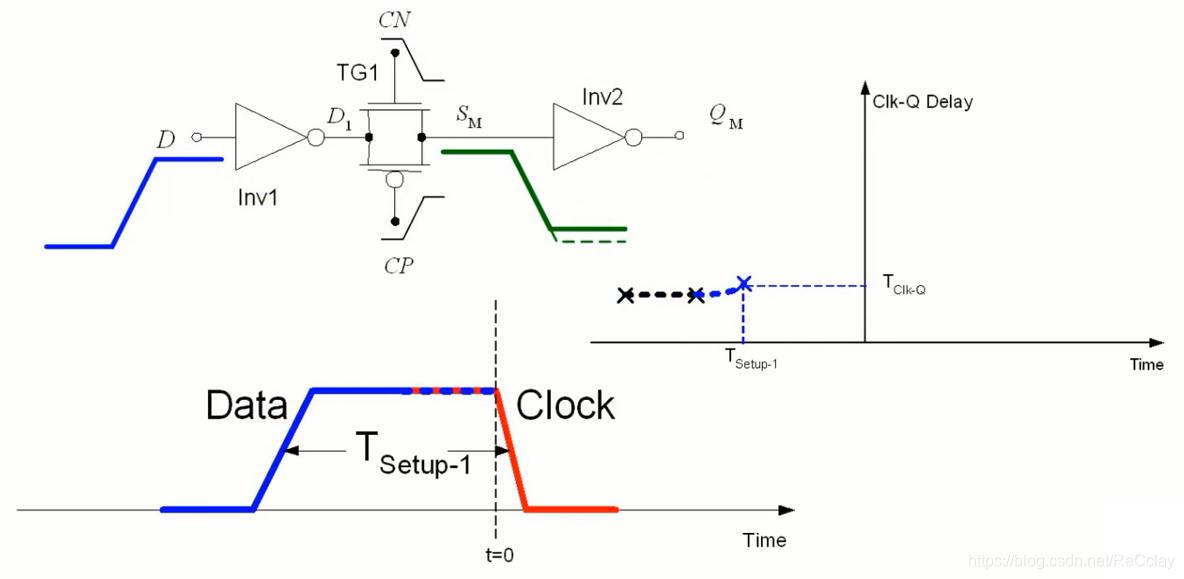

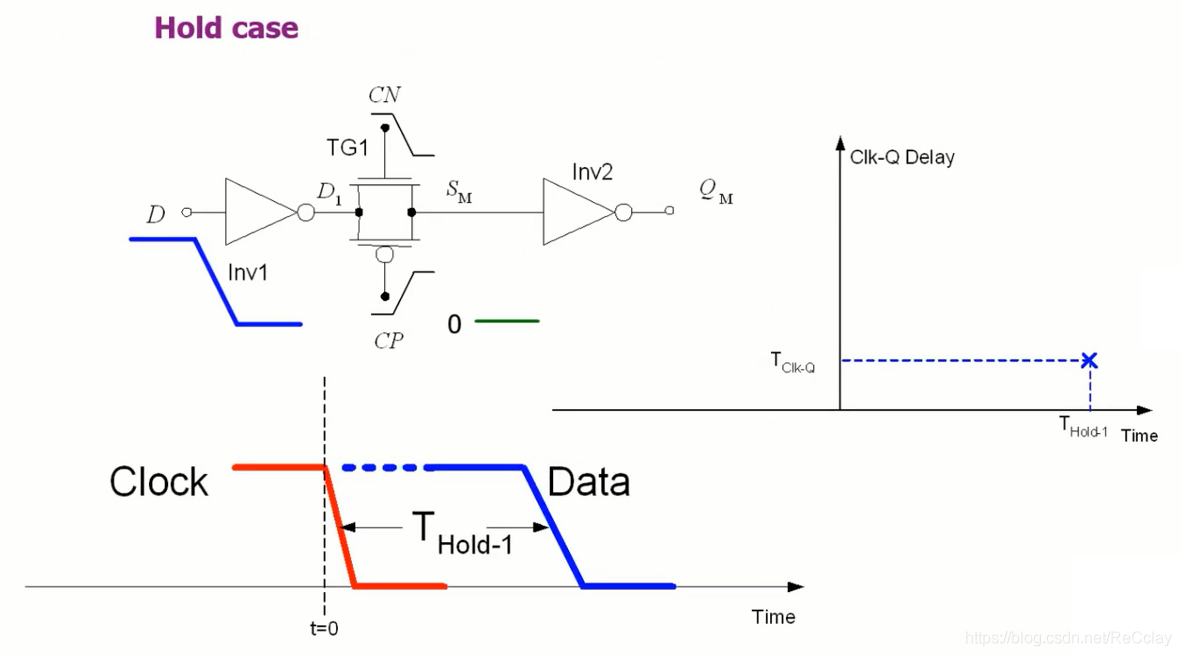

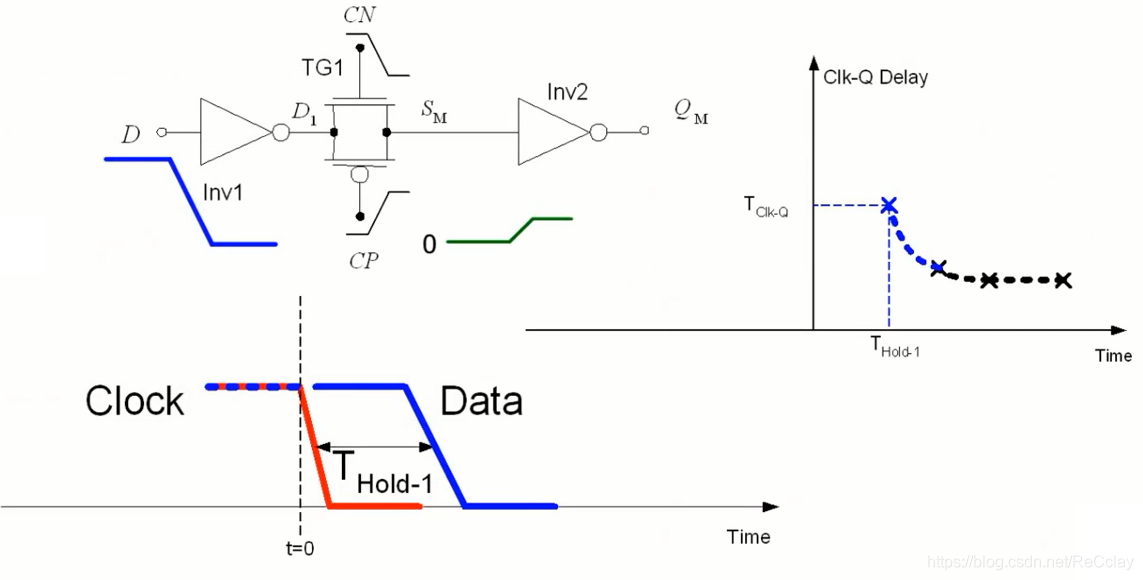

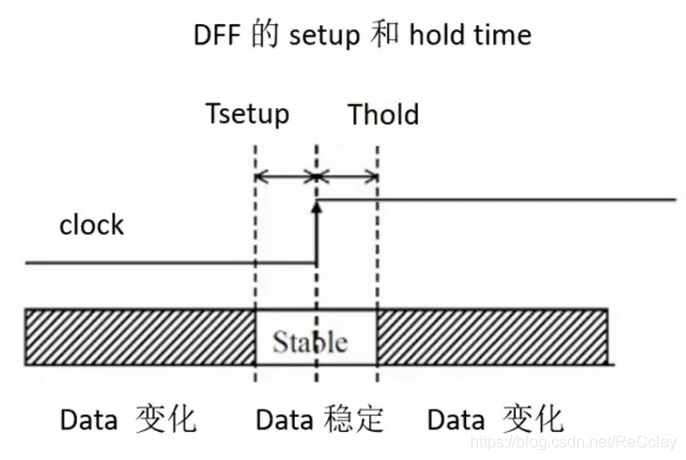

4.2.1、Setup/Hold Time illustrations 建立/保持时间图示

- 建立时间:时钟的上升沿到来之前,数据要保持稳定的时间!

- 保持时间:时钟的上升沿到来之后,数据要保持稳定的时间!

常见面试题:电路为什么需要触发器这种结构?

- 答:用触发器是因为触发器能保存数据,保存电路状态;触发器是在时钟边沿触发,用时钟同步是让整个电路能同步整齐划一的工作;乘法器的计算部分是组合逻辑,不需要触发器,计算后的结果可以用触发器保存起来。

常见面试题:什么是建立时间、保持时间,如果setup time violation (建立时间不满足)或者 hold time violation (保持时间不满足 )应该怎么做?

- 答:建立时间:是指在触发器的时钟信号采样边沿到来之前,数据保持稳定不变的事件;保持时间:是指在触发器的时钟信号采样边沿道来之后,数据保持不变的事件。

- 数据建立时间和保持时间

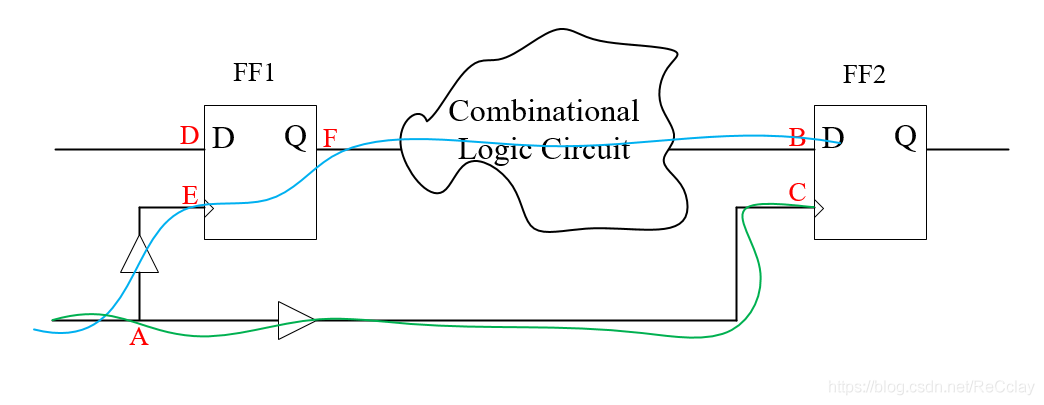

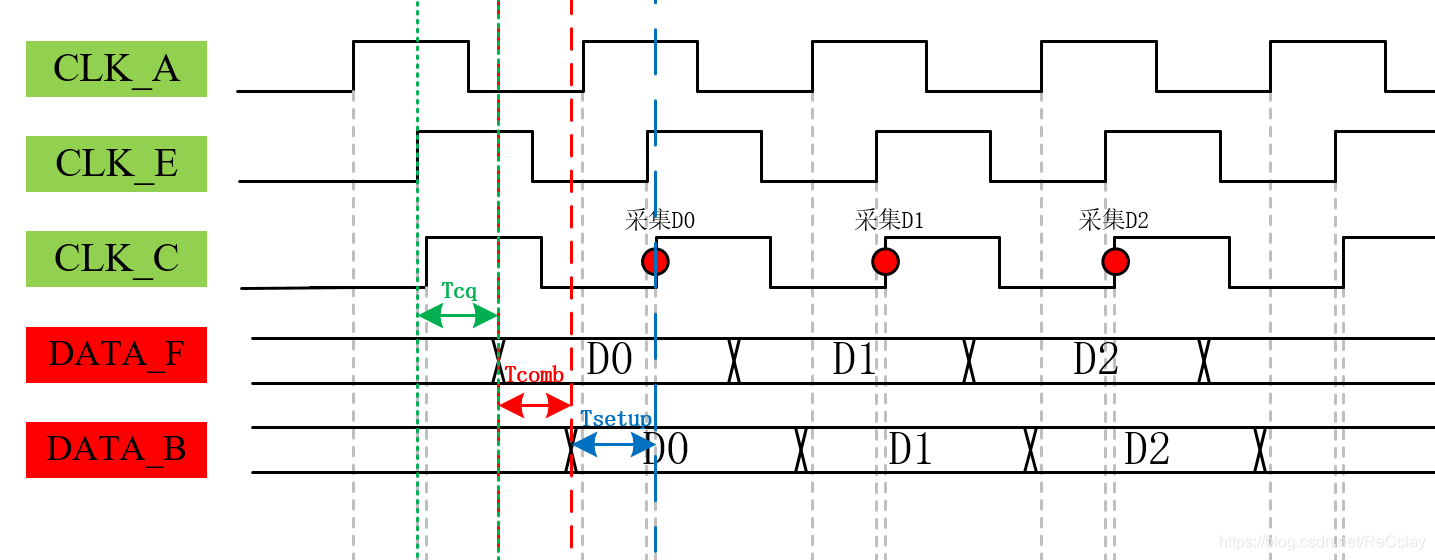

- 上图中的蓝色线是数据路径,绿色线是时钟路径,两者源头一样。

- 上图是典型的时序分析模型,在该模型中,主要分析FF2的数据输入(B点)和时钟输入(点C),看两者到达的关系,是否满足Setup/Hold时间。

- 两个D触发器的时钟源头,都是A点。在时钟线上有一些BUFFER,是为了做时钟树平衡,尽量使A点时钟到达E点和C点的相位一样,两者之间的差值:|Tea - Tca| = Tskew。

- 我们要比的是FF2数据的相位(B点)和CLK相位(C点)关系

- B点数据的相位又和E点CLK相位有关系。

- 从D点进入的数据从F点出来,F点出来的数据跟E点的CLK之间又有一定的延时,我们称之为Tcq(Time Clk to Q)。

- 数据从F点出来到B点,之间会经过一段组合逻辑,这个组合逻辑也有一定的延时,我们称之为Tcomb(Time Combinational),这个组合逻辑延时包含两部分:器件延时(与或非门)和线延时。

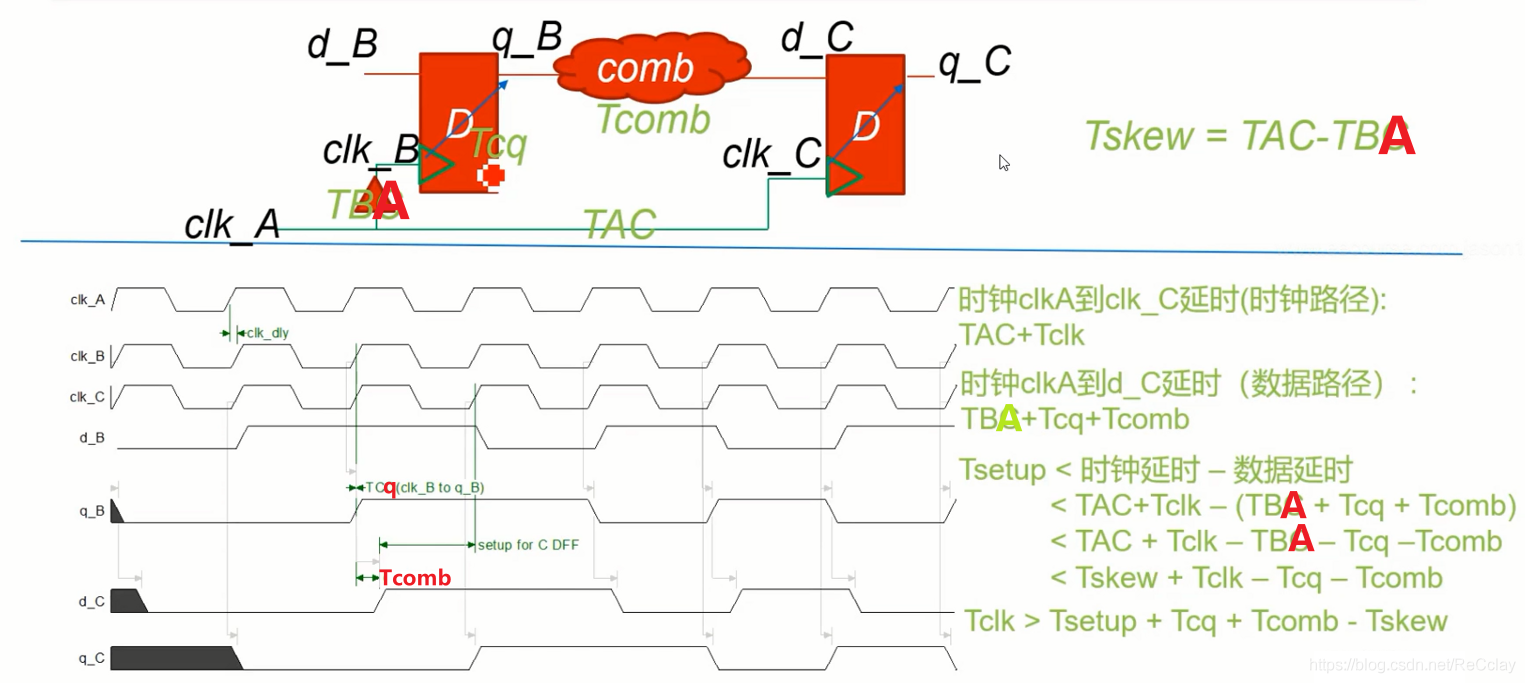

Setup time violation:

- 建立时间在静态时序分析时必须满足以下条件

- Tsetup < 时钟延时 - 数据延时 = (Tclk + Tca) - (Tea + Tcq + Tcomb) = Tclk + Tskew - Tcq - Tcomb

- 时钟延时路径为什么有Tclk?CLK_E的上升沿把数据打出去,只能在CLK_C的下一个沿采集数据,即在Tclk+Tskew采集数据!

- 如果setup time violation,则上述公式不成立

Setup time violation solution:调整上述公式中的变量:Tclk、Tcomb、Tskew

- 增大Tclk

- 降低数字系统的工作频率

- 减少Tcomb【实际工程中用的最多】

- 从数字逻辑功能设计的角度看(前端)

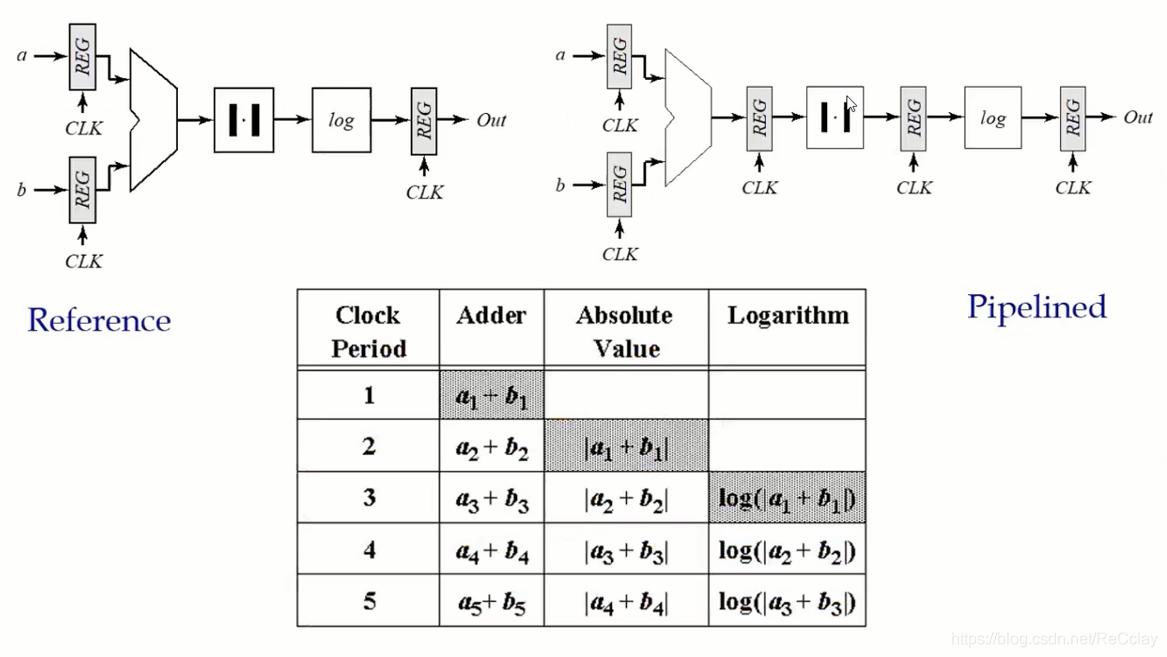

- 在组合电路之间插入寄存器,增加流水线(pipeline)【实际工程中用的多】

- 增加流水的负面效应是整个处理的延时增大。

- 在不改变逻辑功能的前提下,对组合逻辑电路进行优化【实际工程中用的多】

- 减少扇出(fanout)或负载

- 在组合电路之间插入寄存器,增加流水线(pipeline)【实际工程中用的多】

- 从数字物理版图实现的角度看(后端)

- 更换速度更快的标准单元(HVT-High Vlotage Threshold,SVT-Standard Voltage Threshold,LVT-Low Voltage Threshold),但是与之对应的功耗也会增加,需要做Tradeoff!

- 更换驱动能力更强的标准单元(X2,X4)

- 更换阻值更低的金属层以减少标准单元电路的负载和金属线网延迟

- 增加Tskew【工程上用的少,容易破坏时钟树】

- 在时钟路径上,插入Buffer,增加时钟路径的延迟,但是不能影响Hold Timing

- 从数字逻辑功能设计的角度看(前端)

- 增大Tclk

Hold time violation(跟时钟周期没关系)

- 保持时间在静态时序分析时必须满足以下条件:

- Thold < 数据延时 - Tskew = Tcq + Tcomb - Tskew

- 如果hold time violation,则上述公式不成立

Hold time Violation solution

- 增大Tcomb

- 在组合电路的数据传输路径上,插入延迟单元(buffer),增加组合逻辑延迟;但是当组合逻辑延时增加时,setup time可能会出现违例。这时候就需要做平衡(Balance)。由此可以看出setup和hold time是相互制约的。

- 减小Tskew

- 时钟树调整,做好Clock tree balance,hold就容易收敛。因为hold time与时钟周期没有关系!

- 增大Tcomb

总结

- 建立时间:是指在触发器的时钟信号采样边沿到来之前,数据保持稳定不变的事件;保持时间:是指在触发器的时钟信号采样边沿道来之后,数据保持不变的事件。

- setup和hold是相互制约的,修复hold后,setup的余量就会变小或者变成负值。因此时钟频率越高,setup和hold相互制约越严重,甚至会出现修复setup之后,hold就会违例;或者修复hold之后,setup就会违例的现象。

常见面试题:为什么触发器会存在setup和hold time 的要求?

- 答:设计触发器时,需要注意触发器的几个时间特性,满足这些特性触发器才能正常工作。

常见面试题:当setup和hold time violation发生时,会导致什么后果?

- 答:时钟沿采集数据采不准,会导致逻辑设置不稳定,产生亚稳态。因为本来就只是表示0和1。

常见面试题:什么是亚稳态?如何在异步电路设计中解决亚稳态的问题?

- 答:电路里面的状态不是0就是1,通常结果都是确定的,如果发生violation,那么结果是0或者1就会不确定,这种状态就叫亚稳态。即亚稳态: 采沿的时候可能采到0或者1的这种不确定的状态。

- 解决亚稳态的方法:在单个电路中可以打多拍,来减少亚稳态的概率,并不是完全彻底的消灭亚稳态。

- setup和hold 在同步电路里面可以通过工具去约束,从而让时序满足。因为没办法在异步电路中去建立时钟路径,所以没法在异步电路中约束,可能就会出现violation,就会出现亚稳态。

4.2.2、流水线技术(pipeline)

组合逻辑过长,会导致Tsetup不满足,这时候可能会去减少组合逻辑,办法是通过加入入流水线(插入D触发器)!

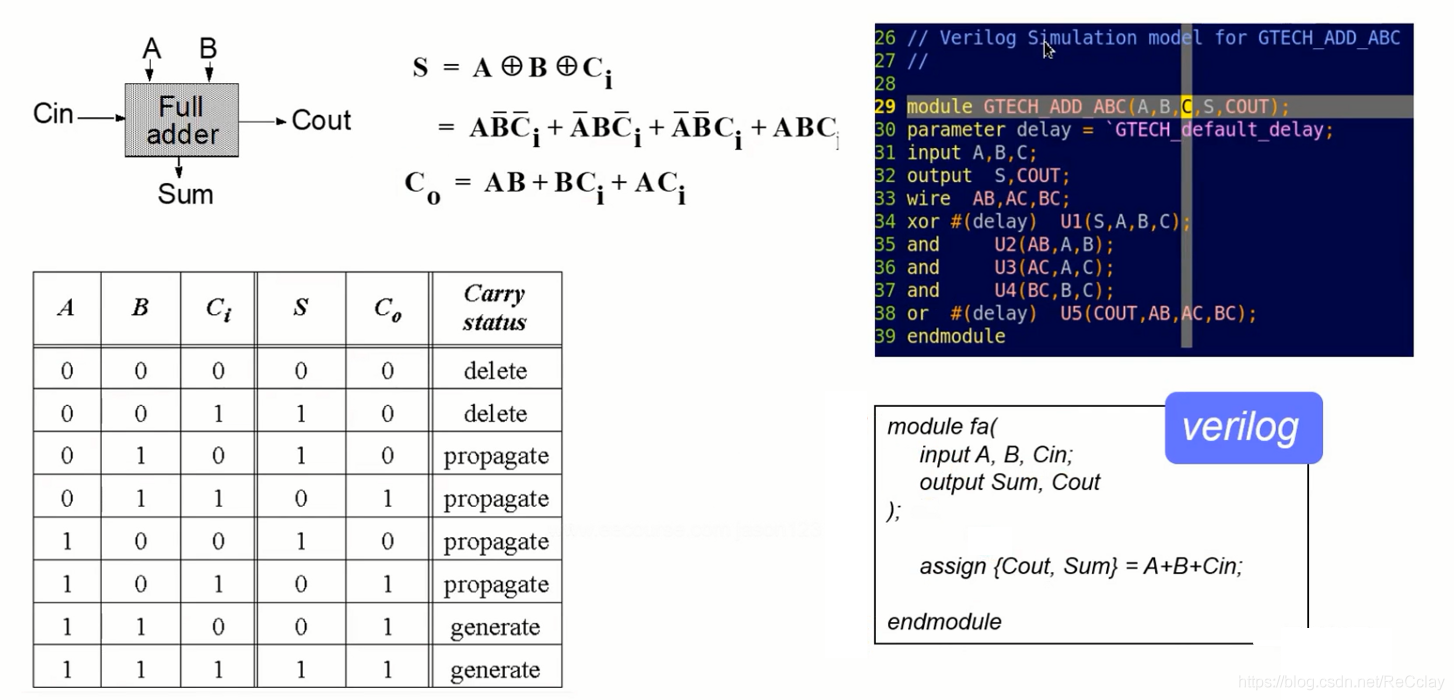

4.3、全加器

- 要求:能画出真值表,布尔代数也记下来。笔试的时候用的多。实际中直接用verilog直接代码写了。

- 半加器和全加器的区别在于有无cin,没有就是半加器

- 上图的右上角代码是Verilog综合后生成的!

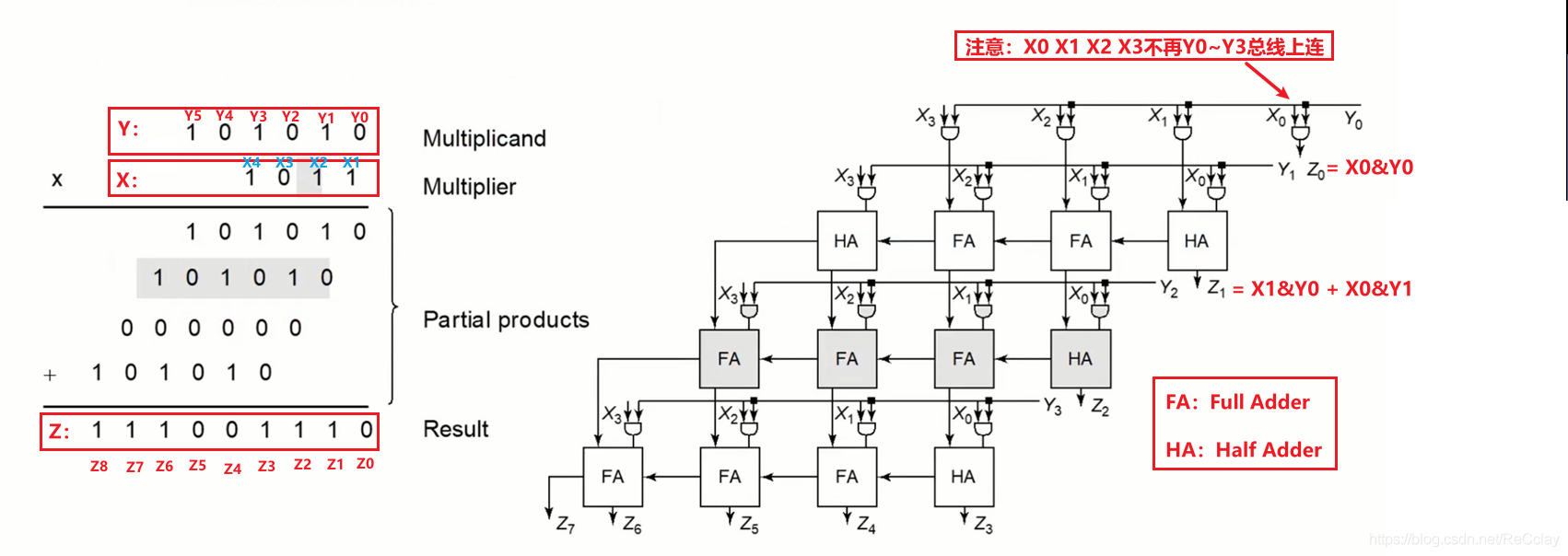

4.4、乘法器

- 乘法器也可以由基本的与或非门(CMOS电路)构成。

4.5、工业界如何实现算数逻辑单元

如何表述(设计)数字算数逻辑单元?

- HDL(硬件描述语言Hardware Description Language):Verilog/VHDL/SystemVerilog

- 加法器(+),乘法器(*)

如何将数字算数逻辑单元的描述代码转化为可以生成的文件?

- 逻辑综合技术:HDL转换为Netlist(MAP成Standard Cell的输出)(门级网表)

- 物理版图设计(Place Route 布局布线,简称PR):Netlist转化为GDSII(可用于生成的版图文件)

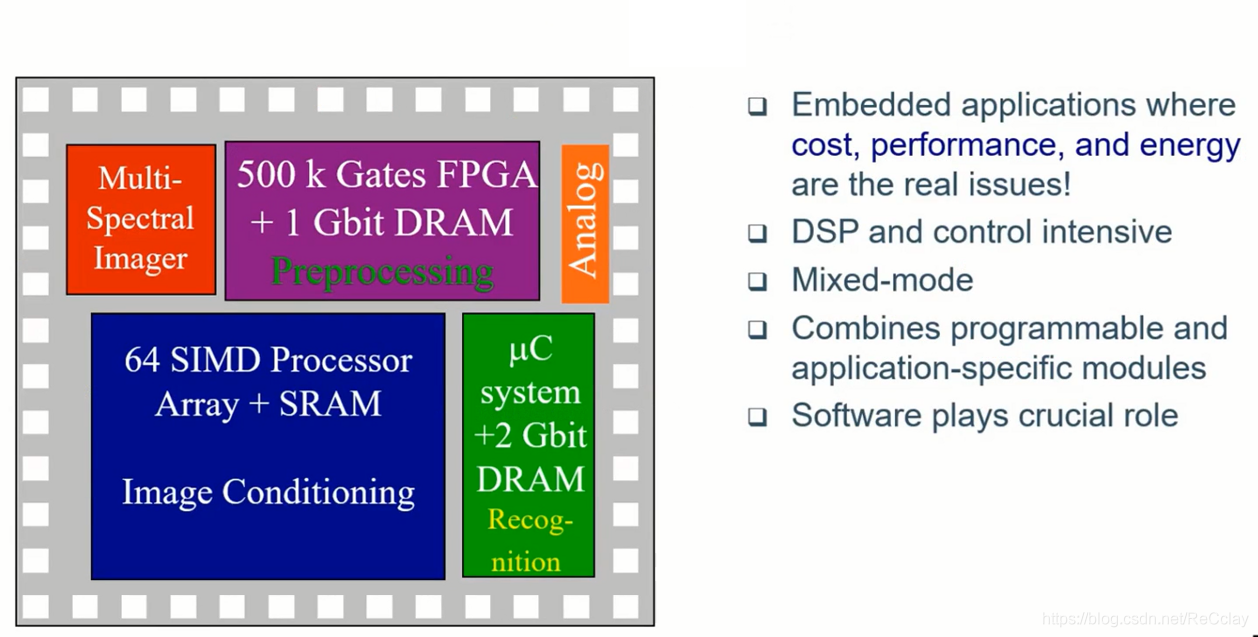

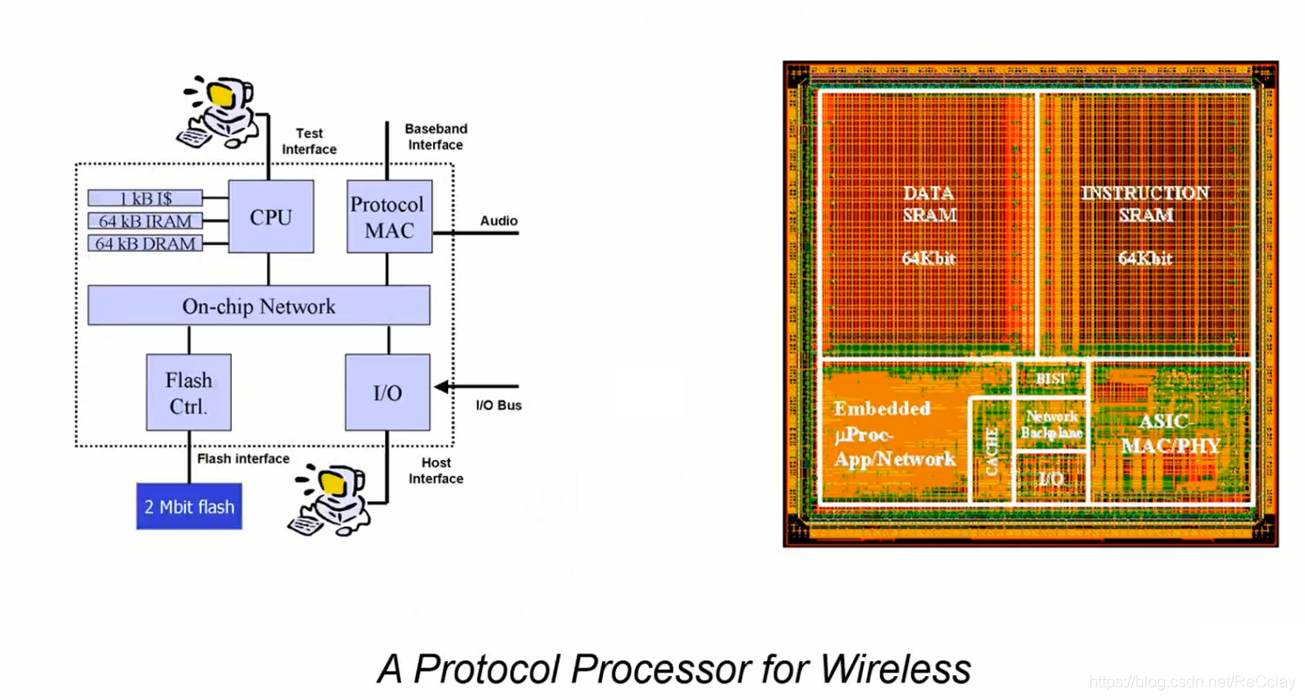

4.6、Design at a corssroad System-on-Chip

- 随着集成度的提高,我们把系统集成在芯片里面,简称SoC

4.7、IP - Intellectual Property

- 芯片里面会集成很多的IP,IP是实现不同的模块

4.8、VLSI超大规模集成电路自动布局布线

- 颜色很多,说明层数很多

五、数字电路数值表示

5.1、数字电路的数制

二进制:binary

- 0(低电平),1(高电平)

- 1’b0,1’b1

八进制:octonary

- 1’o0,1’o1,1’o2,1’o3,1’o4,1’o5,1’o6,1’o7

- 0~7

十进制:decimal

- 1’d0,1’d1,1’d2,1’d3,1’d4,1’d5,1’d6,1’d7,1’d8,1’d9

- 0~9

十六进制:Hexadecimal

- 1’h0,1’h1,1’h2,1’h3,1’h4,1’h5,1’h6,1’h7,1’h8,1’h9,1’ha,1’b,1’hc,1’hd,1’he,1’hf

- 0~F/f

- 8421编码

5.2、数字电路中的补码

- 数字电路中的数值均使用正数表示,负数需要使用补码的方式表示

- 最高位是1是代表负数,0时代表正数

- 正数的补码是正数自己

- 负数的补码:符号位保持不变,其他所有bit反转,然后+1

- eg:+5:原码为0101,补码为0101;-5:原码为:1101,补码码为1011。

5.3、布尔逻辑

- 与逻辑

&- 全为1时,与逻辑值为1

- 有一个位0,与逻辑值为0

- 或逻辑

||- 全为0时,或逻辑为0

- 有一个位1时,或逻辑为1

|算术运算符;||逻辑运算符(只有对True和错False) 都是代表或;对于单比特两者都一样,多比特两者不一样。- 如果 a = 3’b101,b = 3’b110,那么 c = a

|b = 3’b111; - 如果 a = 3’b101,b = 3’b110,那么 c = a

||b = 3’b001;

- 如果 a = 3’b101,b = 3’b110,那么 c = a

- 同理

~算数运算符,!逻辑运算符

- 非逻辑:

!- 0的非逻辑为1

- 1的非逻辑为0

参考

边栏推荐

- 1:引文;

- . Net distributed transaction and landing solution

- 什么是pyc文件

- ACM getting started Day1

- openh264解码数据流向分析

- Leetcode: binary tree 15 (find the value in the lower left corner of the tree)

- B站UP搭建世界首个纯红石神经网络、基于深度学习动作识别的色情检测、陈天奇《机器学编译MLC》课程进展、AI前沿论文 | ShowMeAI资讯日报 #07.05

- Debezium series: modify the source code to support drop foreign key if exists FK

- Go language | 01 wsl+vscode environment construction pit avoidance Guide

- Redis cluster simulated message queue

猜你喜欢

Using repositoryprovider to simplify the value passing of parent-child components

Successful entry into Baidu, 35K monthly salary, 2022 Android development interview answer

40000 word Wenshuo operator new & operator delete

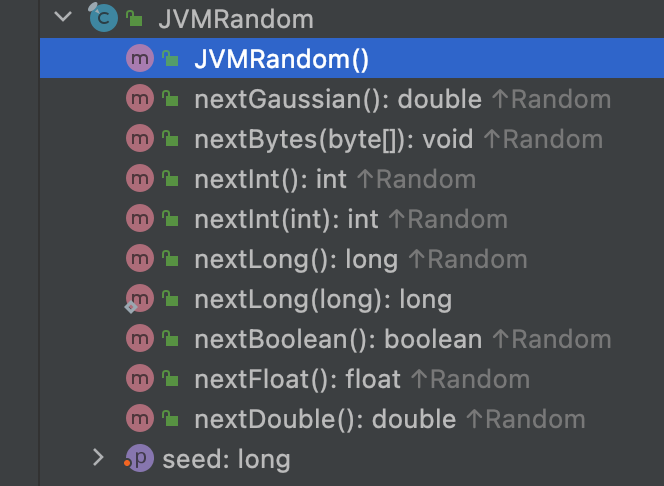

Jvmrandom cannot set seeds | problem tracing | source code tracing

使用 RepositoryProvider简化父子组件的传值

leetcode刷题:二叉树10(完全二叉树的节点个数)

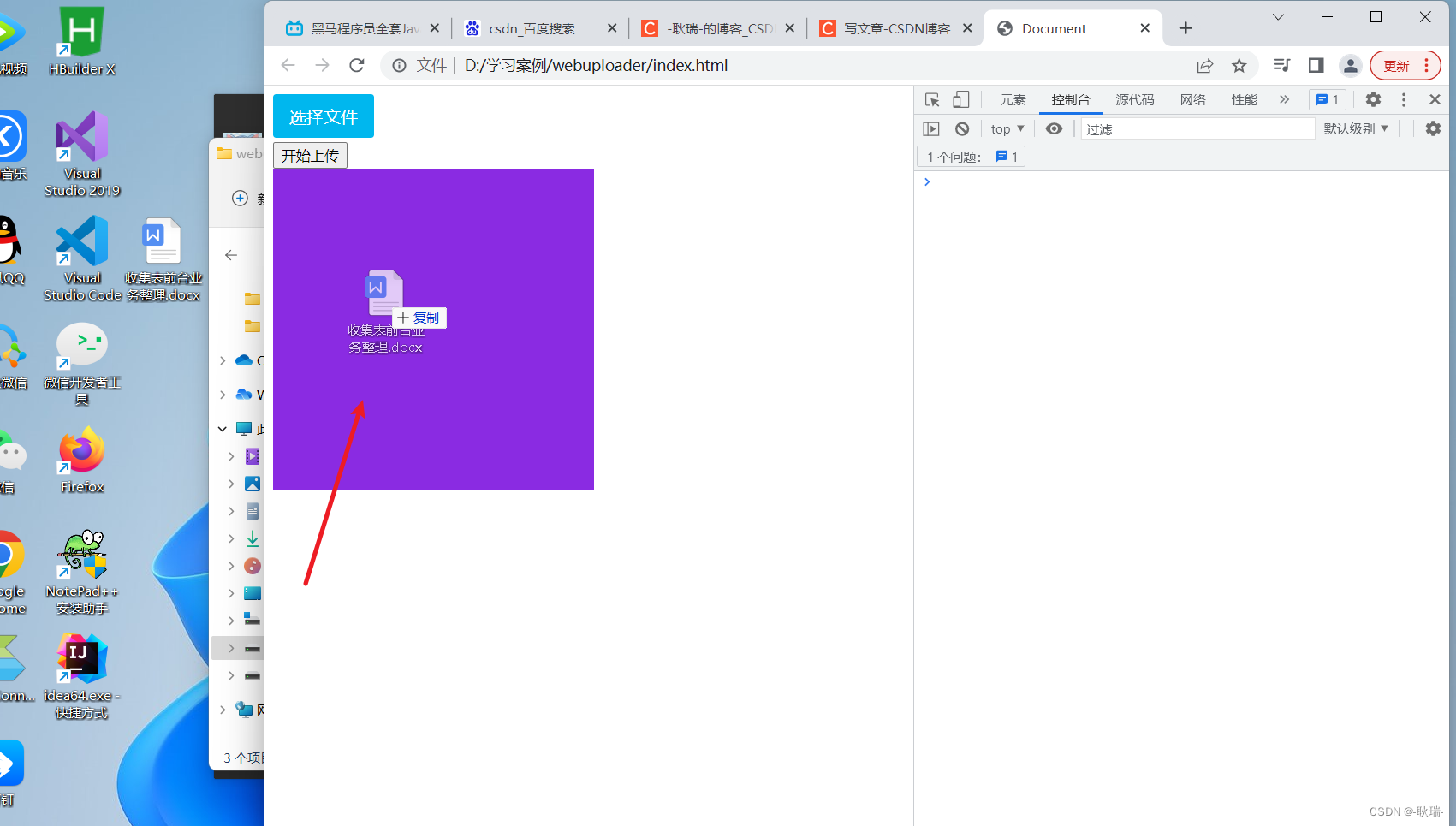

Webuploader file upload drag upload progress monitoring type control upload result monitoring control

实操演示:产研团队如何高效构建需求工作流?

leetcode刷题:二叉树13(相同的树)

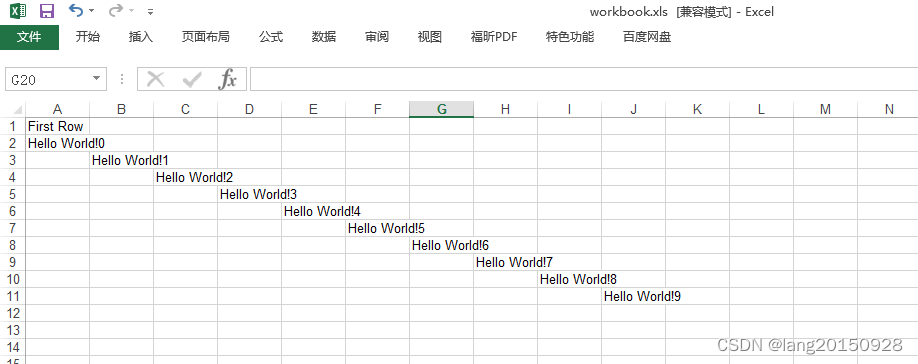

Add data to excel small and medium-sized cases through poi

随机推荐

2022年7月4日-2022年7月10日(ue4视频教程mysql)

什么是pyc文件

Jvmrandom cannot set seeds | problem tracing | source code tracing

Debezium series: PostgreSQL loads the correct last submission LSN from the offset

《乔布斯传》英文原著重点词汇笔记(十二)【 chapter ten & eleven】

Build your own website (16)

Elk distributed log analysis system deployment (Huawei cloud)

Process file and directory names

95后阿里P7晒出工资单:狠补了这个,真香...

gst-launch的-v参数

ffplay文档[通俗易懂]

Wechat applet regular expression extraction link

Is it safe for CICC fortune to open an account online?

微信小程序正则表达式提取链接

随机数生成的四种方法|Random|Math|ThreadLocalRandom|SecurityRandom

leetcode刷题:二叉树15(找树左下角的值)

Win10 x64环境下基于VS2017和cmake-gui配置使用zxing以及opencv,并实现data metrix码的简单检测

Go language | 03 array, pointer, slice usage

函数的概念及语法

JVMRandom不可设置种子|问题追溯|源码追溯