当前位置:网站首页>[quick start of Digital IC Verification] 1. Talk about Digital IC Verification, understand the contents of the column, and clarify the learning objectives

[quick start of Digital IC Verification] 1. Talk about Digital IC Verification, understand the contents of the column, and clarify the learning objectives

2022-07-05 20:09:00 【luoganttcc】

Reading guide : The author has the honor to be a pioneer in the field of electronic information in China “ University of electronic technology ” During postgraduate study , Touch the cutting edge Numbers IC Verification knowledge , I heard something like Huawei Hisilicon 、 Tsinghua purple light 、 MediaTek technology And other top IC related enterprises in the industry , Pairs of numbers IC Verify some knowledge accumulation and learning experience . Want to get started for help IC Verified friends , After one or two thoughts , This column is specially opened , In order to spend the shortest time , Take the least detours , Most learned IC Verify technical knowledge .

List of articles

One 、 Column content

1.1、 Overview Edition

- ①、 This column covers numbers IC What the verification engineer must master Core theories and skills

- ②、Linux operating system (shell)、gvim Text editing tools ( Regular expression , Shortcut key )、EDA Logic simulation tool

- ③、Verilog Language 、SystemVerilog Verification and UVM Validation methodology

- ④、SoC Chip design verification Practical projects (MCU)

- ⑤、 With random Random Incentive generation , Coverage driven validation strategy , Logic simulation technology , Debugging technology , Assertion Technology

- ⑥、 Apply the verification theory and conclusion learned to solve the problem of functional verification in digital circuit system

1.2、 A detailed version

- ①、 This column covers numbers IC What the verification engineer must master Core theories and skills

- ②、Linux operating system (shell)、gvim Text editing tools ( Regular expression , Shortcut key )、EDA Logic simulation tool (Mentor-Questasim and Sysnopsys-VCS It's the point )

- Main stream EDA Manufacturers and their tools

- Cadence: NC-Sim

- Mentor: Questasim(Modelsim Upgraded version )

- synopsys: VCS

- Main stream EDA Manufacturers and their tools

- ③、Verilog Language 、SystemVerilog Verification and UVM Validation methodology

- C/Matlab --( Manually implement the algorithm )–> RTL --(EDA Tool implementation )–> CMOS

- DUT:Design under Test

- Usually use Verilog To complete DUT Of RTL Code writing , It will be integrated into circuit and gate level netlist , The final film . What we need to know is , Written by the design engineer RTL It is difficult for the code to ensure that the logical function is completely correct , The verification engineer needs to describe various working scenarios , Send incentives to verify whether his behavior meets expectations !

- TOM:Time Of Market Time to market

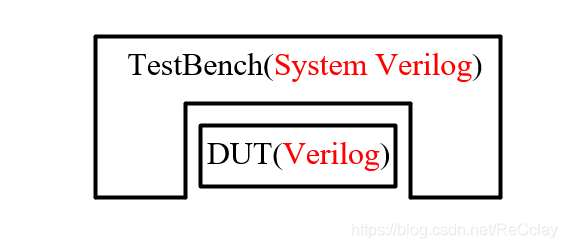

- TestBench( Verification environment ) structure , from DUT decision

- DUT Simple ,TestBench Usually use

FLattenstructure - DUT complex 、 Chip iteration TOM( Time to market ) Demand is high 、Reusable( reusable ) requirement ,TestBench Usually use

Hierarchicalstructure , Thus, there is the verification methodology , It comes down to UVM(Universal Verification Methodology - General validation methodology ).

- DUT Simple ,TestBench Usually use

- ④、SoC Chip design verification Practical projects (MCU)

- ⑤、 With random Random excitation Generate , Coverage driven validation strategy ; Logic simulation technology , Debugging technology , Assertion Technology

“ With random Random excitation Generate , Coverage driven validation strategy ”: Belong to UVM Validation methodology , stay RTL It will be introduced in detail during the design

“ Logic simulation technology ”: For simple logic , Use things like Questasim Of EDA Tools to do some simulation

“ Debugging technology ”: Find out BUG, How to analyze BUG, There are some BUG yes DUT Of , Some may be TestBench Of .

“ Assertion Technology ”:TestBench and DUT It is the horseshoe structure shown in the above figure ,TestBench You can only see DUT The interface of , If Want to see DUT Internal signals , At this time, assertion technology can be used , Check whether the internal behavior is consistent with expectations !

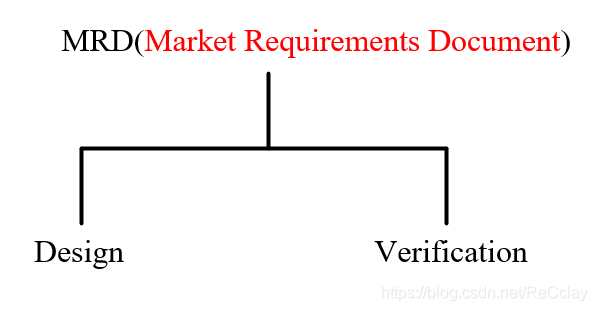

The core of verification : completeness

- I、Design: Realization The function point

- II、Verification: verification The function point

- ①、 Understand all function points

- ②、 Verify all function points

Use Random excitation reason :

- I、 If the function points of the design are subdivided , There may be millions , Verify that one by one coverage cannot be achieved at this time , It's here Random excitation The methodology of information technology . This method , Time for space , Keep running every day , But the motivation of each running use case is different . Correlate with time through random seeds , Time is different , Random seeds are different , Random excitation is different .

- II、 Use random excitation , In this way, the omission of artificial analysis may also be involved !

Use Coverage driven reason :

- I、 Excitation random generation sending , Then, to what extent is my verification completed ? And then there is : Coverage driven . The front excitation is random , Collect the results later to see the coverage . Look at those points , Whether it is covered by random .

- II、 Coverage classification :

- ①、 Functional coverage : See whether the function point has reached .

- ②、 Code coverage : Through tool analysis , Incentive whether to put every line of code , Each branch and its combination are covered .【 Line overlay 、 Conditional coverage 、Toggle Cover 】

- ⑥、 application Verification of learning Theory and conclusion solve Function verification in digital circuit system problem

Two 、 special column Technology stack The goal is

- Skillfully use Linux operating system

- Skillfully use gvim Text editing tools

- Familiar use EDA Logic simulation tool Questasim and VCS

- Master the classic digital circuit Verilog RTL Design

- Have a good command of System Verilog Verification language

- Have a good command of UVM Validation methodology

- Have a good command of SoC Chip architecture 、 Application scenarios and data flows

- Have a good command of AHB-SRAM/AHB-SD-Host/APB-SPI The verification process of 、 Verification method 、 Verification key points and difficulties

- Master the randomized verification strategy with constraints and the coverage driven verification strategy

3、 ... and 、 Numbers IC Job description

- front end (RTL Logic implementation )

- Design

- verification ( function verification )

- EDA Simulation verification ( Verify mainstream , This column focuses on )

- FPGA Prototype verification ( System level verification )

- Back end (RTL Logic is transformed into netlist)

- BES( Synthesis and timing)

- DFX(DFT For manufacturing defects , For testing only ;DFX Besides manufacturing , There are functions that need debugging , Will also be in DFX Consider... In the design )

notes : For the front end , The subsequent ways to improve are :

- I、 From a technical point of view : Architecture Engineer 、 System Engineer

- II、 From a management perspective : verification Leader、 project manager 、 division manager

Four 、 Column content planning

Numbers IC Verify the basic theories and skills of engineers

- LInux operating system

- Gvim Text editing tools

- Classic digital circuit Verilog RTL Design

- Logic simulation tool QuestaSim、VCS

SystemVerilog Verification language

- Questasim(VCS) + Labs( experiment )

UVM Validation methodology

- VCS + Labs( experiment )

5、 ... and 、 Learning requirements - “ Three more ”

- How to write code

- Do more simulations

- Do more exercises

边栏推荐

- Where is the operation of new bonds? Is it safer and more reliable to open an account

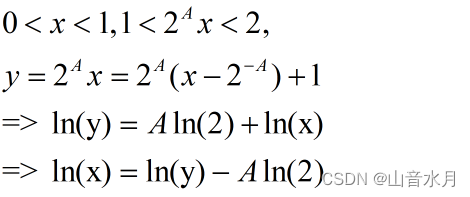

- 计算lnx的一种方式

- How to retrieve the root password of MySQL if you forget it

- C - sequential structure

- [C language] three implementations of quick sorting and optimization details

- Is the education of caiqiantang reliable and safe?

- Autumn byte interviewer asked you any questions? In fact, you have stepped on thunder

- How to safely and quickly migrate from CentOS to openeuler

- Tasks in GStreamer

- [hard core dry goods] which company is better in data analysis? Choose pandas or SQL

猜你喜欢

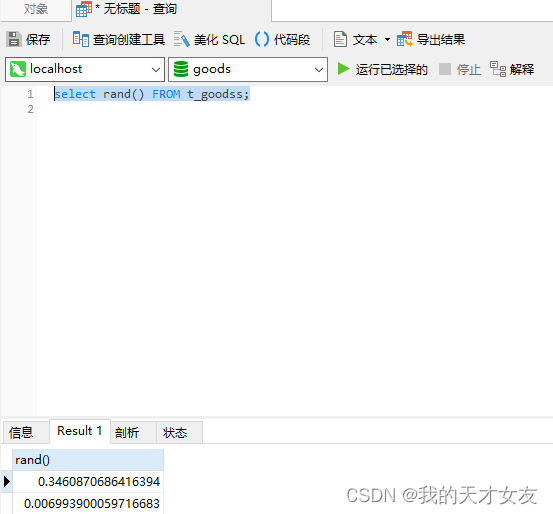

Database logic processing function

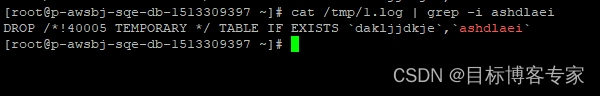

Debezium series: record the messages parsed by debezium and the solutions after the MariaDB database deletes multiple temporary tables

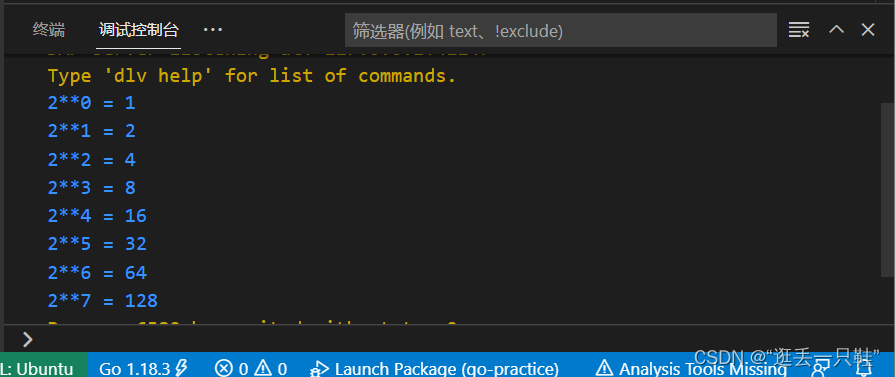

Go language | 02 for loop and the use of common functions

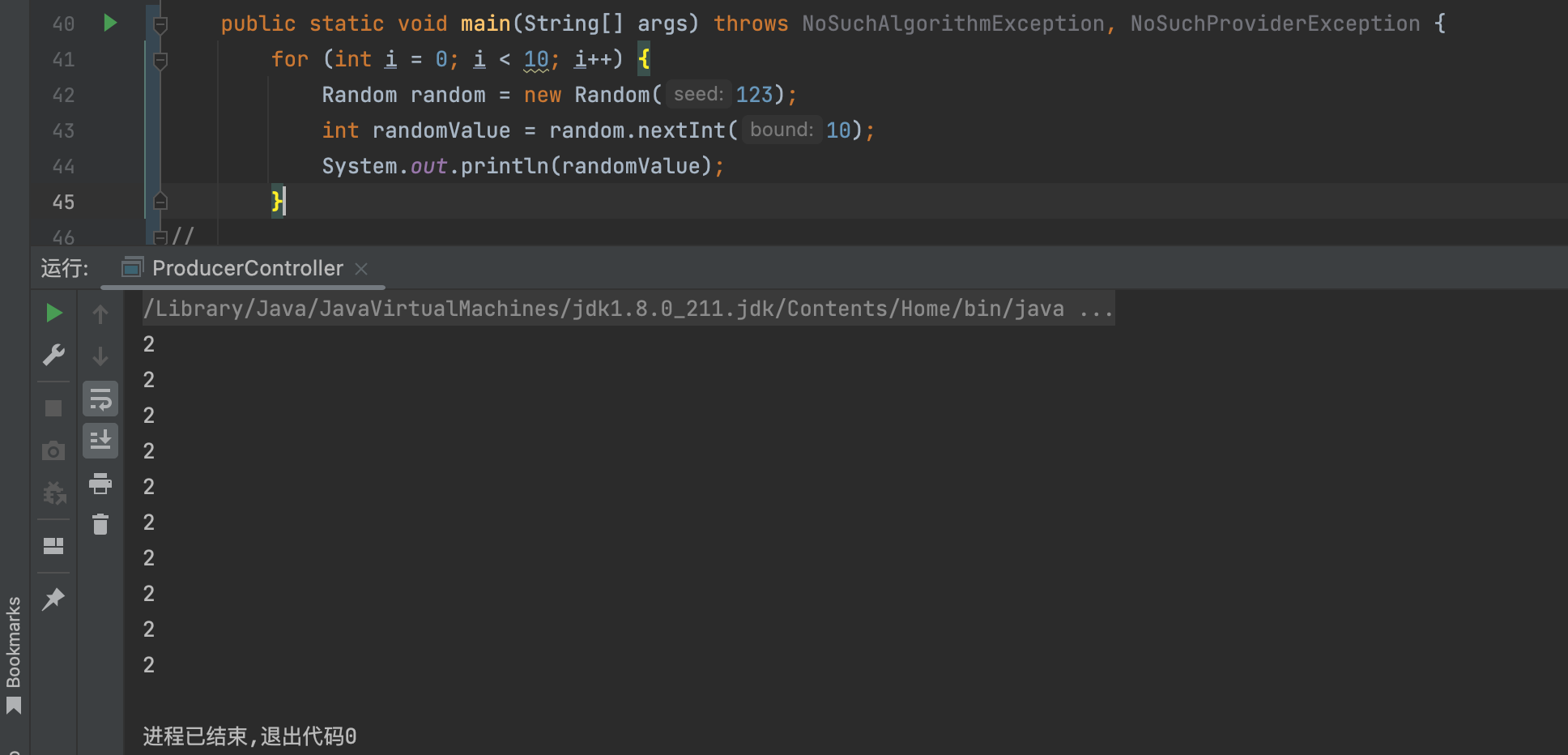

Securerandom things | true and false random numbers

计算lnx的一种方式

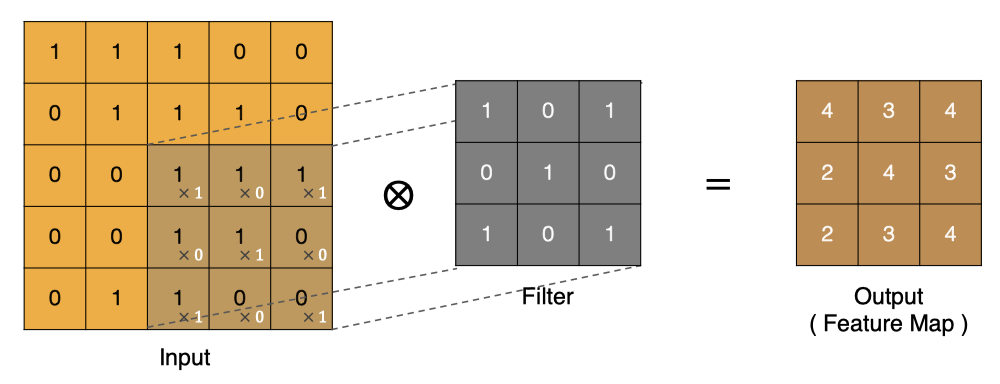

Fundamentals of deep learning convolutional neural network (CNN)

Autumn byte interviewer asked you any questions? In fact, you have stepped on thunder

95后阿里P7晒出工资单:狠补了这个,真香...

Scala基础【HelloWorld代码解析,变量和标识符】

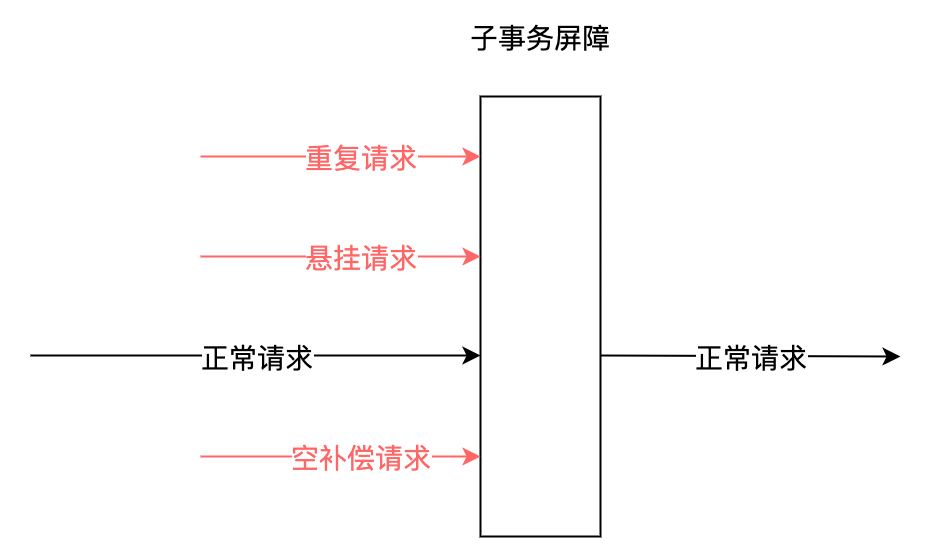

. Net distributed transaction and landing solution

随机推荐

Guidelines for application of Shenzhen green and low carbon industry support plan in 2023

Wildcard selector

B站UP搭建世界首个纯红石神经网络、基于深度学习动作识别的色情检测、陈天奇《机器学编译MLC》课程进展、AI前沿论文 | ShowMeAI资讯日报 #07.05

[C language] string function and Simulation Implementation strlen & strcpy & strcat & StrCmp

[C language] three implementations of quick sorting and optimization details

Is it safe for Galaxy Securities to open an account online?

third-party dynamic library (libcudnn.so) that Paddle depends on is not configured correctl

ffplay文档[通俗易懂]

Build your own website (16)

Go language | 02 for loop and the use of common functions

Go language | 01 wsl+vscode environment construction pit avoidance Guide

sun.misc.BASE64Encoder报错解决方法[通俗易懂]

Leetcode brush questions: binary tree 18 (largest binary tree)

Is it safe for CICC fortune to open an account online?

95后阿里P7晒出工资单:狠补了这个,真香...

id选择器和类选择器的区别

14. Users, groups, and permissions (14)

Leetcode: binary tree 15 (find the value in the lower left corner of the tree)

Leetcode brush question: binary tree 14 (sum of left leaves)

How to safely and quickly migrate from CentOS to openeuler