当前位置:网站首页>【数字IC验证快速入门】8、数字IC中的典型电路及其对应的Verilog描述方法

【数字IC验证快速入门】8、数字IC中的典型电路及其对应的Verilog描述方法

2022-07-05 20:06:00 【luoganttcc】

导读:作者有幸在中国电子信息领域的排头兵院校“电子科技大学”攻读研究生期间,接触到前沿的数字IC验证知识,旁听到诸如华为海思、清华紫光、联发科技等业界顶尖集成电路相关企业面授课程,对数字IC验证有了一些知识积累和学习心得。为帮助想入门前端IC验证的朋友,思忱一二后,特开此专栏,以期花最短的时间,走最少的弯路,学最多的IC验证技术知识。

文章目录

一、硬件描述语言

- HDL的主流语言

- VHDL

- Verilog

- SystemVerilog

- 硬件描述的层次

- 门级(Gate-Level)【可综合】

- 寄存器传输级(RTL-Level)【可综合】

- 行为级【不一定可综合】

- RTL:Register Transfer Level

- 可综合性

- 可阅读性

二、典型电路

2.1、组合逻辑电路:全加器

module fulladd(

input wire ain,

input wire bin,

input wire cin,

output wire sum,

output wire cout

);

assign sum = ain ^ bin ^ cim;

assign cout = (ain & bin) | (bin & cin) | (ain & cin);

endmodule

- 在assign中赋值的变量类型必须为wire类型

- 在always或initial中赋值必须为reg类型

2.2、组合逻辑电路:四选一选择器

module mux_4_1( input wire C, input wire D, input wire E, input wire F, input wire [1:0] S, input reg Mux_out ); [email protected](C or D or E or F or S) begin case(S) 2'b00 : Mux_out = C; 2'b01 : Mux_out = D; 2'b10 : Mux_out = E; default : Mux_out = F; endcase end endmodule2.3、组合逻辑电路:38译码器

[email protected](enable or ain) begin if(!enable) yout = 8'b0; else case(ain) 3'b000 : yout = 8'b0000_0001; 3'b001 : yout = 8'b0000_0010; 3'b010 : yout = 8'b0000_0100; 3'b011 : yout = 8'b0000_1000; 3'b100 : yout = 8'b0001_0000; 3'b101 : yout = 8'b0010_0000; 3'b110 : yout = 8'b0100_0000; 3'b111 : yout = 8'b1000_0000; endcase end- 学习上述的独热码

- 注意

l和1是不一样的! 2.4、组合逻辑电路:逻辑操作

[email protected](A or B) begin Q1 = A > B; Q2 = A < B; Q3 = A >= B; end // Q3 = A >= B; 等价于下面的代码 if(A >= B) Q3 = 1 else Q3 = 0;2.5、组合逻辑电路:移位操作

2.5、组合逻辑电路:移位操作

module shift( input wire [3:0] data, output reg [3:0] q1, output reg [3:0] q2, ); parameter B = 2; [email protected](data) begin q1 = data << B;//左移 q2 = data >> B;//右移 end endmodule2.6、时序逻辑电路:计数器

module count_en( input wire clock, input wire reset, input wire enable, output reg [WIDTH-1 : 0] out ); parameter WIDTH = 8; parameter UDLY = 1; [email protected](posedge clock or negedge reset) begin if(!reset) out <= 8'b0; else if(enable) out <= #UDLY out + 1; //模仿器件延时,一般不提倡 end endmodule- 时序逻辑赋值,要用非阻塞赋值

2.7、时序逻辑电路:异步复位D触发器

module dff_async_pre( input wire data, input wire clk, input wire preset, output reg q ); parameter U_DLY = 1; [email protected](posedge clk or negedge preset)//异步复位 begin if(~preset) q <= #U_DLY 1'b1; else q <= #U_DLY data; end endmodule- if/else 存在优先级

2.8、时序逻辑电路:同步复位D触发器

module dff_sync_rst( input wire data, input wire clk, input wire reset, output reg q ); parameter U_DLY = 1; [email protected](posedge clk)//同步复位 begin if(!reset) q <= #U_DLY 1'b0; else q <= #U_DLY data; end endmodule2.9、时序逻辑电路:复杂D触发器(用的比较少)

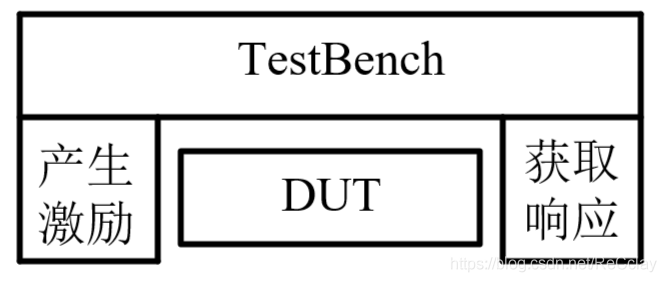

module dff_sync( input wire data, input wire clk, input wire reset, input wire preset, output reg q ); parameter U_DLY = 1; [email protected](posedge clk or negedge reset or negedge preset)//同步复位+异步复位 begin if(~reset) q <= 1'b0; else if(~preset) q <= 1'b1; else q <= #U_DLY data; end endmodule三、TestBench功能

- 产生激励 Generate stimulus

- 将激励输入到待测设计(DUT - Design Under Test)

- 产生预期 Generate Expectation

- 获取响应(Capture response)

- 检查响应的正确性(Check the response for correctness)

- 对于复杂的TestBench,如后续用SystemVerilog写的TestBench(即SVTB),大都需要在TestBench中加入Reference Module(RM),然后将激励引入到RM模块中,并将RM的输出结果保存起来,进而与响应输出的结果进行比对(check)。如果结果一致,那么用例通过;如果对不上,那么DUT或RM可能有问题,需要重新检查。

- 对于VTB,测试对象比较小,功能比较简单通常不需要加入RM。

- RM的逻辑行为与DUT一样,只不过其中没有了延时信息!

- 根据验证目标评估验证进度(Measure the progress against the overall verification goals)

- 验证的核心思想:验证完备性,不仅仅是找BUG

- 证明DUT的功能是ok的,所以首先要将DUT的功能点(Feature)给分解完全!然后依次验证每个功能点是否ok,如果error,那么就要去找BUG。

- 验证进度需要看覆盖率CDV(Coverage Driven Verification),通常可分为两种:功能覆盖率【主观】(分解功能点,需要验证每个功能点,= 100%)、代码覆盖率【客观】(可能会存在冗余代码,某些代码会验不到,<100%)

注:输入的信号称为激励,输入激励的不同组合我们称之为不同的Pattern,也叫测试点(Test Pattern)。输出的信号称为响应。

四、验证四要素

- 1、灌激励:产生输入信号

- 2、做预期:产生预期结果

- Reference Model,简称为RM

- 3、集响应:收集输出信号

- 4、做比较:比较结果

- 目的:验证结果比对的自动化

五、fulladd_tb实例

`timescale 1ns/1ps module fulladd_tb; reg ain, bin, cin; wire cout, sum; reg clk; always #1 clk = ~clk; //此处时钟没用,全加器只是个组合逻辑 //产生激励 initial begin clk = 0; ain = 0; bin = 1; cin = 1; #10 ain = 1; bin = 1; cin = 0; #10 ain = 1; bin = 1; cin = 1; #10 $finish; end //收集响应 initial begin #5; if(sum!=0) $display("sum calc ERROR!!!, sum = %b", sum); else $display("SUM calc correct!!!"); if(cout!=1)$display("cout clac ERROR!!!, cout = %b", cout); else $display("cout calc correct!!!"); #10; if(sum!=0) $display("sum calc ERROR!!!, sum = %b", sum); else $display("SUM calc correct!!!"); if(cout!=1)$display("cout clac ERROR!!!, cout = %b", cout); else $display("cout calc correct!!!"); #10 if(sum!=1) $display("sum calc ERROR!!!, sum = %b", sum); else $display("SUM calc correct!!!"); if(cout!=1)$display("cout clac ERROR!!!, cout = %b", cout); else $display("cout calc correct!!!"); end //例化 fulladd u0_fulladd( .cout (cout), .sum (sum), .ain (ain), .bin (bin), .cin (cin) ); endmodule参考

【FPGA基础】一文快速上手 Verilog 基础知识(总结版)

边栏推荐

- selenium 元素信息

- 常用运算符与运算符优先级

- 微信小程序正则表达式提取链接

- 浮动元素与父级、兄弟盒子的关系

- Database logic processing function

- JS implementation prohibits web page zooming (ctrl+ mouse, +, - zooming effective pro test)

- Is it safe for Anxin securities to open an account online?

- Leetcode skimming: binary tree 12 (all paths of binary tree)

- 深度學習 卷積神經網絡(CNN)基礎

- Android interview classic, 2022 Android interview written examination summary

猜你喜欢

95后阿里P7晒出工资单:狠补了这个,真香...

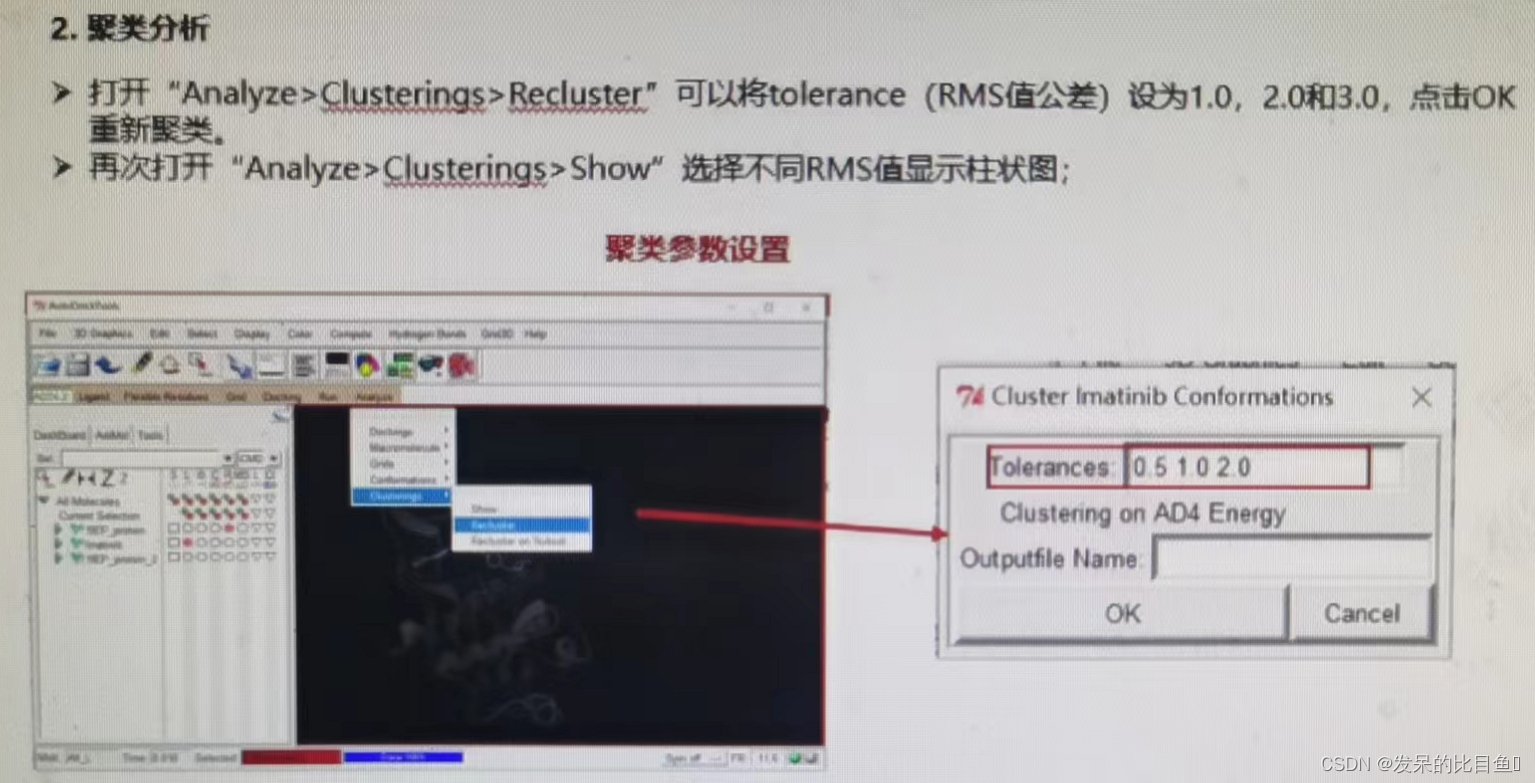

CADD课程学习(7)-- 模拟靶点和小分子相互作用 (半柔性对接 AutoDock)

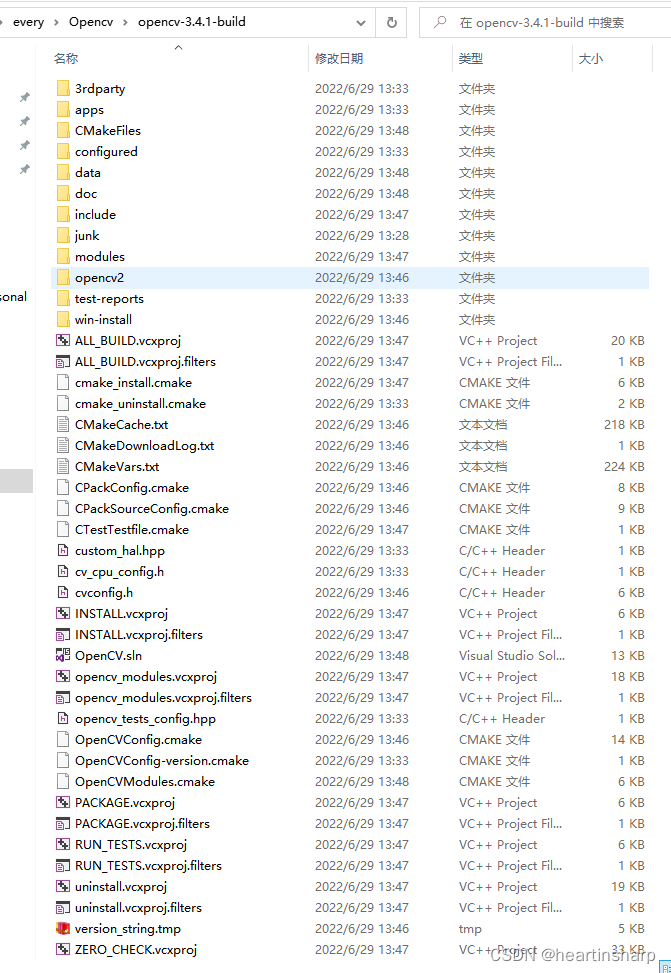

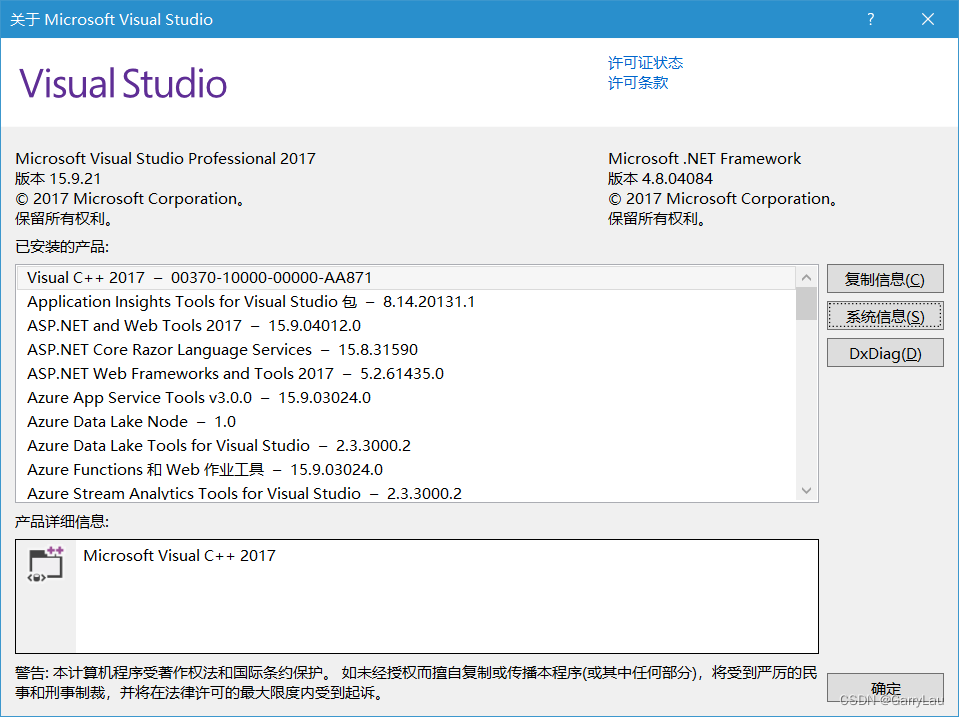

Based on vs2017 and cmake GUI configuration, zxing and opencv are used in win10 x64 environment, and simple detection of data matrix code is realized

再忙不能忘安全

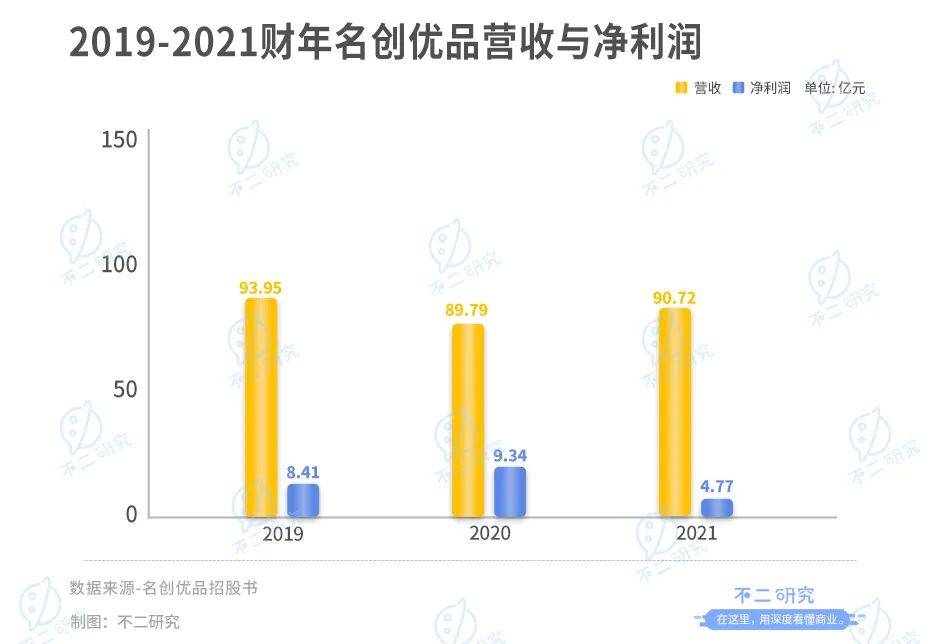

港股将迎“最牛十元店“,名创优品能借IPO突围?

40000 word Wenshuo operator new & operator delete

Complete interview questions for interviewers and senior Android engineers in front-line Internet enterprises

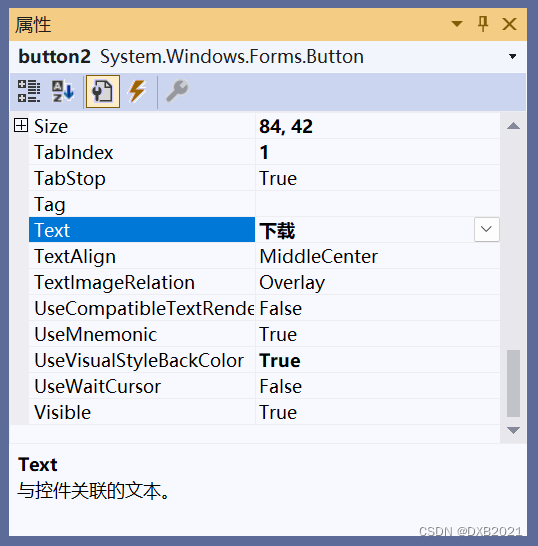

C application interface development foundation - form control (5) - grouping control

Win10 x64环境下基于VS2017和cmake-gui配置使用zxing以及opencv,并实现data metrix码的简单检测

Wechat applet regular expression extraction link

随机推荐

Solve the problem that the database configuration information under the ThinkPHP framework application directory is still connected by default after modification

Leetcode: binary tree 15 (find the value in the lower left corner of the tree)

third-party dynamic library (libcudnn.so) that Paddle depends on is not configured correctl

Is it safe for Anxin securities to open an account online?

Is it safe for Guosen Securities to open an account online?

leetcode刷题:二叉树18(最大二叉树)

618 "low key" curtain call, how can baiqiushangmei join hands with the brand to cross the "uncertain era"?

js实现禁止网页缩放(Ctrl+鼠标、+、-缩放有效亲测)

Leetcode brush question: binary tree 13 (the same tree)

.Net分布式事務及落地解决方案

线程池参数及合理设置

如何安全快速地从 Centos迁移到openEuler

The difference between ID selector and class selector

Analysis of openh264 decoded data flow

C language OJ gets PE, OJ of ACM introduction~

Debezium series: modify the source code to support UNIX_ timestamp() as DEFAULT value

Process file and directory names

随机数生成的四种方法|Random|Math|ThreadLocalRandom|SecurityRandom

.Net分布式事务及落地解决方案

2022年7月4日-2022年7月10日(ue4视频教程mysql)