当前位置:网站首页>FPGA状态机

FPGA状态机

2022-06-10 18:46:00 【Tarbet】

FPGA状态机

一、状态机实现

状态机:实现一个测试过程,该过程包括启动准备状态、启动测试、停止测试、查询测试结果、显示测试结果、测试结束返回初始化6个状态;用时间来控制该过程,90秒内完成该过程

描述状态跳转时间

- 状态机状态

- s0:准备状态

- s1:启动状态

- s2:停止状态

- s3:查询测试结果

- s4:显示测试结果

- s5:测试结束返回初始态

- 阶段性跳转

- s0 -> s1 第1s跳转到s1

- s1 -> s2 第25s跳转到s2

- s2 -> s3 第55s跳转到s3

- s3 -> s4 第60s跳转到s4

- s4 -> s5 第75s跳转到s5

- s5 -> s0 第90s跳转回初始状态

- 状态机状态

编码实现。

module fsm(

input clk,

input rst_n,

output result

);

reg[5:0] state;

reg[27:0] ctn;

parameter max_time=28'd49_999_999;

wire[63:0] timer;

parameter s0 = 6'b100000;

parameter s1 = 6'b010000;

parameter s2 = 6'b001000;

parameter s3 = 6'b000100;

parameter s4 = 6'b000010;

parameter s5 = 6'b000001;

//计数器

[email protected](posedge clk or negedge rst_n)begin

if(!rst_n)begin

ctn <= 28'd0;

end

else if(ctn == max_time)begin

ctn <= 28'd0;

end

else ctn <= ctn +1'b1;

end

always @(posedge clk or negedge rst_n)begin

if(rst_n)begin

state <= s0;

end

else

case(state)

s0:begin

if(timer == 1)

state <= s1;

else state <= s0;

end

s1:begin

if(timer == 25)

state <= s2;

else state <= state;

end

s2:begin

if(timer == 55)

state <= s3;

else state <= state;

end

s3:begin

if(timer == 60)

state <= s4;

else state <= state;

end

s4:begin

if(timer == 75)

state <= s5;

else state <= state;

end

s5:begin

if(timer == 90)

state <= s0;

else state <= state;

end

default:sr=state <= s0;

endcase

end

endmodule

二、检测10010串

- 画出可以检测10010串的状态图

- verilog编程实现

module Ce_Top(

input clk,

input rst_n,

input data,

output result

);

reg result_r;

reg[4:0] state;

parameter IDLE = 5'b10000;

parameter S1 = 5'b01000;

parameter S10 = 5'b00100;

parameter S100 = 5'b00010;

parameter S1001= 5'b00001;

[email protected](posedge clk or negedge rst_n)begin

if(!rst_n)begin

state <= IDLE;

result_r <= 1'b0;

end

else

case(state)

IDLE: begin

if(data==0)begin

state <= IDLE;

result_r <= 0;

end

else begin

state <= S1;

result_r <= 0;

end

end

S1:begin

if(data ==0)begin

state <= S10;

result_r <= 0;

end

else begin

state <=S1;

result_r <= 0;

end

end

S10:begin

if(data ==0)begin

state <= S100;

result_r <= 0;

end

else begin

state <=S1;

result_r <= 0;

end

end

S100:begin

if(data==0)begin

state <= IDLE;

result_r <= 0;

end

else begin

state <= S1001;

result_r <= 0;

end

end

S1001:begin

if(data==0)begin

state <= IDLE;

result_r <= 1;

end

else begin

state <= S1;

result_r <= 0;

end

end

default: state <= 5'bx;

endcase

end

assign result =result_r;

endmodule

三、总结

主体实验通过状态机对实验进行状态跳转,进入不同逻辑时序,在代码是线上只做了思路书写,未上板验证实验。

边栏推荐

- 【6.4-6.10】博客精彩回顾

- How to apply VR panorama in home decoration? Experience the real home decoration effect

- mixin-- 混入

- How is it safe for individuals to invest in financial management?

- 面试中经常问到的几个问题,快来看看能答对几道吧

- 马斯克称自己不喜欢做CEO,更想做技术和设计;吴恩达的《机器学习》课程即将关闭注册|极客头条

- Go语学习笔记 - 跨域配置、全局异常捕获 | Web框架Gin(四)

- Design and development of hospital reservation registration platform based on JSP Zip (thesis + project source code)

- Apicloud visual development novice graphic tutorial

- Analysis of epidemic situation in Shanghai based on improved SEIR model

猜你喜欢

2022.05.28 (lc_516_longest palindrome subsequence)

Design and development of hospital reservation registration platform based on JSP Zip (thesis + project source code)

【C语言进阶】数据的存储【下篇】【万字总结】

2022.05.25 (lc_718_longest repeating subarray)

轻松学Pytorch-全卷积神经网络实现表情识别

Apicloud visual development - one click generation of professional source code

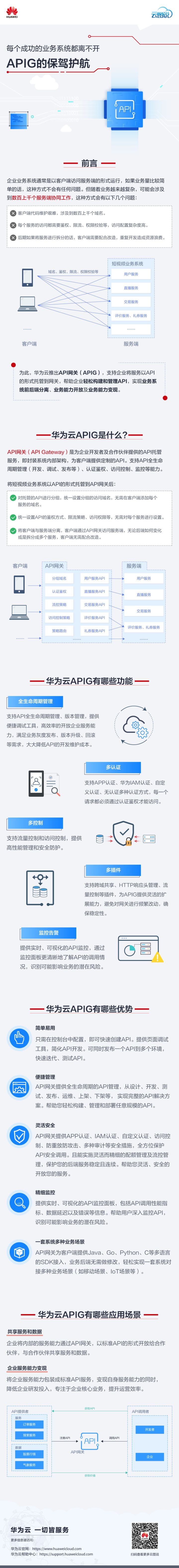

Yuntu says that every successful business system cannot be separated from apig

VR全景作品中各式各样的嵌入功能是如何做到的?

一文带你了解J.U.C的FutureTask、Fork/Join框架和BlockingQueue

高考开启,VR全景可以这样看考点

随机推荐

How to query the database table storage corresponding to a field on the sapgui screen

Longest ascending subsequence (LIS) Logu

APICloud可视化开发新手图文教程

写作技术文章是留给自己未来的财富

Does the giraffe's neck grow longer not because it eats leaves from high places? Scientists have found the answer in fossils 17million years ago

618 great promotion is coming, mining bad reviews with AI and realizing emotional analysis of 100 million comments with zero code

在VR全景中如何添加聚合热点?内容模块如何添加?

2022.05.26 (lc_1143_longest common subsequence)

Domain Driven Design (VI) - Architecture Design

OFFICE技术讲座:标点符号-中文-大全

基于改进SEIR模型分析上海疫情

【C语言】这些经典题型大家都掌握了吗?一文学会这些题

Mysql database design concept (multi table query & transaction operation)

【 Web 】 page d'accueil personnelle 】 Programme d'études 】 albums de photos 】 babillard d'information 】

Logback exclude specified package / class / method log output

It is forbidden to throw away rotten software. A guide for software test engineers to advance from elementary level to advanced level will help you promote all the way

如何在VR全景作品中添加独立热点?

软件测试月薪10K如何涨到30K,只有自动化测试能做到

Ding Dong grabs vegetables - monitoring and pushing tools for delivery period

frp reverse proxy