当前位置:网站首页>DCC888 :Register Allocation

DCC888 :Register Allocation

2022-06-27 17:32:00 【春江花月夜晨】

Register Allocation

Register Allocation

(0)These values might be stored either in registers, or in memory.

(1)Registers are fast, but they come in small quantity.

(2)Memory is plenty, but it has slower access time.

(3) A good register allocator should strive to keep in registers the variables used more often.

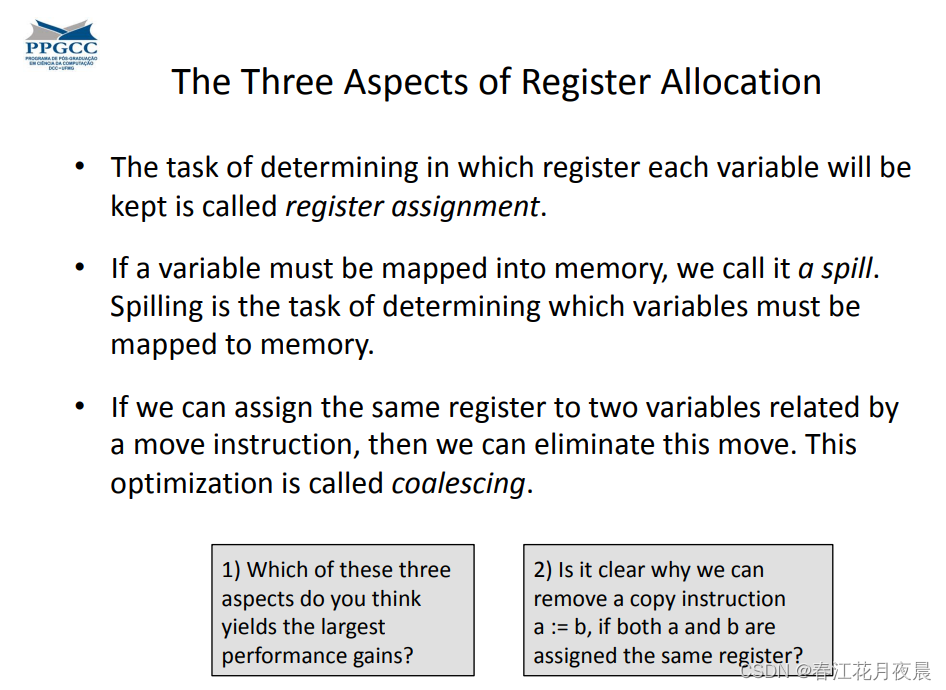

the three aspects of register allocation

register assignment

The task of determining in which register each variable will be kept

spill

If a variable must be mapped into memory, we call it a spill.

Spilling is the task of determining which variables must be mapped to memory.

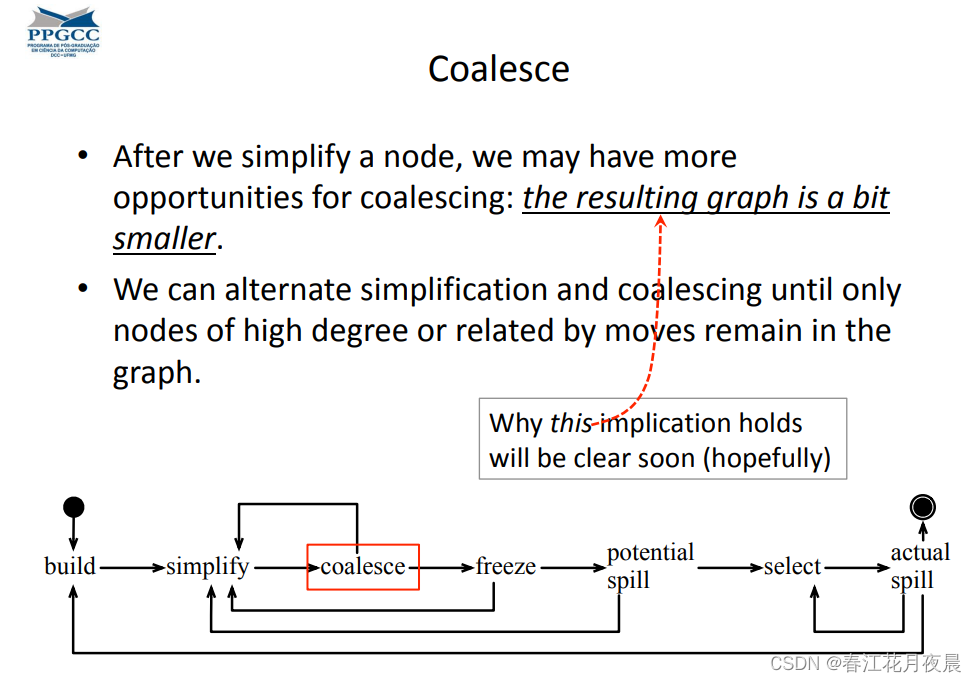

coalescing

If we can assign the same register to two variables related by a move instruction, then we can eliminate this move. This optimization is called coalescing.

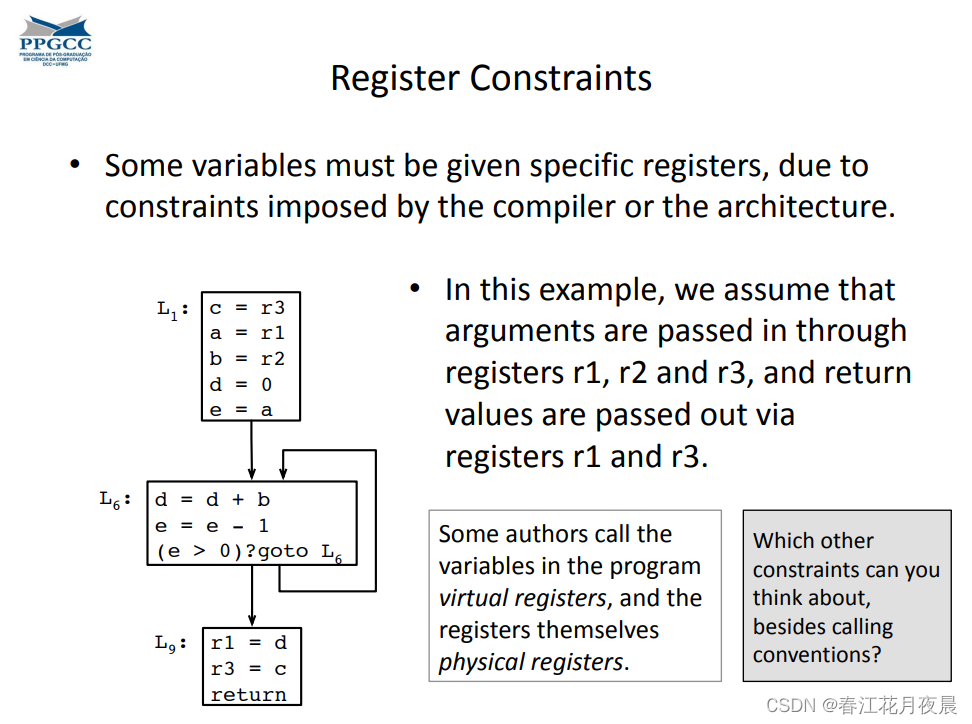

register constraints

maxLive :MaxLive is the maximum number of registers that are simultaneously alive at any program point of the program’s control flow graph.

MinReg :The minimum number of registers that a program needs,

MinReg > MaxLive

@ = e, c 该节点的input是c -> r1,e-> r2;

c = d, 该节点的input是d->r1, e->r2;

e = a, 该节点的input是d->r1, a->r2;此时发现与最开始的假设a->r1冲突。

Register Assignment is NP-Complete

Chaitin’s proof

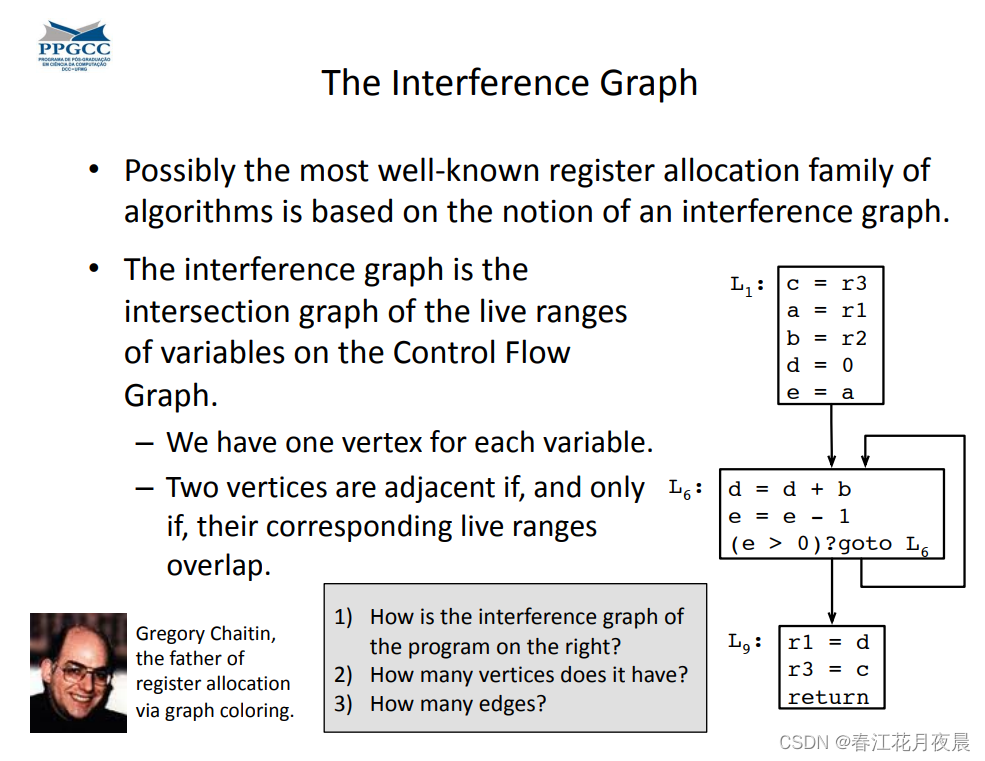

the interference graph

Linear Scan

It is based on the greedy coloring of interval graphs:

– Given a sequence of intervals, we want to find the minimum number of colors necessary to paint them, so that overlapping intervals are given different colors.

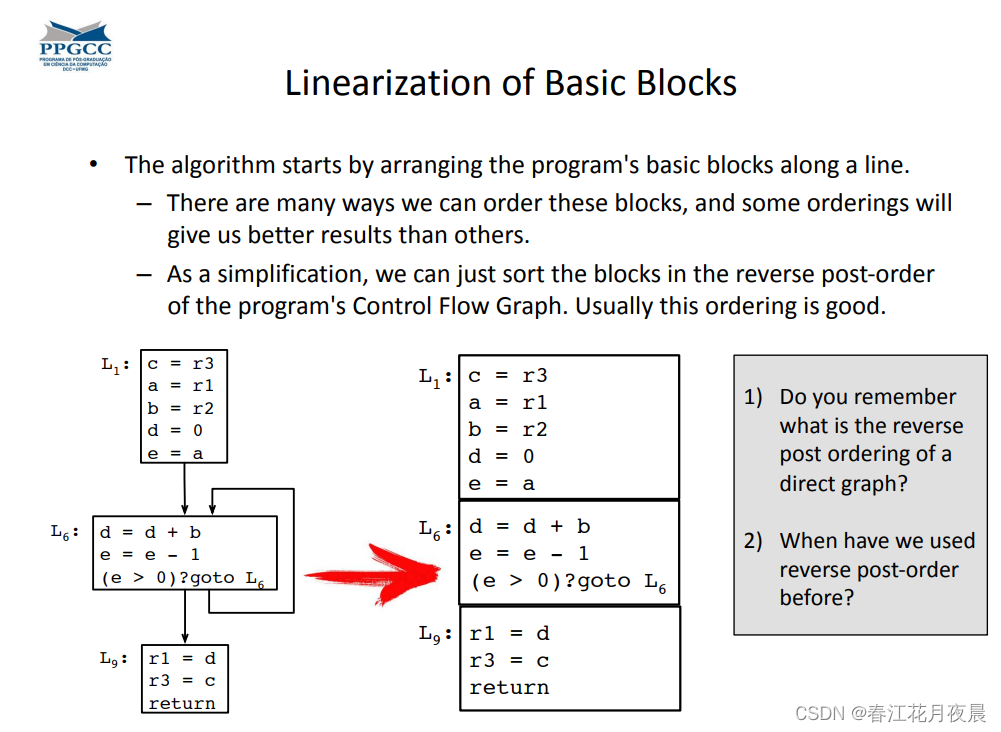

Linearization of Basic Blocks

reverse post-order

first :r3 ->c

second: r1->a

intervals once spill

spill 到memory,将会打断variable生命周期

spill :need store/load placemeng

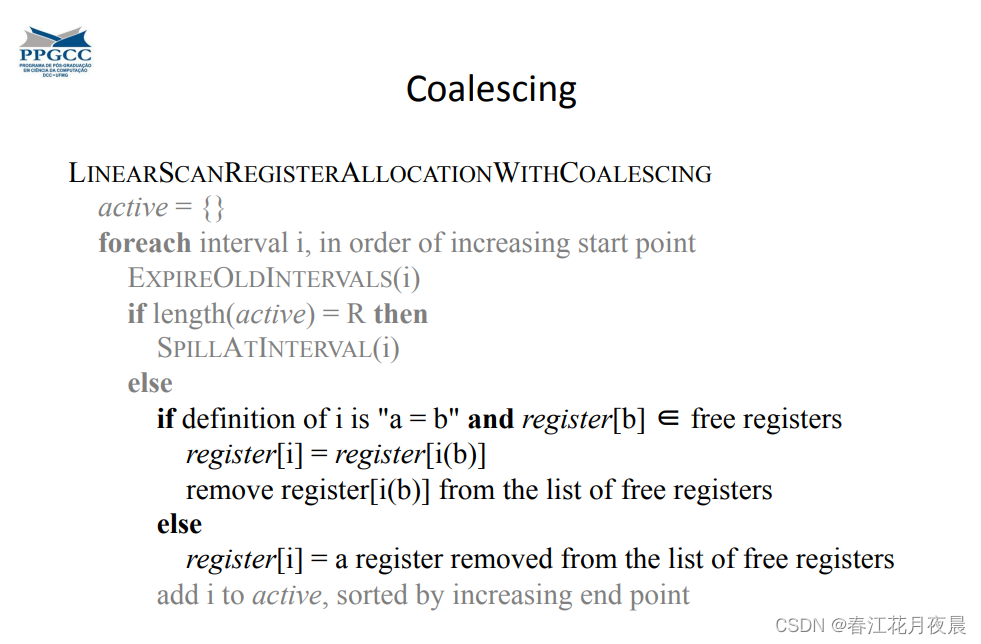

coalescing

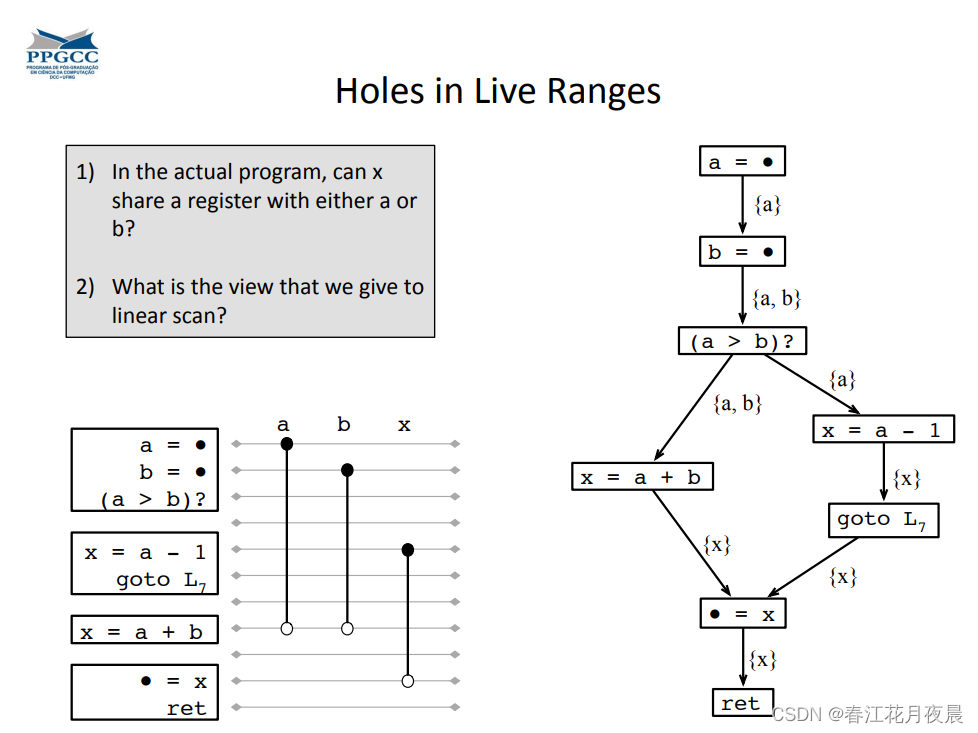

live ranges with holes

graph coloring register allocation

the interference graph

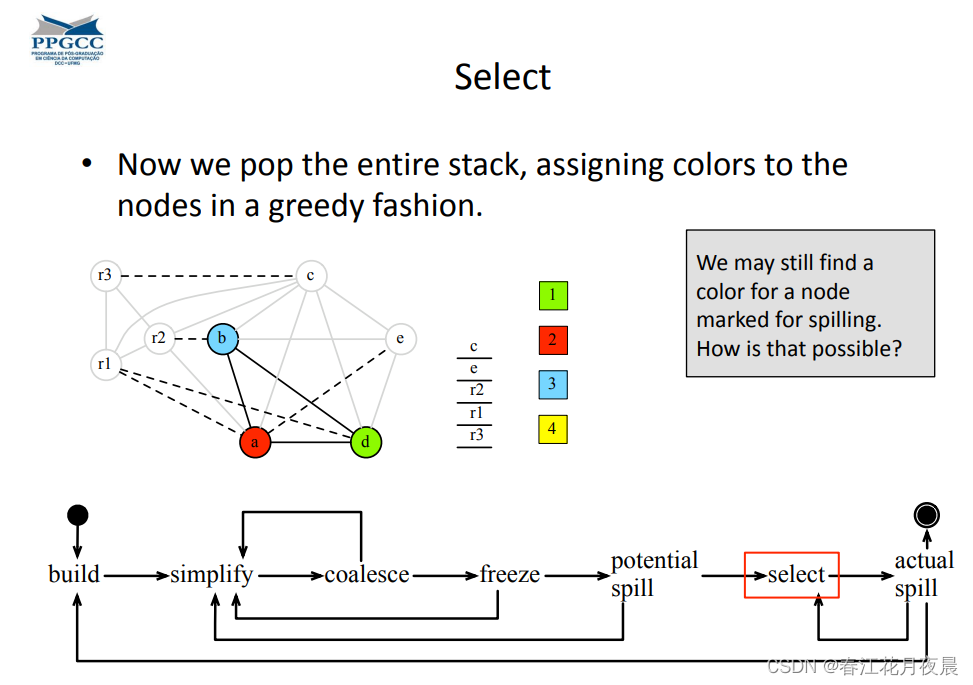

simplification的时候,将node一次放入栈中。

r3 - r1 - r2 - e - c - b - a - d

reverse order : d - a - b - c - e - r2 - r1 - r3

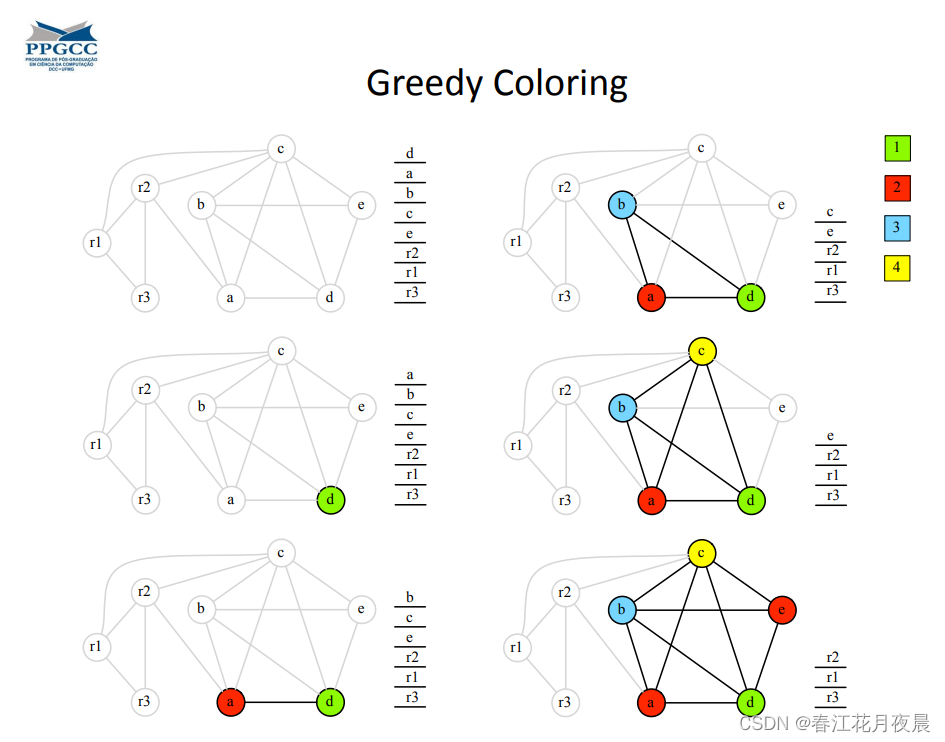

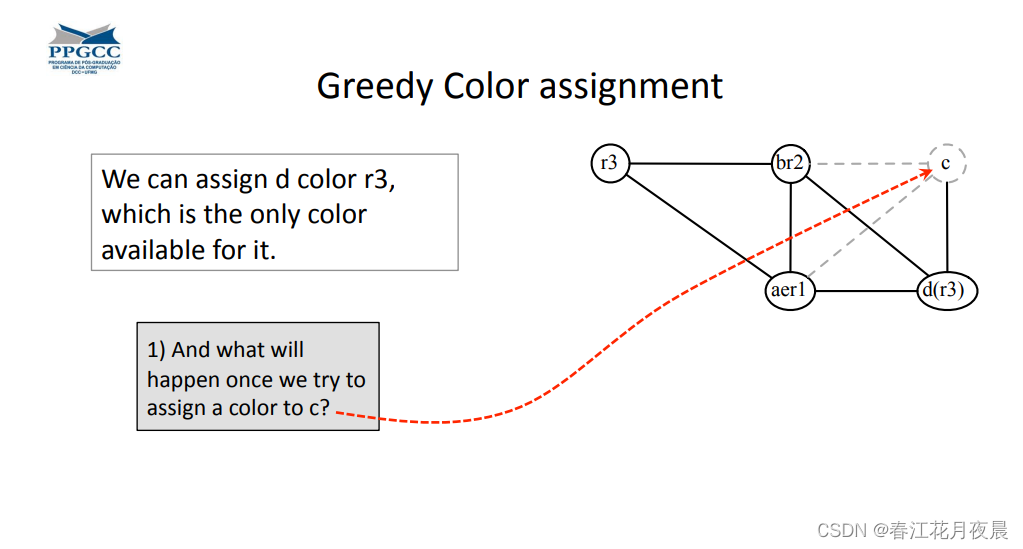

greedy coloring

iterated register coalescing

spilling heuristics

spilling

其中以d为例:2是d在loop之外的def和use,10的一次方是d的loop nesting factor是1,乘以2是因为loop之内有def和use两次,d的degree为4.

边栏推荐

- Four years of College for an ordinary graduate

- 破解仓储难题?WMS仓储管理系统解决方案

- 昱琛航空IPO被终止:曾拟募资5亿 郭峥为大股东

- Google Earth Engine(GEE)——ImageCollection (Error)遍历影像集合产生的错误

- 国信证券是国企吗?在国信证券开户资金安全吗?

- openssl客户端编程:一个不起眼的函数导致的SSL会话失败问题

- 教你打印自己的日志 -- 如何自定义 log4j2 各组件

- 基于STM32F103ZET6库函数蜂鸣器实验

- 【建议收藏】ABAP随笔-EXCEL-4-批量导入-推荐

- Jinyuan's high-end IPO was terminated: it was planned to raise 750million Rushan assets and Liyang industrial investment were shareholders

猜你喜欢

利用OpenCV执行相机校准

Blink SQL built in functions

Cloud native database: the outlet of the database, you can also take off

明美新能源冲刺深交所:年应收账款超6亿 拟募资4.5亿

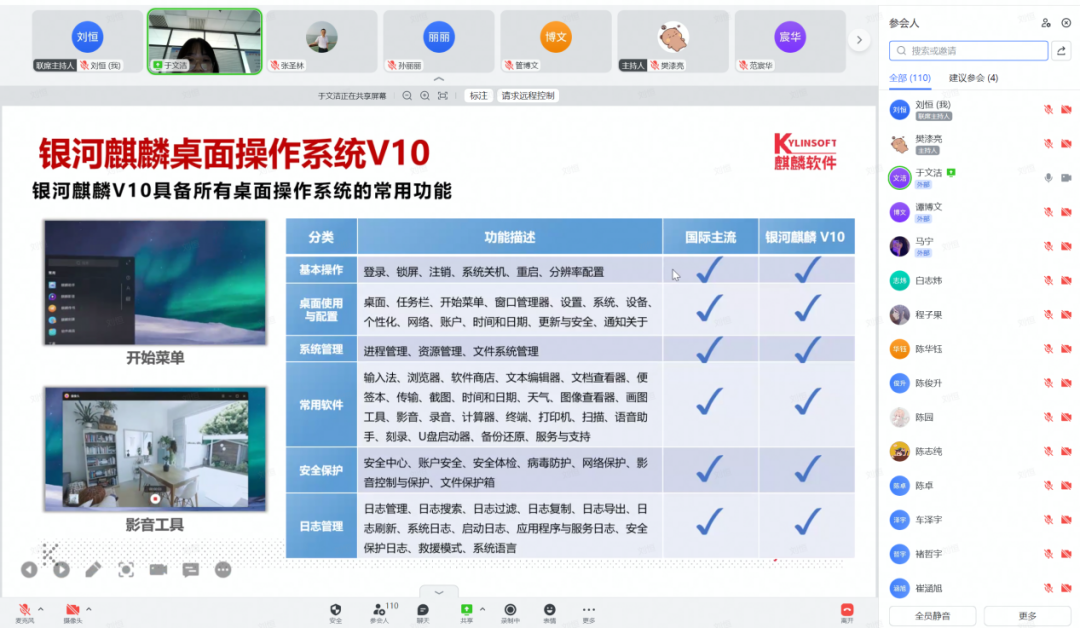

Industry university cooperation cooperates to educate people, and Kirin software cooperates with Nankai University to complete the practical course of software testing and maintenance

深度学习和神经网络的介绍

Usage of rxjs mergemap

Summary of domestic database certification test guide (updated on June 16, 2022)

Don't worry. This is the truth about wages in all industries in China

New Zhongda chongci scientific and Technological Innovation Board: annual revenue of 284million and proposed fund-raising of 557million

随机推荐

Comment encapsuler un appel à une bibliothèque

数仓的字符截取三胞胎:substrb、substr、substring

Rxjs mergeMap 的使用场合

Blink SQL built in functions

xctf攻防世界 MISC薪手进阶区

Market status and development prospect forecast of global functional polyethylene glycol (PEG) industry in 2022

Row to column and column to row in MySQL

惊呆!原来 markdown 的画图功能如此强大!

Two methods of MySQL database login and logout

一位平凡毕业生的大学四年

使用logrotate对宝塔的网站日志进行自动切割

Hikvision tools manager Hikvision tools collection (including sadp, video capacity calculation and other tools) a practical tool for millions of security practitioners

Technology sharing | introduction to kubernetes pod

Differences between mongodb and MySQL

MFS distributed file system

[cloud based co creation] the "solution" of Digital Travel construction in Colleges and Universities

binder hwbinder vndbinder

从感知机到前馈神经网络的数学推导

利用OpenCV执行相机校准

Vscode suggests that you enable gopls. What exactly is it?