当前位置:网站首页>GPIO configuration of SOC

GPIO configuration of SOC

2022-06-28 07:40:00 【youbin2013】

SOC Of GPIO To configure

1 GPIO working principle

Soc Co integration 40 Two way GPIO, Every way GPIO The input / output direction of is controlled by the direction register , The input / output level value of the pin is saved in the corresponding input / Output value register . The external signal is input to the internal and then synchronized by three stages , refilter , The filter width can be configured through the corresponding filter width register , The filter width range supported is 0~63 Two system clock cycles . If the pulse width of the input signal can reach the set value of the register , Is allowed to be sampled , Otherwise it will be regarded as “ skin needling ” Filter .GPIO The output adopts register output , By writing GPIO The output value register directly outputs the signal to the outside through the pin .GPIO The structure of the module is shown in the figure 1 Shown :

chart 1 gpio structure

Be careful : There is a conflict between the data manual and the actual use , In the manual GPIO Yes 60 However, in the actual use process, only 40 road ,40 road GPIO There are two sets of registers for configuration ,0-9 road GPIO Using registers 1 Of 22-31 Bits to configure , after 30 With registers 2 Of 0-29 Bits to configure .

2 The configuration process

GPIO The configuration process is as follows :

- Enable the whole GPIO Peripheral clock , Configure peripheral clock registers ( The address is 0x40C00000) Of 24 Position as 1.

- The configuration pin is multiplexed to GPIO, Configure pin multiplexing register ( The address is 0x40C00004) Of the 2 Position and number 3 Position as 0x0, Both the interrupt multiplexing pin and the extended memory pin are configured as GPIO function .

- To configure GPIO Mode register GPIOEN device , Make corresponding IO Work for GPIO Mouth mode , If GPIO The number is less than 10 Then configure GPIOEN1 Corresponding IO The value of mouth is 0x1, If GPIO Number is greater than or equal to 10 Then configure GPIOEN2 Corresponding IO The value of mouth is 0x1.

- To configure GPIO Direction register GPIODIR, Configure its corresponding IO Is the port input or output , The corresponding bit is 1 Indicative output , The corresponding bit is 0 Indicates input .

- Set output IO The level of the port , To configure GPIO Output level register GPIOODR The corresponding bit of is 1 Indicates the output high level , The corresponding bit is 0 Indicates that the output is low .

- Get input IO Level value of port , obtain GPIO Input level register GPIOIDR The value of the corresponding bit of , if 1 Indicates that a high level is obtained , If 0 Indicates that the low level is obtained .

3 Data structure encapsulation

according to GPIO The distribution of module register addresses in the memory allocation graph , Define its address as an integer macro definition , The register is defined as the structural union of each functional bit field . In this way, the integer address is converted to the structural union pointer of the register , You can write the underlying driver through the register bit field , chart 1 Represents the definition and type conversion of the macro definition register , chart 2 Represents the register structure union definition .

chart 1

chart 2

边栏推荐

- Application of XOR. (extract the rightmost 1 in the number, which is often used in interviews)

- hack the box:RouterSpace题解

- How to configure DDR3 of dm8148

- Resizing node of rediscluster cluster cluster mode

- MMR rearrangement (similarity is calculated by editing distance and repeatability)

- Mysql8.0和Mysql5.0访问jdbc连接

- The practice of traffic and data isolation in vivo Reviews

- kubelet垃圾(退出的容器和未使用的镜像)回收源码分析

- 剑指Offer||:链表(简单)

- Analyze 5 indicators of NFT project

猜你喜欢

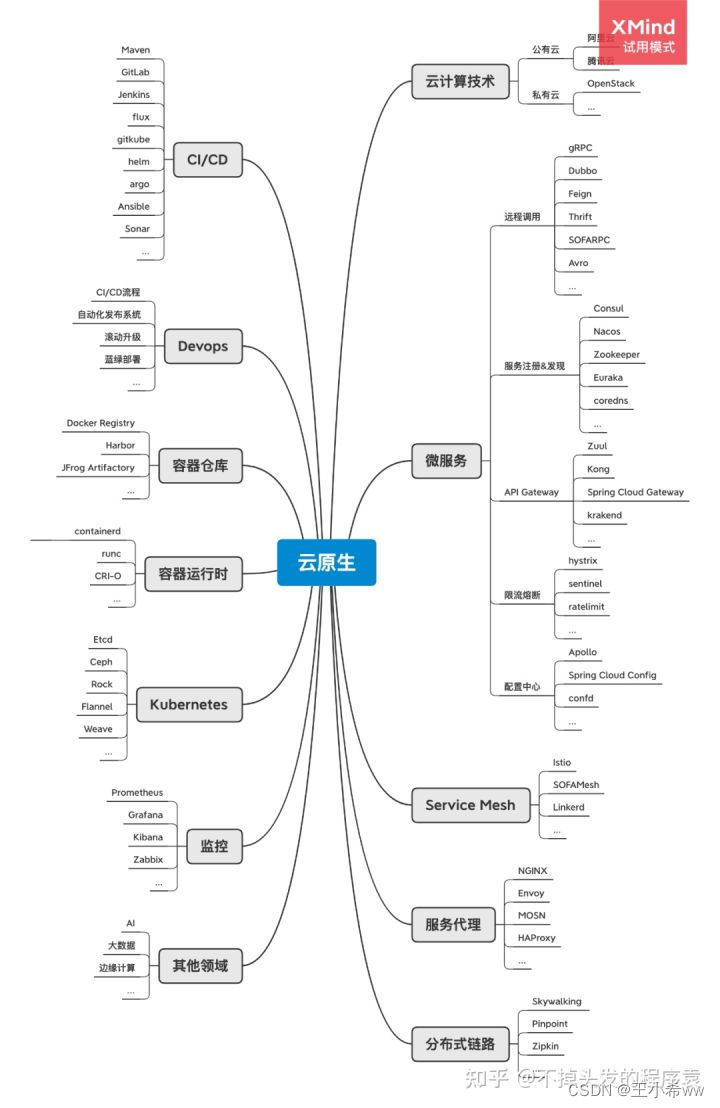

云原生(待更新)

Rediscluster cluster mode capacity expansion node

linux下修改mysql端口号

PLC -- Notes

分析 NFT 项目的 5 个指标

Jetpack - defects of livedata component and Countermeasures

The practice of traffic and data isolation in vivo Reviews

kubernetes集群命令行工具kubectl

Alibaba cloud server creates snapshots and rolls back disks

Devtools implementation principle and performance analysis practice

随机推荐

Redis implements distributed locks

Practice and exploration of vivo live broadcast application technology

云原生(待更新)

ABAP skill tree

Modifying MySQL user name root under Linux

Practice of traffic recording and playback in vivo

Investment transaction and settlement of the fund

大型项目中的Commit Message规范化控制实现

Cloud native (to be updated)

Code submission specification

HJ成绩排序

Spark 离线开发框架设计与实现

Leetcode learning records

hack the box:RouterSpace题解

Source code analysis of kubernetes' process of deleting pod

Is it safe to open an account on Dongfang fortune

linux下修改mysql用户名root

How to configure DDR3 of dm8148

异或的应用。(提取出数字中最右侧的1,面试中经常用的到)

Implementation of commit message standardized control in large projects