当前位置:网站首页>[conception de la machine d'état] Moore, Mealy State Machine, Three - stage, Two - stage, one - stage State Machine Writing Specification

[conception de la machine d'état] Moore, Mealy State Machine, Three - stage, Two - stage, one - stage State Machine Writing Specification

2022-06-28 23:15:00 【Linest - 5】

Table des matières

Introduction à la machine d'état

Processus de conception de la machine d'état

Conception de la machine d'état:3 Segment(Recommandations)

Modification de la machine d'état :2 Segment

Modification de la machine d'état :1 Segment(Soyez prudent.)

Modification de la machine d'état :Moore Type

Introduction à la machine d'état

Machine à l'état fini(Finite-State Machine,FSM),Machine d'état abrégée,.Est un modèle mathématique qui représente des états finis et des comportements tels que les transitions et les actions entre ces états. La machine d'état n'est pas seulement un outil de description de circuit , C'est aussi une façon de penser. , Au niveau du système et dans la conception des circuits RTL Les niveaux sont largement utilisés .

Tout le monde dit que la machine d'état est FPGA L'âme du design , Voir son importance ,In Verilog Dans la conception, La machine d'état peut en fait être équivalente à if Déclarations et case Déclarations, Mais parce que dans certains cas, , Les états sont nombreux et complexes , C'est très gênant de sauter dans tous les états. ,Alors... La conception générale de la machine d'état est une méthode fiable et pratique .

Le Code de machine d'état canonique peut grandement améliorer l'efficacité de la conception , Réduire le temps de débogage tout en réduisant la possibilité d'erreurs d'état , Pour concevoir un système robuste .

Lors de la conception de la machine d'état , Il est préférable de satisfaire aux exigences suivantes: :

- Méthode générale de conception, Conçu pour des machines d'état simples ou complexes ;

- Les étapes sont claires et faciles à comprendre , Une seule question par étape ;

- Code de machine d'état strict , Pas facile à faire des erreurs;

- La machine d'état conçue a une structure simple et stable .

Type de machine d'état

Verilog La machine à l'état moyen est principalement utilisée pour la conception de la logique de synchronisation , L'état d'un circuit séquentiel capable de passer d'un état fini à l'autre selon les besoins et les règles . La direction de commutation de l'état dépend non seulement des valeurs d'entrée individuelles , Dépend également de l'état actuel . Les machines d'état peuvent être divisées en deux catégories :

- Moore Machine d'état

- Mealy Machine d'état

Moore Type de machine d'état

Moore La sortie de la machine d'état type n'est liée qu'à l'état actuel , Indépendant de l'entrée courante .

La sortie restera stable pendant un cycle d'horloge complet , Même si le signal d'entrée change , La production ne changera pas non plus . L'effet de l'entrée sur la sortie ne se reflète qu'au prochain cycle d'horloge .Et ça aussi. Moore Une caractéristique importante de la machine d'état type : Les entrées et les sorties sont isolées .

Mealy Type de machine d'état

Mealy Sortie de la machine d'état type , Non seulement par rapport à l'état actuel , Dépend également du signal d'entrée actuel .

Mealy La sortie de la machine d'état type est modifiée immédiatement après le changement du signal d'entrée , Et le changement d'entrée peut se produire dans n'importe quel état du cycle d'horloge .Donc,, Dans la même logique ,Mealy La réponse de sortie de la machine d'état type à l'entrée sera Moore La machine d'état de type a un cycle d'horloge plus tôt .

Processus de conception de la machine d'état

Tracer le diagramme de transfert d'état en fonction des exigences de conception , Déterminer le type de machine d'état d'utilisation , Divers signaux d'entrée et de sortie doivent être marqués simultanément. , Plus facile à programmer .Le plus souvent utilisé est Mealy Type 3 Machine d'état segmentaire, Le processus de conception de la machine d'état est illustré ci - dessous par un exemple concret de conception d'un distributeur automatique .

Distributeur automatique

Les fonctions du distributeur automatique sont décrites comme suit: :

Prix unitaire des boissons 2 Yuan, Le distributeur ne peut accepter que 0.5 Yuan、1 La pièce de yuan. Envisager la mise à zéro et l'expédition . Le processus de mise en pièces et d'expédition est effectué une seule fois , Il n'y aura pas d'entrée unique de plusieurs pièces ou d'expédition unique de plusieurs bouteilles de boissons . Chaque tour du distributeur accepte la monnaie 、Expédition、 Une fois le changement terminé , Pour entrer dans un nouvel état de vente automatique .

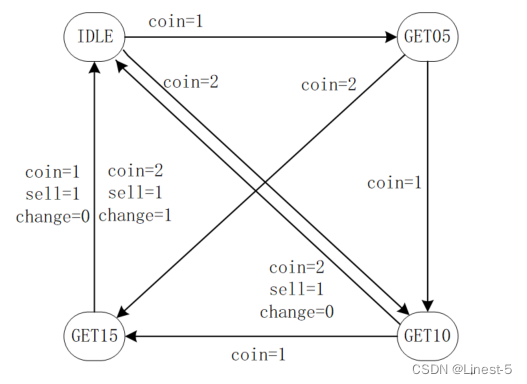

Le diagramme de transfert de l'état de fonctionnement du distributeur est le suivant: ,Contient des entrées、 État du signal de sortie .

Parmi eux,coin = 1 Le représentant a donné son avis. 0.5 Pièces de monnaie,coin = 2 Le représentant a donné son avis. 1 Pièces de monnaie.

Conception de la machine d'état:3 Segment(Recommandations)

La machine d'état est conçue comme suit: :

- (0) Tout d'abord,, Déterminer le Code de la machine d'état en fonction du nombre de machines d'état . Assigner une valeur au registre d'état en utilisant le codage ,Meilleure lisibilité du Code.

- (1) Premier segment de la machine d'état ,Logique temporelle,Affectation non bloquante, État du registre de passage .

- (2) Deuxième section de la machine d'état ,Logique combinatoire,Affectation des blocs, Selon l'état actuel et l'entrée actuelle , Déterminer l'état de la prochaine machine d'état .

- (3) Troisième section de la machine d'état ,Logique temporelle,Affectation non bloquante,Parce que oui. Mealy Type de machine d'état, Selon l'état actuel et l'entrée actuelle , Déterminer le signal de sortie .

Exemple

module vending_machine_p3 (

input clk ,

input rstn ,

input [1:0] coin ,

output [1:0] change , //Change.

output sell //Boissons de sortie

);

//machine state decode

parameter IDLE = 3'd0 ;

parameter GET05 = 3'd1 ;

parameter GET10 = 3'd2 ;

parameter GET15 = 3'd3 ;

reg [2:0] st_next ;

reg [2:0] st_cur ;

reg [1:0] change_r ;

reg sell_r ;

// Machine d'état du premier segment ,Logique temporelle Affectation non bloquante

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

st_cur <= 'b0 ;

end

else begin

st_cur <= st_next ;

end

end

// Machine d'état du deuxième segment ,Logique combinatoire Affectation des blocs

always @(*) begin

st_next = st_cur ; // Si les options conditionnelles ne sont pas prises en compte , Peut assigner l'annulation initiale latch

case(st_cur)

IDLE:

case (coin)

2'b01: st_next = GET05 ;

2'b10: st_next = GET10 ;

default: st_next = IDLE ;

endcase

GET05:

case (coin)

2'b01: st_next = GET10 ;

2'b10: st_next = GET15 ;

default: st_next = GET05 ;

endcase

GET10:

case (coin)

2'b01: st_next = GET15 ;

2'b10: st_next = IDLE ;

default: st_next = GET10 ;

endcase

GET15:

case (coin)

2'b01,2'b10:

st_next = IDLE ;

default: st_next = GET15 ;

endcase

default: st_next = IDLE ;

endcase

end

// Machine d'état du troisième segment ,Logique temporelle Affectation non bloquante

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

else begin

case (st_cur)

IDLE:

begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

GET05:

begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

GET10:

begin

if (coin ==2'd2) begin

change_r <= 2'b0 ;

sell_r <= 1'b1 ;

end

else begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

end

GET15:

begin

if (coin ==2'h1) begin

change_r <= 2'b0 ;

sell_r <= 1'b1 ;

end

else if (coin == 2'h2) begin

change_r <= 2'b1 ;

sell_r <= 1'b1 ;

end

else begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

end

default:

begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

endcase

end

end

assign sell = sell_r ;

assign change = change_r ;

endmoduletestbench Conçu comme suit:. Dans la simulation, 4 Scénario,Respectivement.:

case1 Correspond à une entrée continue 4 - Oui. 5 Pièce d'angle;case2 Correspondant à 1 Yuan - 5 Angle - 1 Ordre de placement des dollars ;case3 Correspondant à 5 Angle - 1 Yuan - 5 Ordre de mise des coins ;case4 Correspond à la continuité 3 - Oui. 5 Puis un coin. 1 Ordre de placement des dollars .

Exemple

`timescale 1ns/1ps

module test ;

reg clk;

reg rstn ;

reg [1:0] coin ;

wire [1:0] change ;

wire sell ;

//clock generating

parameter CYCLE_200MHz = 10 ;

always begin

clk = 0 ; #(CYCLE_200MHz/2) ;

clk = 1 ; #(CYCLE_200MHz/2) ;

end

//motivation generating

reg [9:0] buy_oper ;

initial begin

buy_oper = 'h0 ;

coin = 2'h0 ;

rstn = 1'b0 ;

#8 rstn = 1'b1 ;

@(negedge clk) ;

//case(1) 0.5 -> 0.5 -> 0.5 -> 0.5

#16 ;

buy_oper = 10'b00_0101_0101 ;

repeat(5) begin

@(negedge clk) ;

coin = buy_oper[1:0] ;

buy_oper = buy_oper >> 2 ;

end

//case(2) 1 -> 0.5 -> 1, taking change

#16 ;

buy_oper = 10'b00_0010_0110 ;

repeat(5) begin

@(negedge clk) ;

coin = buy_oper[1:0] ;

buy_oper = buy_oper >> 2 ;

end

//case(3) 0.5 -> 1 -> 0.5

#16 ;

buy_oper = 10'b00_0001_1001 ;

repeat(5) begin

@(negedge clk) ;

coin = buy_oper[1:0] ;

buy_oper = buy_oper >> 2 ;

end

//case(4) 0.5 -> 0.5 -> 0.5 -> 1, taking change

#16 ;

buy_oper = 10'b00_1001_0101 ;

repeat(5) begin

@(negedge clk) ;

coin = buy_oper[1:0] ;

buy_oper = buy_oper >> 2 ;

end

end

//(1) mealy state with 3-stage

vending_machine_p3 u_mealy_p3 (

.clk (clk),

.rstn (rstn),

.coin (coin),

.change (change),

.sell (sell)

);

//simulation finish

always begin

#100;

if ($time >= 10000) $finish ;

end

endmodule Les résultats de la simulation sont les suivants::

Comme le montre la figure, Signal représentant l'action d'expédition sell Peut normalement être élevé après la fin de la pièce , Et le signal qui représente l'action de mise à zéro change Peut également produire un signal de mise à zéro correct en fonction de la scène de pièce d'entrée .

Modification de la machine d'état :2 Segment

Oui. 3 Machine d'état segmentaire 2、3 Fusion de la description du segment ,Les autres parties restent inchangées, La machine d'état devient 2 Description du segment .

Modifier comme suit::

Exemple

reg [1:0] change_r ;

reg sell_r ;

always @(*) begin

case(st_cur)

IDLE: begin

change_r = 2'b0 ;

sell_r = 1'b0 ;

case (coin)

2'b01: st_next = GET05 ;

2'b10: st_next = GET10 ;

default: st_next = IDLE ;

endcase

end

GET05: begin

change_r = 2'b0 ;

sell_r = 1'b0 ;

case (coin)

2'b01: st_next = GET10 ;

2'b10: st_next = GET15 ;

default: st_next = GET05 ;

endcase

end

GET10:

case (coin)

2'b01: begin

st_next = GET15 ;

change_r = 2'b0 ;

sell_r = 1'b0 ;

end

2'b10: begin

st_next = IDLE ;

change_r = 2'b0 ;

sell_r = 1'b1 ;

end

default: begin

st_next = GET10 ;

change_r = 2'b0 ;

sell_r = 1'b0 ;

end

endcase

GET15:

case (coin)

2'b01: begin

st_next = IDLE ;

change_r = 2'b0 ;

sell_r = 1'b1 ;

end

2'b10: begin

st_next = IDLE ;

change_r = 2'b1 ;

sell_r = 1'b1 ;

end

default: begin

st_next = GET15 ;

change_r = 2'b0 ;

sell_r = 1'b0 ;

end

endcase

default: begin

st_next = IDLE ;

change_r = 2'b0 ;

sell_r = 1'b0 ;

end

endcase

endInstancier le nouveau module modifié ci - dessus à 3 Segmental testbench Peut simuler ,Les résultats sont les suivants::

Comme le montre la figure, Signal d'expédition sell Et Signal de mise à zéro change Par rapport à 3 La sortie de la machine d'état de segment a un cycle d'horloge avancé , Ceci est dû au fait que les signaux de sortie sont tous des assignations de blocage .

Comme indiqué dans le cercle rouge , Les signaux de sortie ont des impulsions d'interférence , C'est parce que les signaux d'entrée sont asynchrones , Et le signal de sortie est une sortie Logique combinatoire , Pas de lecteur d'horloge .

Dans la pratique, Si les signaux d'entrée sont synchronisés avec l'horloge , Cette impulsion de brouillage ne se produira pas . S'il s'agit d'un signal d'entrée asynchrone , Le signal doit d'abord être synchronisé .

Modification de la machine d'état :1 Segment(Soyez prudent.)

Oui. 3 Machine d'état segmentaire 1、 2、3 Fusion de la description du segment , La machine d'état devient 1 Description du segment .

Modifier comme suit::

Exemple

reg [1:0] change_r ;

reg sell_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

st_cur <= 'b0 ;

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

else begin

case(st_cur)

IDLE: begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

case (coin)

2'b01: st_cur <= GET05 ;

2'b10: st_cur <= GET10 ;

endcase

end

GET05: begin

case (coin)

2'b01: st_cur <= GET10 ;

2'b10: st_cur <= GET15 ;

endcase

end

GET10:

case (coin)

2'b01: st_cur <= GET15 ;

2'b10: begin

st_cur <= IDLE ;

sell_r <= 1'b1 ;

end

endcase

GET15:

case (coin)

2'b01: begin

st_cur <= IDLE ;

sell_r <= 1'b1 ;

end

2'b10: begin

st_cur <= IDLE ;

change_r <= 2'b1 ;

sell_r <= 1'b1 ;

end

endcase

default: begin

st_cur <= IDLE ;

end

endcase // case (st_cur)

end

endInstancier le nouveau module modifié ci - dessus à 3 Segmental testbench Peut simuler ,Les résultats sont les suivants::

Comme le montre la figure, Signaux de sortie et 3 La machine d'état de segment est entièrement cohérente .

1 L'inconvénient des machines d'état segmentées est qu'il y a beaucoup de logique qui s'assemblent , Entretien ultérieur difficile . Lorsque la machine d'état et le signal de sortie sont faibles , Vous pouvez essayer cette description .

Modification de la machine d'état :Moore Type

Si vous utilisez Moore Description du flux de travail du distributeur , Il faut donc en ajouter d'autres. 2 Codes d'état ,Pour décrire Mealy Signal d'entrée à la sortie de la machine d'état et état de la machine d'état .

3 Segment Moore Distributeur automatique décrit par la machine d'état type Verilog Les codes sont les suivants::

Exemple

module vending_machine_moore (

input clk ,

input rstn ,

input [1:0] coin ,

output [1:0] change ,

output sell

);

parameter IDLE = 3'd0 ;

parameter GET05 = 3'd1 ;

parameter GET10 = 3'd2 ;

parameter GET15 = 3'd3 ;

parameter GET20 = 3'd4 ;

parameter GET25 = 3'd5 ;

reg [2:0] st_next ;

reg [2:0] st_cur ;

//(1) state transfer

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

st_cur <= 'b0 ;

end

else begin

st_cur <= st_next ;

end

end

always @(*) begin //all case items need to be displayed completely

case(st_cur)

IDLE:

case (coin)

2'b01: st_next = GET05 ;

2'b10: st_next = GET10 ;

default: st_next = IDLE ;

endcase

GET05:

case (coin)

2'b01: st_next = GET10 ;

2'b10: st_next = GET15 ;

default: st_next = GET05 ;

endcase

GET10:

case (coin)

2'b01: st_next = GET15 ;

2'b10: st_next = GET20 ;

default: st_next = GET10 ;

endcase

GET15:

case (coin)

2'b01: st_next = GET20 ;

2'b10: st_next = GET25 ;

default: st_next = GET15 ;

endcase

GET20: st_next = IDLE ;

GET25: st_next = IDLE ;

default: st_next = IDLE ;

endcase

end

reg [1:0] change_r ;

reg sell_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

else if (st_cur == GET20 ) begin

sell_r <= 1'b1 ;

end

else if (st_cur == GET25) begin

change_r <= 2'b1 ;

sell_r <= 1'b1 ;

end

else begin

change_r <= 2'b0 ;

sell_r <= 1'b0 ;

end

end

assign sell = sell_r ;

assign change = change_r ;

endmodule

Modifier comme indiqué ci - dessus Moore Machine d'état instanciée à 3 Segmental testbench Peut simuler ,Les résultats sont les suivants::

Comme le montre la figure, Signaux de sortie et Mealy Type 3 La machine d'état segmentée retarde un cycle d'horloge par rapport à , C'est parce qu'un délai d'un cycle d'horloge est nécessaire pour entrer dans la nouvelle machine d'état d'encodage .En ce moment, L'assignation de la sortie à une valeur non bloquante retardera le signal de sortie final d'un cycle d'horloge .C'est la même chose. Moore Caractéristiques de la machine d'état type .

Lors de l'attribution du signal de sortie , Assigner une valeur avec un bloc , Vous pouvez avancer d'un cycle d'horloge .

La logique de sortie est modifiée comme suit: .

Exemple

reg [1:0] change_r ;

reg sell_r ;

always @(*) begin

change_r = 'b0 ;

sell_r = 'b0 ; //not list all condition, initializing them

if (st_cur == GET20 ) begin

sell_r = 1'b1 ;

end

else if (st_cur == GET25) begin

change_r = 2'b1 ;

sell_r = 1'b1 ;

end

endLes résultats de la simulation de l'assignation du blocage du signal de sortie sont les suivants: :

Comme le montre la figure, Le signal de sortie a été 3 Segment Mealy La machine d'état de type est cohérente .

边栏推荐

- Leetcode 324 Swing sort II [tri double pointeur] le chemin du leetcode pour l'héroding

- [matlab]函数定义与使用

- Count the number of arrays with pointers

- Finally, someone explained the cloud native architecture

- Chapter III processor scheduling exercise

- MSCI 2022 market classification assessment

- TDD案例实战

- Wave picking of WMS warehouse management system module

- 设计电商秒杀系统

- 网上注册股票开户很困难么?在线开户是安全么?

猜你喜欢

Fanuc robot_ Introduction to Karel programming (2)_ Usage of general IO signal

The picture display on the left of the two column layout is determined by the content height on the right

How to solve the problem of desktop without sound

Progress of dbnn experiment

![LeetCode 324 摆动排序 II[排序 双指针] HERODING的LeetCode之路](/img/41/b8ba8d771b7224eac1cc8c54fe9d29.png)

LeetCode 324 摆动排序 II[排序 双指针] HERODING的LeetCode之路

Master the usage of const

![[mathematical modeling] fmincon() function of MATLAB nonlinear programming](/img/fc/46949679859b1369fcc83d0d8b637c.png)

[mathematical modeling] fmincon() function of MATLAB nonlinear programming

Wave picking of WMS warehouse management system module

Finally, someone explained the cloud native architecture

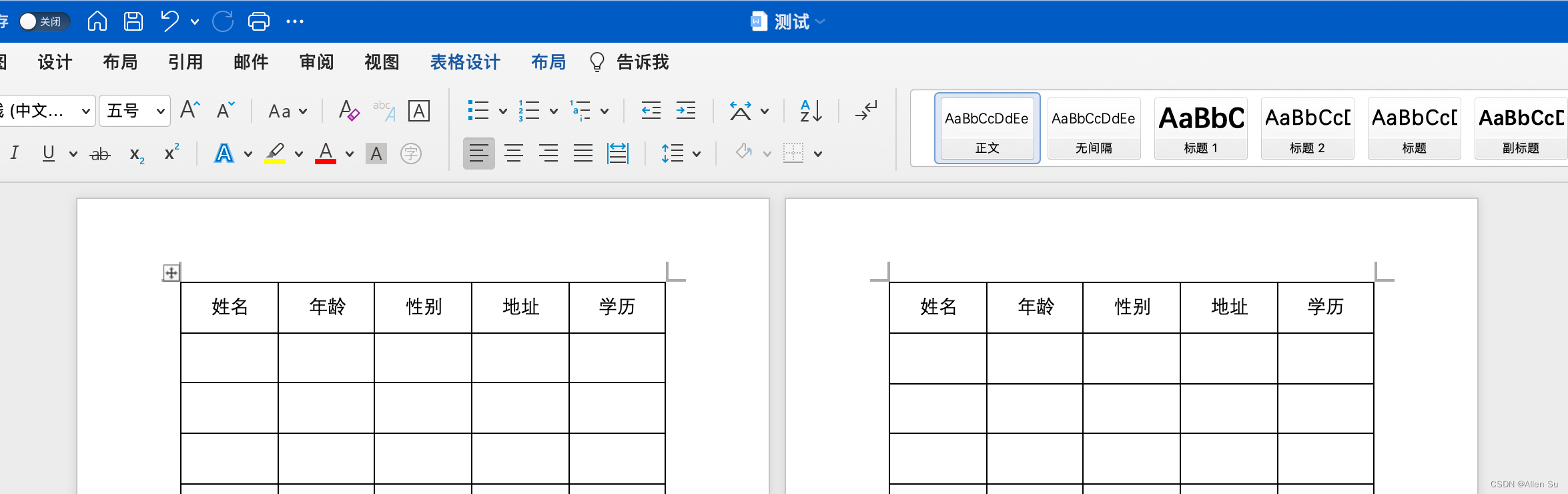

【Word 教程系列第 2 篇】Word 中如何设置每页的表格都有表头

随机推荐

LINQ linked table query

笔记

Do you know all the wonderful functions of the vlookup function?

[Chapter 2 of word tutorial series] how to set the table on each page to have a header in word

Is it safe to open a stock account by mobile phone?

TDD and automated testing

Encounter with avita 11: long lost freshness under strong product power

Google Earth engine (GEE) -- crop extraction and analysis using sentinel-2 data

Implementation of go language plug-in platform

SqlServer复习

【深度学习】(2) Transformer 网络解析,代码复现,附Pytorch完整代码

他原来是这么刷题的!

Cs5463 code module analysis (including download link)

Go language - reflect

C語言-單詞分析解析

The Best of Many Worlds_ Dual Mirror Descent for Online Allocation Problems

【深度学习】(3) Transformer 中的 Encoder 机制,附Pytorch完整代码

小样本利器2.文本对抗+半监督 FGSM & VAT & FGM代码实现

Cmake tutorial (I)

在线SQL转HTMLTable工具