当前位置:网站首页>从底层结构开始学习FPGA----RAM IP的定制与测试

从底层结构开始学习FPGA----RAM IP的定制与测试

2022-07-01 05:31:00 【孤独的单刀】

文章目录

系列目录与传送门

在定制一个RAM IP核之前,强烈建议您先阅读:从底层结构开始学习FPGA----RAM IP核及关键参数介绍。在这篇文章中,已经对RAM IP核的各个关键因素做了详细的讲解。

1、RAM IP的定制

- 在新建一个工程后, 点击IP Catalog

- 点击后会出现 IP Catalog 页面,在 IP 核的搜索框中搜索 block

- 根据筛选,双击选择RAM & ROM 核“Block Memory Generator”

①、第一页

②、第二页

③、第三页

④、第四页

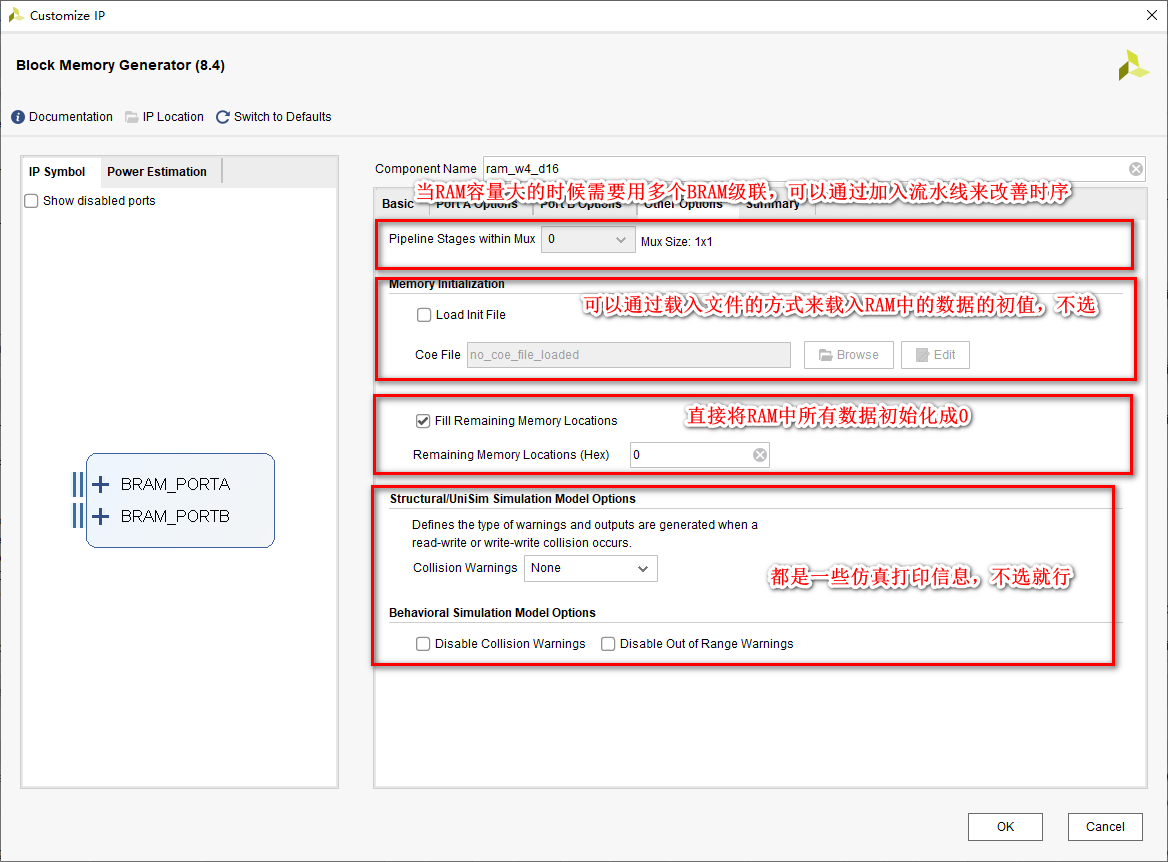

⑤、第五页

2、RAM IP的例化与仿真测试

2.1、例化一个RAM IP核

按上述步骤生成IP后,复制 IP核 自带的例化模板。

然后在我们的RTL代码中,例化生成一个4*16的SDP RAM。

该RTL不做其他功能,只例化RAM即可。

module test(

input clk, //输入时钟

input [3:0] data_in, //输入数据

input en_wr, //写使能信号

input en_rd, //读使能信号

input [3:0] addr_wr, //写地址

input [2:0] addr_rd, //读地址

input we_wr, //写使能

output [7:0] data_out //输出数据

);

//例化RAM IP核

ram_w4_d16 ram_w4_d16_inst (

//端口A--写端口

.clka (clk),

.ena (en_wr),

.wea (we_wr),

.addra (addr_wr),

.dina (data_in),

//端口B--读端口

.clkb (clk),

.enb (en_rd),

.addrb (addr_rd),

.doutb (data_out)

);

endmodule

2.2、仿真测试

写个testbench,对RAM IP测试一下。

测试行为:先往地址0-15写入数据0-15,然后从地址0-7读出数据(因为读数据位宽是写数据位宽的2倍,所以读数据一次会读出2个写地址的数据)。

`timescale 1ns / 1ns

module tb_test();

reg clk;

reg [3:0] data_in;

reg en_wr;

reg en_rd;

reg [3:0] addr_wr;

reg [2:0] addr_rd;

reg we_wr;

wire [7:0] data_out;

initial begin

clk = 0;

en_wr = 0;en_rd = 0;we_wr = 0;

data_in = 4'd0;

addr_wr = 4'd0;

addr_rd = 3'd0;

#110

en_wr = 1;we_wr = 1; //开始写入数据

repeat(15) begin //向地址0-15写入数据0-15

#10

data_in = data_in + 1;

addr_wr = addr_wr + 1;

end

#10

en_wr = 0; //停止写入数据

en_rd = 1;we_wr = 0; //开始读出数据

repeat(10) begin //从地址0-7读数据

#10 addr_rd = addr_rd + 1;

end

en_rd = 0; //停止读出数据

#20 $finish; //结束仿真

end

always #5 clk = ~clk; //生成时钟,周期10ns

//例化被测模块test

test test_inst(

.clk (clk ),

.data_in (data_in ),

.en_wr (en_wr ),

.en_rd (en_rd ),

.addr_wr (addr_wr ),

.addr_rd (addr_rd ),

.we_wr (we_wr ),

.data_out (data_out )

);

endmodule使用vivado自带的仿真工具simulator运行仿真,仿真结果如下:

符合预期结果。

3、总结与参考

- 可以看到RAM IP的定制还是挺简单的,在了解其参数后,可以很快、很方便地例化一个自己需要的RAM模块。

- 创作不易,如果本文对您有帮助,还请多多点赞、评论和收藏。您的支持是我持续更新的最大动力!

边栏推荐

- eBPF Cilium实战(2) - 底层网络可观测性

- [RootersCTF2019]babyWeb

- QT waiting box production

- QDataStream的簡單讀寫驗證

- [RootersCTF2019]babyWeb

- And search: the suspects (find the number of people related to the nth person)

- [SRS] use of Vhost isolated stream: push / pull Stream Address

- Use and principle of wait notify

- printk 调试总结

- 2022.6.30-----leetcode.1175

猜你喜欢

Txncoordsender of cockroachdb distributed transaction source code analysis

Actual combat: gateway api-2022.2.13

![[RootersCTF2019]babyWeb](/img/b4/aa8f8e107a9dacbace72d4717b1834.png)

[RootersCTF2019]babyWeb

![[excel] column operation, which performs specific column for data in a cell, such as text division by comma, colon, space, etc](/img/c8/e3e31ad9ef214d97228cb501dd752f.jpg)

[excel] column operation, which performs specific column for data in a cell, such as text division by comma, colon, space, etc

LRU cache for leveldb source code analysis

LevelDB源码分析之memtable

Set集合详细讲解

Memtable for leveldb source code analysis

Redis database deployment and common commands

el-cascader回显失败;el-cascader回显不出来

随机推荐

Redis数据库的部署及常用命令

mysql 将毫秒数转为时间字符串

Simple implementation of database connection pool

eBPF Cilium实战(2) - 底层网络可观测性

[excel] column operation, which performs specific column for data in a cell, such as text division by comma, colon, space, etc

[RootersCTF2019]babyWeb

数字金额加逗号;js给数字加三位一逗号间隔的两种方法;js数据格式化

Numeric amount plus comma; JS two methods of adding three digits and a comma to numbers; JS data formatting

Global and Chinese market of search engine optimization (SEO) software 2022-2028: Research Report on technology, participants, trends, market size and share

Fiber Bragg grating (FBG) notes [1]: waveguide structure and Bragg wavelength derivation

[ffmpeg] [reprint] image mosaic: picture in picture with wheat

C WPF uses dockpanel to realize screenshot box

Simple read / write verification of qdatastream

0xc000007b应用程序无法正常启动解决方案(亲测有效)

Typeorm framework

Precautions for use of conductive slip ring

Redis database deployment and common commands

Use and principle of reentrantlock

Day 05 - file operation function

JDBC常见面试题