当前位置:网站首页>Vivado 错误代码 [DRC PDCN-2721] 解决

Vivado 错误代码 [DRC PDCN-2721] 解决

2022-06-26 12:37:00 【在路上,正出发】

不只是解决 error ,更多是记录和总结。加油!

目录

说明

VIVADO IDE :2021.1

操作系统:WIN 10

FPGA芯片系列:Kintex 7 (xc7k410tffg900-2L)

问题描述

最近在调试一块信号处理板卡,板载芯片为XILINX的7系列FPGA(xc7k410tffg900-2L)。MGT BANK的参考时钟是156.25MHz的差分时钟,是由CDCM6208时钟芯片的输出来驱动。CDCM6208配置完成后,首要的工作便是验证其产生的156.26MHz差分时钟有没有真正进入FPGA 的MGT BANK。具体验证步骤如下:

第一步:使用 原语IBUFDS_GTE2将MGT BANK 的差分参考时钟引入并转为同频率的单端时钟。

在代码里面进行例化:

IBUFDS_GTE2 #(

.CLKCM_CFG("TRUE"), // Refer to Transceiver User Guide

.CLKRCV_TRST("TRUE"), // Refer to Transceiver User Guide

.CLKSWING_CFG(2'b11) // Refer to Transceiver User Guide

)

IBUFDS_GTE2_inst (

.O(O_CLK_156M25), // 输出156.25M的单端时钟

.ODIV2(), // 该端口可闲置不用

.CEB(1'b0), // 该端口低电平输入有效 要一直给 0

.I (I_CLK_156M25_P), // BANK 参考时钟 输入端口 P

.IB(I_CLK_156M25_N) // BANK 参考时钟 输入端口 N

);第二步:将原语输出的单端时钟送入MMCM或者PLL进行分频,供系统设计使用

问题可能就是出在这里,如果不进MMCM或者PLL,可能就不会出现错误

clk_wiz_1 instance_name1

(

// Clock out ports

.clk_out1(CLK_10M), // output clk_out1

// Status and control signals

.reset(0), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(O_CLK_156M25)); // input clk_in1然后再实现的过程中就会报DRC的错误,违背了设计规则(Design Rule):

[DRC PDCN-2721] IBUFDS_GT_loads_clock_region: IBUFDS_GTE2 IBUFDS_GTE2_inst drives MMCME2_ADV instance_name1/inst/mmcm_adv_inst in a different clock region and must do so using local routing resources which may negatively affect clock performance. Use CLOCK_DEDICATED_ROUTE set to FALSE to indicate this is intended.

错误的大致原因就是IBUFDS_GTE2原语出来的时钟区域和所驱动的MMCM或PLL的时钟区域不一致。注意,个人认为此处的时钟区域的概念是物理层面的时钟资源分布的区域,有别于STA(静态时序分析)的时钟域概念。

解决错误

其实在错误的最后已经给出了解决方法。需要在XDC文件里面做如下约束:

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets O_CLK_156M25]而后就可以无误生成比特流~

以上就是对错误 [DRC PDCN-2721] 的记录,欢迎留言交流,补充~

解决思路参考官网:官方论坛

边栏推荐

- Adobe Acrobat阻止30款安全软件查看PDF文件 或存在安全风险

- Less than 40 lines of code to create a blocprovider

- File remote synchronization and backup artifact Rsync

- KITTI Tracking dataset whose format is letf_top_right_bottom to JDE normalied xc_yc_w_h

- "Pinduoduo and short video speed version", how can I roast!

- Spark-day01- get started quickly

- 7-3 最低通行费

- NoSQL mongodb - 04 mongodb database and web service combination case

- Iframe usage and contentwindow, parent and PostMessage communication methods

- 机组实践实验8——使用CMStudio设计基于基本模型机微程序指令(1)

猜你喜欢

NoSQL mongodb - 02 mongodb server installation, mongodb shell, basic concepts and visualization tools

Examples of how laravel uses with preload (eager to load) and nested query

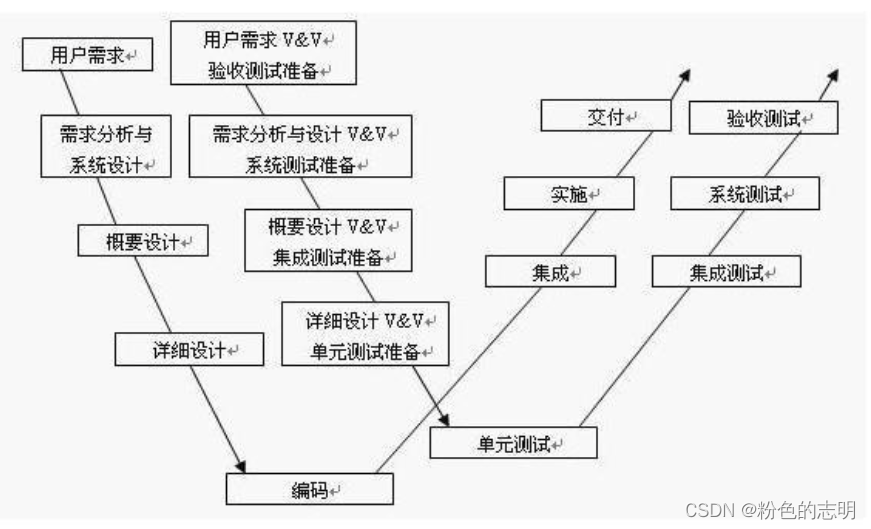

软件测试 - 概念篇

Software testing - Fundamentals

goto语句实现关机小程序

Xiaobai lazy special-win10-win11 one click installation version

Spark-day03-core programming RDD operator

Splunk iowait 报警的解决

深度解析当贝盒子B3、腾讯极光5S、小米盒子4S之间的区别

PHP uses laravel pay component to quickly access wechat jsapi payment (wechat official account payment)

随机推荐

Spark-day02-core programming-rdd

几行代码就能实现复杂的 Excel 导入导出,这个工具类真心强大!

Realize microservice load balancing (ribbon)

Redis learning - 04 persistence

Redis learning - 01 introduction, installation and configuration

PHP uses laravel pay component to quickly access wechat jsapi payment (wechat official account payment)

solo 博客系统的 rss 渲染失败

快手实时数仓保障体系研发实践

Spark-day03-core programming RDD operator

源码学习:AtomicInteger类代码内部逻辑

Examples of how laravel uses with preload (eager to load) and nested query

New routing file in laravel framework

imagecopymerge

ES6:Map

不到40行代码手撸一个BlocProvider

Implementing mixins scheme in applet

Laravel+gatewayworker completes the im instant messaging and file transfer functions (Chapter 4: server debugging errors)

Tiger Dao VC products are officially launched, a powerful supplement to seektiger ecology

Configuring Apache digest authentication

关于NaN的一些总结