当前位置:网站首页>SystemVerilog learning-07-class inheritance and package use

SystemVerilog learning-07-class inheritance and package use

2022-07-01 06:14:00 【Vuko-wxh】

Class inheritance

What is inheritance ?

Inheritance is a key concept of the object-oriented programming paradigm . Class is used to create user-defined types . Inheritance makes it very safe for users to use , Add or modify the behavior of the class in a non intrusive way . The process of extending a base class and generating new subclasses is called class derivation , When a class is extended and created , The derived class inherits the data members of its base class 、 Properties and methods , This is class inheritance .

The inherited class can realize the following functions :

Inherited the methods of the original class , And can be modified

Add new methods

Add a new data member

While realizing the above functions, certain rules must be met :

Subclasses inherit all data members and methods of the parent class

Subclasses can add new data members and methods

Subclasses can override data members and methods in the base class

If a method is overridden , It must maintain parameters consistent with the original definition of the base class

Subclasses can be passed through super Operator to reference methods and members in the parent class

Be declared local Data members and methods of can only be visible to themselves , Not visible to both external and subclasses ; Yes, the statement is protected Data members and methods of , Invisible to the outside , Visible to itself and subclasses .

Inheritance and subclasses

Previously defined classes Packet, You can enter — Step extension to form a new class LinkedPacket. adopt extends,LinkedPacket Inherit from its parent class Packet, Including inheriting all its members ( Variable / Method ).

class LinkedPacket extends Packet;

LinkedPacket next;

function LinkedPacket get_next();

get_next = next;

endfunction

endclass

Subclasses can inherit members of the parent class , therefore LinkedPacket The object is also a legal Packet object .

thus , The parent class handle can point to the object of the child class .

LinkedPacket lp = new;

Packet p = lp;

Handles to parent and child classes , The subclass handle can be directly assigned to the parent handle , Subclasses can have member methods with the same name as the parent class , A child class can have a member variable with the same name as the parent class .

super

super Is the member used to access the current object and its parent class . Especially if the member of the subclass has the same name as the member of the parent class , Then you need to use super Specify its parent class members to access , Instead of the default subclass member .

class Packet; // base class

integer value;

function integer delay();

delay = value * value;

endfunction

endclass

class LinkedPacket extends Packet; //derived class

integer value ;

function integer delay();

delay = super.delay ()+ value * super.value;

endfunction

endclass

Use of the bag

The definition of package

In order to make it possible to work in multiple modules ( Hardware ) Or class ( Software ) Share user-defined types between ,SV Added package (package) .

The concept of package refers to VHDL, User defined types such as class 、 Method 、 Variable 、 Structure 、 Enumeration classes can be found in package…endpackage In the definition of .

Export the contents of the package

module、interface、class You can use the content defined or declared in the package .

You can use the index of the field :: Number directly refers to .

definitions::parameter definitions::instruction_t instYou can specify to index some types defined in the package to the specified domain .

module M; import definitions::instruction_t; instruction_t inst; endmoduleThrough wildcards * To import all categories in the package into the specified domain .

module M; import definitions::*; instruction_t inst; endmoduleDistinction between packages and libraries

package This container can be used to isolate types .package The significance of is to make the software ( class 、 type 、 Such method ) Encapsulated in different domains , To isolate from the global domain .

Libraries are compiled products , Hardware ( module、interface、program) Will be compiled into the library , If you don't specify a compiler , Will be compiled into the default library . The library can accommodate hardware types , It can also accommodate software types , For example, class 、 Methods and packages .

Packages can only contain software types, such as classes 、 Methods and parameters .

reference

- Verification of West circuit department PPT

边栏推荐

猜你喜欢

FPGA - 7系列 FPGA内部结构之Clocking -02- 时钟布线资源

Distributed lock implementation

DHT11 温湿度传感器

Cjc8988 Low Power Stereo codec with 2 stereo headphone drivers

68 Cesium代码datasource加载czml

端口扫描工具对企业有什么帮助?

DHT11 temperature and humidity sensor

SystemVerilog学习-10-验证量化和覆盖率

excel動態圖錶

What if the data in the cloud disk is harmonious?

随机推荐

Database problems, how to optimize Oracle SQL query statements faster and more efficient

【网络安全工具】USB控制软件有什么用

69 Cesium代码datasource加载geojson

解决麒麟V10上传文件乱码问题

Index method and random forest to realize the information of surface water body in wet season in Shandong Province

DHT11 温湿度传感器

Kubedm builds kubenetes cluster (Personal Learning version)

skywalking集成nacos动态配置

OpenGL es: (1) origin of OpenGL es (transfer)

Differences between in and exists in MySQL

Using Baidu map to query national subway lines

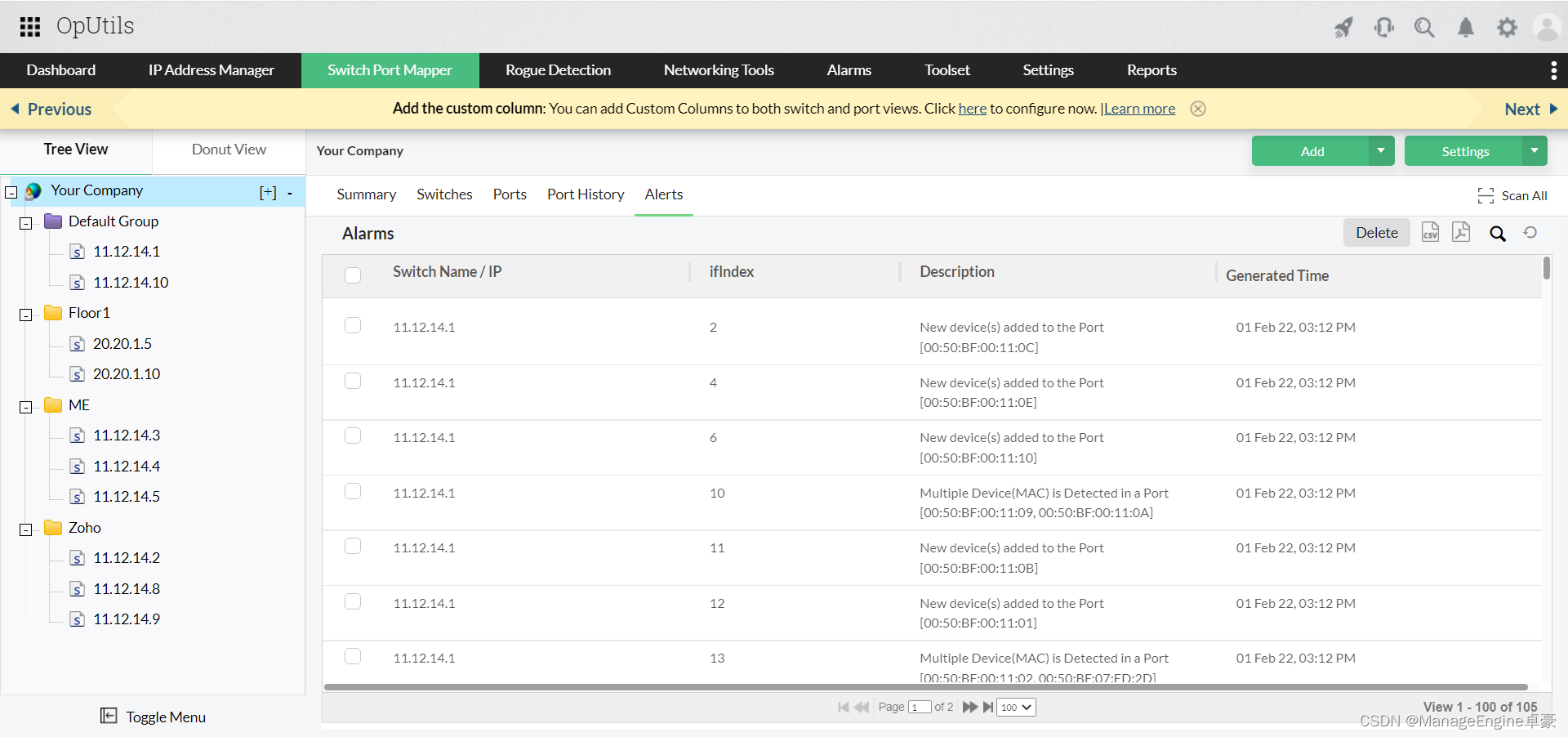

【ManageEngine】如何实现网络自动化运维

Tidb database characteristics summary

The row and column numbers of each pixel of multi-source grid data in the same area are the same, that is, the number of rows and columns are the same, and the pixel size is the same

Projects and dependencies in ABP learning solutions

数据库问题,如何优化Oracle SQL查询语句更快,效率更高

UOW of dev XPO comparison

SOE spatial analysis server MySQL and PostGIS geospatial database of Postgres anti injection attack

Talking from mlperf: how to lead the next wave of AI accelerator

Retention rate of SQL required questions