当前位置:网站首页>Stm32f04 clock configuration

Stm32f04 clock configuration

2022-07-03 09:52:00 【0725 you Guangchuan】

Clock configuration

1、 summary

F407 The internal clock of has LSI(32Hz)、HSI(16MHz)

External clock has HSE 25MHz, It is more stable to use an external clock .

use HSE The clock configuration system clock is as follows

25Mhz, adopt PLL frequency doubling , As PllClk and PLL48CLK The clock ,(m The frequency division factor is generally HSE size : Configure as input VCO by 1MHz,XN Frequency doubling is the output VCO =336Mhz, Through the frequency division factor p(=2) and R(=7) Provide clock for external bus ,ABB(HCLK)=168,APB1 Bus is 42Hz、APB2 Bus is 84Hz, The timer clock is APB Bus clock 2 times ,)

2、 Clock configuration summary

/*

- Use HSE when , Steps to set the system clock

- 1、 Turn on HSE , And wait for HSE Stable

- 2、 Set up AHB、 APB2、 APB1 The prescaler factor of

- 3、 Set up PLL The source of the clock

- Set up VCO Input clock Division factor m

- Set up VCO Output clock Octave factor n

- Set up PLLCLK Clock division factor p

- Set up OTG FS,SDIO,RNG Clock division factor q

- 4、 Turn on PLL, And wait for PLL Stable

- 5、 hold PLLCK Switch to system clock SYSCLK

- 6、 Read clock switch status bit , Make sure PLLCLK Selected as the system clock

- m: VCO Input clock Division factor , Value 2~63

- n: VCO Output clock Octave factor , Value 192~432

- p: PLLCLK Clock division factor , Value 2, 4, 6, 8

- q: OTG FS,SDIO,RNG Clock division factor , Value 4~15

- Function call examples , Use HSE Set the clock

- SYSCLK=HCLK=168M,PCLK2=HCLK/2=84M,PCLK1=HCLK/4=42M

*/

3、 Program with register

void hseCfg(void)

{

/*****************************************************************************/

/ PLL (clocked by HSE) used as System clock source /

/****************************************************************************/

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/ Reset RCC All the registers of */

RCC_DeInit();

RCC->CR |=(uint32_t)RCC_CR_HSEON;// Can make HSE The clock

// The following is waiting for the hardware to automatically set CR The register is HSERDY by 1 Express HSE The clock is ready

do

{

HSEStatus=RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

}while((HSEStatus==0)&&(StartUpCounter!=HSE_STARTUP_TIMEOUT));

if((RCC->CR & RCC_CR_HSERDY)!=RESET)

{

HSEStatus=0x1;

}

else

{

HSEStatus=0x0;

}

if(HSEStatus==0x1)

{

/* Select regulator voltage output Scale 1 mode */

/* The mode of selecting the voltage regulator is 1, Used to balance the voltage , Reduce power consumption */

RCC->APB1ENR |= RCC_APB1ENR_PWREN;

PWR->CR |= PWR_CR_VOS;

/* Divide the frequency of each bus of the system

AHB It's divided into 1

APB1 It's divided into 4

APB1 It's divided into 2

*/

RCC->CFGR |=RCC_CFGR_HPRE_DIV1;

RCC->CFGR |=RCC_CFGR_PPRE1_DIV4;

RCC->CFGR |=RCC_CFGR_PPRE2_DIV2;

/* PLL frequency doubling * RCC_PLLCFGR_PLLSRC_HSE As a system clock /

RCC->PLLCFGR = 25 | (336 << 6) | (((2 >> 1) -1) << 16) |

(RCC_PLLCFGR_PLLSRC_HSE) | (7 << 24);

/* Enable the main PLL /

/ Enable the Lord PLL /

RCC->CR |= RCC_CR_PLLON;

/ Wait till the main PLL is ready /

/ Wait for the Lord PLL Stable */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Configure Flash prefetch, Instruction cache, Data cache and wait state */

/* To configure FLASH Prefetch finger , Instruction cache , Data caching , Waiting period */

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS;

RCC->CFGR &=~(RCC_CFGR_SW);

RCC->CFGR |=RCC_CFGR_SW_PLL;// choice PLL As a system clock

while((RCC->CFGR &(uint32_t)RCC_CFGR_SWS_PLL) !=RCC_CFGR_SWS_PLL)

{

}// wait for PLL be ready , There are hardware settings

}

else

{

Do other processing for exceptions

}

}

4、 Program with firmware library

void HseCFg(uint32_t PLLM, uint32_t PLLN, uint32_t PLLP, uint32_t PLLQ)

{

ErrorStatus errorStatus=ERROR;

RCC_DeInit(); /* Reset RCC All the registers of */

RCC_HSEConfig(RCC_HSE_ON);// Can make HSE The clock

// The following is waiting for the hardware to automatically set CR The register is HSERDY by 1 Express HSE The clock is ready

errorStatus=RCC_WaitForHSEStartUp();

if(errorStatus==SUCCESS)

{

/* Divide the frequency of each bus of the system

AHB It's divided into 1

APB1 It's divided into 4

APB1 It's divided into 2

*/

RCC_HCLKConfig(RCC_SYSCLK_Div1);

RCC_PCLK1Config(RCC_HCLK_Div4);

RCC_PCLK2Config(RCC_HCLK_Div2);

/* PLL frequency doubling * RCC_PLLCFGR_PLLSRC_HSE As a system clock /

RCC_PLLConfig(RCC_PLLSource_HSE, PLLM, PLLN, PLLP, PLLQ);

RCC_PLLCmd(ENABLE);// Bit band operation used , Give the register X Location 1

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Configure Flash prefetch, Instruction cache, Data cache and wait state */

/* To configure FLASH Prefetch finger , Instruction cache , Data caching , Waiting period */

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS;

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

while((RCC->CFGR &(uint32_t)RCC_CFGR_SWS_PLL) !=RCC_CFGR_SWS_PLL)

{

}

}

else

{

}

}

5、HSI Configured as system clock

void HSIFun(uint32_t PLLM, uint32_t PLLN, uint32_t PLLP, uint32_t PLLQ)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

// ErrorStatus errorStatus=ERROR;

/* Reset RCC All the registers of */

RCC_DeInit();

RCC->CR |=(uint32_t)RCC_CR_HSION;

do

{

HSEStatus=RCC->CR & RCC_CR_HSIRDY;

StartUpCounter++;

}while((HSEStatus==0)&&(StartUpCounter!=HSE_STARTUP_TIMEOUT));

if((RCC->CR & RCC_CR_HSIRDY)==RCC_CR_HSIRDY)

{

RCC_HCLKConfig(RCC_SYSCLK_Div1);

RCC_PCLK1Config(RCC_HCLK_Div4);

RCC_PCLK2Config(RCC_HCLK_Div2);

RCC_PLLConfig(RCC_PLLSource_HSI, PLLM, PLLN, PLLP, PLLQ);

RCC_PLLCmd(ENABLE);

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Configure Flash prefetch, Instruction cache, Data cache and wait state */

/* To configure FLASH Prefetch finger , Instruction cache , Data caching , Waiting period */

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS;

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

while((RCC->CFGR &(uint32_t)RCC_CFGR_SWS_PLL) !=RCC_CFGR_SWS_PLL)

{

}

}

else

{

}

}

边栏推荐

- Fundamentals of Electronic Technology (III)_ Chapter 2 principle of amplification circuit__ Crystal triode and field effect triode

- Install local sources using yum

- Definition and use of enum in C language

- Comment la base de données mémoire joue - t - elle l'avantage de la mémoire?

- Leetcode daily question (985. sum of even numbers after queries)

- [CSDN] C1 training problem analysis_ Part II_ Web Foundation

- Assignment to '*' form incompatible pointer type 'linkstack' {aka '*'} problem solving

- Oracle数据库 SQL语句执行计划、语句跟踪与优化实例

- Project cost management__ Plan value_ Earned value_ Relationship among actual cost and Countermeasures

- I didn't think so much when I was in the field of single chip microcomputer. I just wanted to earn money to support myself first

猜你喜欢

MySQL environment variable configuration

CEF download, compile project

我想各位朋友都应该知道学习的基本规律就是:从易到难

You need to use MySQL in the opening experiment. How can you forget the basic select statement? Remedy is coming~

Flink CDC practice (including practical steps and screenshots)

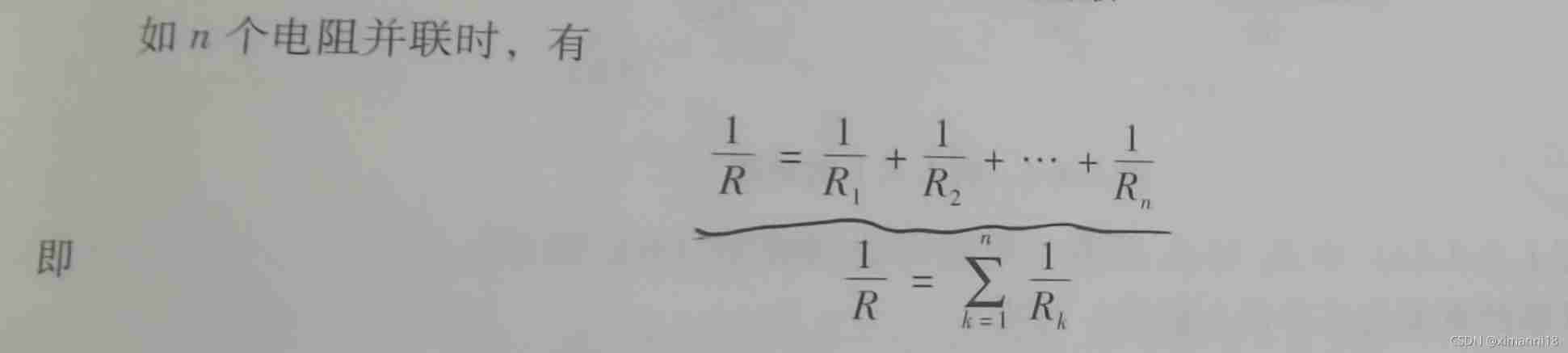

Fundamentals of Electronic Technology (III)__ Chapter 1 resistance of parallel circuit

Programming ideas are more important than anything, not more than who can use several functions, but more than the understanding of the program

![[male nanny style] teach you to open the first wechat applet](/img/a1/a571609ee846adf75506a88a629906.png)

[male nanny style] teach you to open the first wechat applet

When you need to use some functions of STM32, but 51 can't realize them, 32 naturally doesn't need to learn

![Successful graduation [2] - student health management system function development...](/img/91/72cdea3eb3f61315595330d2c9016d.png)

Successful graduation [2] - student health management system function development...

随机推荐

When you need to use some functions of STM32, but 51 can't realize them, 32 naturally doesn't need to learn

Development of fire evacuation system

Nodemcu-esp8266 development (vscode+platformio+arduino framework): Part 4 --blinker_ DHT_ WiFi (lighting technology app control + temperature and humidity data app display)

MySQL Data Definition Language DDL common commands

Successful graduation [2] - student health management system function development...

Raspberry pie installation SciPy

没有多少人能够最终把自己的兴趣带到大学毕业上

Fundamentals of Electronic Technology (III)__ Logic gate symbols in Chapter 5

Nr-prach:prach format and time-frequency domain

Project cost management__ Cost management technology__ Article 6 prediction

IDEA远程断点调试jar包项目

JMX、MBean、MXBean、MBeanServer 入门

I didn't think so much when I was in the field of single chip microcomputer. I just wanted to earn money to support myself first

Flink learning notes (XI) table API and SQL

QT qcombobox QSS style settings

Project cost management__ Cost management technology__ Article 8 performance review

应用最广泛的8位单片机当然也是初学者们最容易上手学习的单片机

对于新入行的同学,如果你完全没有接触单片机,建议51单片机入门

Stm32-hal library learning, using cubemx to generate program framework

Leetcode daily question (2212. maximum points in an archery competition)