当前位置:网站首页>Design of CAN bus controller based on FPGA (Part 2)

Design of CAN bus controller based on FPGA (Part 2)

2022-06-24 15:33:00 【FPGA technology Jianghu】

be based on FPGA Of CAN Design of bus controller ( Next )

Today, I bring you FPGA Of CAN Design of bus controller , Because of the long space , It is divided into three parts . Today brings the third , The next part , Program simulation and testing and summary . Don't talk much , Loading .

Reading guide

CAN Bus (Controller Area Network) Is the abbreviation of controller area network , yes 20 century 80 Germany in the early S BOSCH The company has developed a serial data communication protocol to solve the data exchange between many control and test instruments in modern automobiles . at present ,CAN Bus has been listed ISO international standard , be called ISO11898.CAN Bus has become one of the mainstream technologies of industrial data communication .

CAN Bus as a digital serial communication technology , Compared with other similar technologies , In reliability 、 It has unique technical advantages in real-time and flexibility , The main features are as follows :

- CAN A bus is a multi master bus , Any node on the bus can actively send information to other nodes on the network at any time, regardless of primary and secondary , Therefore, free communication between nodes can be realized .

- CAN Bus adopts non-destructive bus arbitration technology . But when multiple nodes send information to the bus at the same time , Nodes with low priority will actively quit sending , The node with the highest priority can continue to transmit data unaffected , Thus, the arbitration time of bus conflicts can be greatly saved . Even when the network load is very heavy, the network will not be paralyzed .

- CAN The communication medium of the bus can be twisted pair 、 Coaxial cable or optical fiber , Choose flexible .

- CAN The communication rate of the bus can reach 1Mbit/s( At this time, the longest communication distance is 40 rice ), The communication distance can be up to 10km( The rate is at 5kbit/s following ).

- CAN The node information on the bus is divided into different priorities , It can meet different levels of real-time requirements , High priority data can be found in 134μs Get transmitted within .

- CAN The bus can realize point-to-point through message filtering 、 Point to multipoint and global broadcasting are used to transmit data , No special scheduling is required .

- CAN The bus data adopts short frame structure , Short transmission time , Low probability of interference , It has excellent error detection effect .

- CAN The bus adopts CRC Check and provide corresponding error handling function , Ensure the reliability of data communication .

- CAN Devices on the bus can be placed in a sleep mode without any internal activity , Equivalent to not connected to the bus , Can effectively reduce system power consumption .

CAN The node on the bus has the function of automatically turning off the output in case of serious error , So that the operation of other nodes on the bus is not affected .CAN Outstanding features of the bus 、 High reliability and unique design , It is especially suitable for the interconnection of monitoring equipment in industrial process , therefore , More and more attention has been paid by the industry , And is recognized as one of the most promising fieldbus . in addition ,CAN The bus protocol has been recognized by the international organization for Standardization , Mature technology , Control chips have been commercialized , High cost performance , It is especially suitable for data communication between distributed measurement and control systems .

CAN The bus plug-in card can be inserted at any time PC AT XT Compatible with on-board , It is convenient to form a distributed monitoring system . therefore , use FPGA Realization CAN Bus communication controller has very important application value . This article will explain the use of... Through an example FPGA Realization CAN Implementation method of bus communication controller .

Part three content summary : This chapter will introduce the simulation, testing and summary of the program .

Four 、 Program simulation and testing

CAN Bus communication controller simulation program , It is necessary to send and receive analog data .

The following is part of the code of the test program :

// Connect can_top modular

can_top i_can_top(

.cs_can_i(cs_can),

.clk_i(clk),

.rx_i(rx_and_tx),

.tx_o(tx),

.irq_on(irq),

.clkout_o(clkout)

);

// produce 24 MHz The clock

initial

begin

clk=0;

forever #21 clk = ~clk;

end

// initialization

initial

begin

start_tb = 0;

cs_can = 0;

rx = 1;

extended_mode = 0;

tx_bypassed = 0;

rst_i = 1'b0;

ale_i = 1'b0;

rd_i = 1'b0;

wr_i = 1'b0;

port_0_o = 8'h0;

port_0_en = 0;

port_free = 1;

rst_i = 1;

#200 rst_i = 0;

#200 start_tb = 1;

end

// Causing delay tx The signal (CAN Transmitter delay )

always

begin

wait (tx);

repeat (4*BRP) @ (posedge clk); // 4 time quants delay

#1 delayed_tx = tx;

wait (~tx);

repeat (4*BRP) @ (posedge clk); // 4 time quants delay

#1 delayed_tx = tx;

end

assign rx_and_tx = rx & (delayed_tx | tx_bypassed); // When this signal is on, tx is not

looped back to the rx.

// The main program

initial

begin

wait(start_tb);

// Set bus timing register

write_register(8'd6, {`CAN_TIMING0_SJW, `CAN_TIMING0_BRP});

write_register(8'd7, {`CAN_TIMING1_SAM, `CAN_TIMING1_TSEG2, `CAN_TIMING1_TSEG1});

// Set the clock division register

extended_mode = 1'b0;

write_register(8'd31, {extended_mode, 3'h0, 1'b0, 3'h0}); // Setting the normal mode (not

extended)

// Set the receive code and receive register

write_register(8'd16, 8'ha6); // acceptance code 0

write_register(8'd17, 8'hb0); // acceptance code 1

write_register(8'd18, 8'h12); // acceptance code 2

write_register(8'd19, 8'h30); // acceptance code 3

write_register(8'd20, 8'h0); // acceptance mask 0

write_register(8'd21, 8'h0); // acceptance mask 1

write_register(8'd22, 8'h00); // acceptance mask 2

write_register(8'd23, 8'h00); // acceptance mask 3

write_register(8'd4, 8'he8); // acceptance code

write_register(8'd5, 8'h0f); // acceptance mask

#10;

repeat (1000) @ (posedge clk);

// Switch reset mode

write_register(8'd0, {7'h0, ~(`CAN_MODE_RESET)});

repeat (BRP) @ (posedge clk);

// Set bus idle after reset

repeat (11) send_bit(1);

test_full_fifo; // test currently switched on

send_frame; // test currently switched off

bus_off_test; // test currently switched off

forced_bus_off; // test currently switched off

send_frame_basic; // test currently switched off

send_frame_extended; // test currently switched off

self_reception_request; // test currently switched off

manual_frame_basic; // test currently switched off

manual_frame_ext; // test currently switched off

$display("CAN Testbench finished !");

$stop;

endIn the test process, each functional module of the program is verified through multiple tasks . The following procedure is used to verify the forced shutdown bus task :

// Force off bus task

task forced_bus_off; // Forcing bus-off by writinf to tx_err_cnt register

begin

// Switch to reset mode

write_register(8'd0, {7'h0, `CAN_MODE_RESET});

// Set the clock division register

write_register(8'd31, {1'b1, 7'h0}); // Setting the extended mode (not normal)

// Write data to register

write_register(8'd15, 255);

// Switch the reset mode

write_register(8'd0, {7'h0, ~(`CAN_MODE_RESET)});

#2500000;

// Switch the reset mode

write_register(8'd0, {7'h0, `CAN_MODE_RESET});

// Write data to register

write_register(8'd15, 245);

// Turn off reset mode

write_register(8'd0, {7'h0, ~(`CAN_MODE_RESET)});

#1000000;

end

endtask // forced_bus_offThe following program verifies how to send frame data in a basic format :

// Send a basic format frame

task manual_frame_basic;

begin

// Switch to reset mode

write_register(8'd0, {7'h0, (`CAN_MODE_RESET)});

// Set register

write_register(8'd4, 8'h28); // acceptance code

write_register(8'd5, 8'hff); // acceptance mask

repeat (100) @ (posedge clk);

// Switch the reset mode

write_register(8'd0, {7'h0, ~(`CAN_MODE_RESET)});

// Set bus idle after module reset

repeat (11) send_bit(1);

write_register(8'd10, 8'h55); // Writing ID[10:3] = 0x55

write_register(8'd11, 8'h57); // Writing ID[2:0] = 0x2, rtr = 1, length = 7

write_register(8'd12, 8'h00); // data byte 1

write_register(8'd13, 8'h00); // data byte 2

write_register(8'd14, 8'h00); // data byte 3

write_register(8'd15, 8'h00); // data byte 4

write_register(8'd16, 8'h00); // data byte 5

write_register(8'd17, 8'h00); // data byte 6

write_register(8'd18, 8'h00); // data byte 7

write_register(8'd19, 8'h00); // data byte 8

tx_bypassed = 1; // When this signal is on, tx is not looped back to the rx.

fork

begin

self_reception_request_command;

end

begin

#2200;

repeat (1)

// Start sending data

begin

send_bit(0); // Frame start

send_bit(0); // ID

send_bit(1); // ID

send_bit(0); // ID

send_bit(1); // ID

send_bit(0); // ID

send_bit(1); // ID

send_bit(0); // ID

send_bit(1); // ID

send_bit(0); // ID

send_bit(1); // ID

send_bit(0); // ID

send_bit(1); // RTR

send_bit(0); // IDE

send_bit(0); // r0

send_bit(0); // DLC

send_bit(1); // DLC

send_bit(1); // DLC

send_bit(1); // DLC

send_bit(1); // CRC

send_bit(1); // CRC

send_bit(0); // CRC stuff

send_bit(0); // CRC 6

send_bit(0); // CRC

send_bit(0); // CRC

send_bit(0); // CRC

send_bit(1); // CRC stuff

send_bit(0); // CRC 0

send_bit(0); // CRC

send_bit(1); // CRC

send_bit(0); // CRC

send_bit(1); // CRC 5

send_bit(1); // CRC

send_bit(0); // CRC

send_bit(1); // CRC

send_bit(1); // CRC b

send_bit(1); // CRC DELIM

send_bit(0); // ACK

send_bit(1); // ACK DELIM

send_bit(1); // EOF

send_bit(1); // EOF

send_bit(1); // EOF

send_bit(1); // EOF

send_bit(1); // EOF

send_bit(1); // EOF

send_bit(1); // EOF

send_bit(1); // INTER

send_bit(1); // INTER

send_bit(1); // INTER

end // repeat

end

join

// Read data from receive buffer

read_receive_buffer;

release_rx_buffer_command;

read_receive_buffer;

release_rx_buffer_command;

read_receive_buffer;

#4000000;

end

endtask // manual_frame_basic5、 ... and 、 summary

This article explains how to use... Through an example FPGA Realization CAN Bus communication controller . First of all, I explained CAN Bus protocol , Then it introduces a common CAN Communication controller SJA1000 The main characteristics of . Next, I will explain the main framework and specific code of the program . Finally, the program is verified by a test program . This example implements your own CAN The bus communication controller provides an applicable case .

This is the end of this article , Good bye, great Xia !

边栏推荐

- Chaos mesh in Tencent -- Tencent mutual entertainment chaotic engineering practice

- 09_ An efficient memory method

- 熬夜整理出的软件测试【高频】面试题大全(2022最新)

- MySQL toolset: the official export tool mysqlpump

- 50 practical applications of R language (23) - important concepts of Bayesian Theory: credibility, model models, and parameters

- Istio Troubleshooting: using istio to reserve ports causes pod startup failure

- Left hand code, right hand open source, part of the open source road

- ES mapping之keyword;term查询添加keyword查询;更改mapping keyword类型

- Working with collections

- A series of problems caused by IPVS connection reuse in kubernetes

猜你喜欢

IDEA 插件 Material Theme UI收费后的办法

Redis consistency hash and hash slot

Linux Installation cenos7 MySQL - 8.0.26

测试 H5 和小程序的区别,你真的知道吗?

从pair到unordered_map,理论+leetcode题目实战

As a developer, what is the most influential book for you?

刚刚阿里面软件测试回来,3+1面任职阿里P7,年薪28*15薪

API data interface for announcement of Hong Kong listed companies

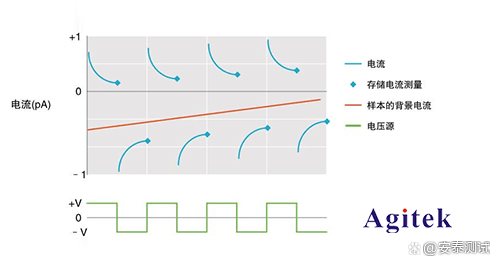

Wide measuring range of jishili electrometer

![[bitbear story collection] June MVP hero story | technology practice collision realm thinking](/img/b7/ca2f8cfb124e7c68da0293624911d1.png)

[bitbear story collection] June MVP hero story | technology practice collision realm thinking

随机推荐

Stm32f1 and stm32cubeide programming examples -ws2812b full color LED driver (based on spi+dma)

How to build a high-performance go cache Library

In 2021, big companies often ask IOS interview questions -- runloop

An accident caused by a MySQL misoperation, and the "high availability" cannot withstand it!

Laravel8 uses faker to call factory to fill data

阿里OSS对象存储服务

Use list

A series of problems caused by IPVS connection reuse in kubernetes

MySQL replication series 6- tables related to replication information

Oracle RAC configuration multipathing

[log service CLS] initial experience of Tencent cloud CLS log service

leetcode 139. Word break word split (medium)

VIM common shortcut keys

Bosun query

Two way combination of business and technology to build a bank data security management system

CVPR2022 | 可精簡域適應

Is it safe to open a stock account by mobile phone

Since the household appliance industry has entered the era of stock competition, why does Suning win the first channel for consecutive times?

Very exciting! 12000 words summarized the theory of network technology, reviewing the old and learning the new

Restoring to an earlier version in CVS