当前位置:网站首页>Details of task switching

Details of task switching

2022-07-23 15:53:00 【raindayinrain】

In a multitasking environment , There can be multiple tasks at the same time . Each task has its own local descriptor table (LDT) And task status segments (TSS). In the local descriptor table, the descriptor of the segment that belongs to the local space of the task is stored . You can switch between multiple tasks , Make them execute in turn , When switching from one task to another , The specific switching process is carried out by the processor firmware .

So called multitasking system , Refers to a system that can perform more than two tasks at the same time . Task scheduling is mainly the responsibility of the operating system , The processor is only responsible for the specific switching process , Including protecting the site of the previous task .

There are two basic ways to switch tasks , One is collaborative , Switch from one task to another , The current task needs to actively request to temporarily give up the right to execute , Or when the operating system service is requested through the call door , By the operating system " Take the opportunity " Transfer control to another task . This way depends on the task " Self-discipline ".

The other is preemptive , In this way , A timer interrupt can be installed , And implement task switching in the interrupt service program . Hardware interrupt signals always appear regularly , No matter what the processor was doing , Interruptions will happen in time , And task switching can also be carried out smoothly . In this case , Every task can get equal opportunities to perform . And , Even if a mission is out of control , It will not lead to other tasks without the opportunity to perform .

15.1. Code list of this chapter

15.2. Settings before task switching

All tasks share a global space , This is provided by the kernel or operating system , Including system service procedures and data ; meanwhile , Each task has its own local space , Each task has different functions , therefore , Local space contains the private code and data of a task that is different from other tasks .

In one task , Global space and local space have different privilege levels . Use the door , Control can be changed from 3 The local space of privilege level is transferred to 0 Privilege level global space , To use the services provided by the kernel or operating system .

Task switching is based on tasks , It means leaving a task , Go to another task to perform . Task transfer is relatively more complex , When a task is being performed , All parts of the processor are closely related to the task : The segment register points to the memory segment used by the task ; The general-purpose register holds the intermediate result of the task , wait .

Leave the current task , Go to another task to start execution , To save various states of old tasks , And restore the running environment of the new task .

That is, to perform task switching , There must be at least two tasks in the system , And one is already being implemented . In limine , The processor executes in the global space of the task , The current privilege level is 0, then , We return through a false call gate , Return the processor to the local space of the task to execute , The current privilege level is reduced to 3.

In fact, this is unnecessary . First , When the processor first enters the protected mode , With 0 Run at privilege level , And it usually executes the operating system code , It also needs to be 0 Privilege level . secondly , The task does not have to be 3 Privilege level , But 0 Privilege level . especially , In addition to providing services for every task, the operating system , There will also be a part that exists independently as a task , And is 0 Privilege level tasks , To complete some management and control functions , For example, provide an interface to interact with users .

After the computer is powered up , Once in protected mode , Directly create and execute the operating system 0 Privileged tasks . then , You can switch from this task to another task .

In that case , This chapter , The first thing to do is to create 0 Privilege level operating system ( kernel ) Mission .

Kernel tasks , The general function is to create other tasks , Manage them , So it is called task manager , Or program manager .

Task status section (TSS) It is a sign of the existence of a task , Without it , You cannot perform task switching , Because various state data of the old task need to be saved during task switching .

The program manager task does not have its own LDT, The task can not have its own LDT, This is allowed . The program manager can install its own segment descriptor in GDT in . in addition , Program manager task is to run in 0 At the privilege level , No need to create additional stacks . Because in addition to returning from the door , You cannot transfer control from high privilege level code segments to low privilege level code segments .

stay GDT Created in TSS The descriptor of , You must create TSS The descriptor of , And can only be installed on GDT in .

To indicate that the task is currently being executed , The last thing to do is to TSS Select sub transfer to task register TR in .

15.3. Method of task switching

Support for multitasking is one of the hallmarks of modern processors . So ,Intel The processor provides a variety of methods , To flexibly switch between tasks .

The processor does not provide additional instructions for task switching . in fact , We use the old instructions and methods we are familiar with , But it expands their functions , So that it can continue to perform its original functions , It can also be used to implement task switching .

The first method of task switching is by means of interruption , This is also the basis of modern preemptive multitasking .

We know , In real mode , At the lowest address of memory 1KB It's the interrupt vector table , preserved 256 Segment address and offset address of interrupt processing process . When the interrupt occurs , The processor multiplies the interrupt number by 4, Access the interrupt vector table as an index number in the table , Take out the segment address and offset address of the interrupt processing process from the corresponding position , And move there to execute .

In protected mode , The interrupt vector table is no longer used , Replaced by , Is the interrupt descriptor table .

It is similar to GDT,LDT, Used to save descriptors . The only difference is , It stores the door descriptor , Including interrupt gate , Trap gate , Mission gate .

When the interrupt occurs , The processor multiplies the interrupt number by 8( Because each descriptor accounts for 8 byte ), Access the interrupt descriptor table as an index , Take out the door descriptor . In the gate descriptor, there are code segment selectors and intra segment offsets for interrupt processing , This is the same as calling gates . next , Move to the corresponding position to execute .

General interrupt processing can use interrupt gate and trap gate . Interrupt gates and trap gates allow interrupt handling within a task , Go to the global space to perform some system level management , Essentially , It is also the control transfer behavior within the task .

however , When the interruption occurs , If the door corresponding to the interrupt number is the task door , be , The nature is quite different , Task switching is required . namely , To interrupt the execution of the current task , Protect the site of the current task , And switch to another task to perform .

Task gate descriptor format

Don't use ( occupy 16 position ) P DPL 00101 Don't use ( occupy 8 position ) TSS Chooser ( occupy 16 position ) Don't use ( occupy 16 position )

In the task gate descriptor P Bit indicates whether the door is valid , When P Position as "0" when , It is not allowed to switch tasks through this door ;DPL Is the privilege level of the task gate descriptor , But it has no effect on task switching initiated by interruption , The processor does not apply any protection at the privilege level . But that doesn't mean DPL Fields are useless , When task switching is implemented through the task gate in a non disruptive manner , It works .

When the interrupt occurs , The processor multiplies the interrupt number by 8 Access the interrupt descriptor table as an index . When it finds that this is a task gate ( The descriptor ) when , We know that task switching should be initiated . therefore , It takes out the task gate descriptor ; Then take out the new task from the task gate descriptor TSS Chooser ; next , Reuse TSS Select sub access GDT, Take out the new task TSS The descriptor .

Before moving to a new task , The processor should first save the state of the current task . The current task is TSS By the task register TR The current content of points to , therefore , The processor should put the " snapshot " Save to by TR Point to the TSS in . then , The processor accesses the new task TSS, Recover the contents of each register , Including general registers , Flag register EFLAGS, Segment register , Instruction pointer register EIP, Stack pointer register ESP, And local descriptor table register (LDTR) etc. .

Final , Task register TR Point to the new task TSS, And the processor immediately starts to perform new tasks . Once the new task starts , The processor firmware will automatically TSS Descriptors B Location "1", Indicates that the status of the task is busy .

When the interrupt occurs , Routine interrupt processing can be executed , You can also switch tasks . Although different in nature , But they all use iret Command return . The former is to return to different code segments within the same task ; The latter is to return to the interrupted task .

32 Bit processor EFLAGS Yes NT position ( position 14), It means nested task flags . For each task TSS There is a task link field in ( Pointer to the previous task ), It can be filled in as... Of the previous task TSS Descriptor selector . Such as the current task EFLAGS The register of NT Is it "1", It means that the currently executing task is nested in other tasks , And can pass TSS The pointer of the task link field returns to the previous task .

Keep set to 0( occupy 10 position ) ID empty empty empty empty empty 0 NT IOPL OF DF IF TF SF ZF 0 AF 0 PF 1 CF

When task switching is caused by interruption , Depends on the current task ( Old mission ) Whether it is nested in other tasks , Its EFLAGS The register of NT It may be "0", It could be "1". The processor will not change it , But with other registers , write in TSS Protected in . in addition , Current task ( Old mission ) Must be in " busy " state , Its TSS Descriptors B It must be "1", It remains the same after task switching .

The handling of new tasks is , We should take the old task TSS Select sub fill in the new task TSS Task link field in , meanwhile , Put the new task EFLAGS The register of NT Location "1", To allow you to return to the previous task to continue . meanwhile , We should also carry out new tasks TSS Descriptors B Location "1".

You can use iret The instruction returns from the current task to the previous task , The premise is that the current task EFLAGS The register of NT The bit must be "1". Whenever the processor encounters iret Instructions , All need to be checked NT position , Such a bit is 0, Indicates that it is a general interrupt process , Return processing according to the general interrupt , namely , Interrupt returns are within the task ( Although the interrupt processing process belongs to the operating system , But it belongs to the global space of the task ); Such a bit is 1, It indicates that the current task can be executed , Because of interrupting other tasks . therefore , You should return to the original interrupted task to continue . here , The processor firmware sends the current task EFLAGS The register of NT Bit changed to "0", And put TSS Descriptors B Bit changed to "0". After saving the status of the current task , next , Use new tasks ( Interrupted tasks ) Of TSS Restore the scene .

Except for task switching caused by interruption , You can also use far procedure calls CALL, Or far jump command JMP Directly initiate task switching . here ,CALL and JMP The operand of the instruction is task TSS Descriptor selection sub or task gate .

call 0x0010:0x00000000

jmp 0x0010:0x00000000

When the processor executes these two instructions , First, use the descriptor given in the instruction to select the sub access GDT, Analyze its descriptor type . Such is the general code segment descriptor , Just follow the ordinary inter segment transfer rules ; If it is a call gate , Execute according to the rules of the call gate ; " TSS The descriptor , Or task gate , Then perform task switching .

here , In the instruction 32 Bit offset ignored , Because when performing task switching , The status of all processors can be changed from TSS gain . Be careful , The task gate descriptor can be installed in the interrupt descriptor table , It can also be installed in the global descriptor table or local descriptor table .

If it is used to initiate task switching ,call and jmp There are also differences . Use call Task switching initiated by instruction is similar to task switching initiated by interruption . namely , from call Task switching initiated by instructions is nested , Current task ( Old mission )TSS Descriptors B Bits remain the same "1" unchanged ,EFLAGS The register of NT The bit does not change ; new task TSS Descriptors B Location "1",EFLAGS The register of NT The position is also set "1", Indicates that this task is nested in other tasks . meanwhile ,TSS The content of the task link field is changed to that of the old task TSS Descriptor selector .

Suppose the task 1 Is the first task in the whole system . When tasks 1 At the beginning of execution , Its TSS Descriptors B Is it "1",EFLAGS The register of NT Is it "0", Not nested in other tasks .

When from task 1 Switch to task 2 after , Mission 1 Still for " busy ",EFLAGS The register of NT A constant ( In its TSS in ); Mission 2 Also become a " busy ",EFLAGS The register of NT A into "1", Indicates nested in task 1 in . meanwhile , Mission 1 Of TSS Descriptor selectors are also copied to the task 2 Of TSS in ( Task link field ).

Finally, from the task 2 Go to task 3 perform . Mission 2 keep " busy ", EFLAGS The register of NT unchanged ( In its TSS in ); Mission 3 Become the current task , Its TSS Descriptors B A into "1",EFLAGS The register of NT Bit also becomes "1", meanwhile , Its TSS The task link field points to the task 2.

use CALL Command initiated task switching , It can be done by iret The instruction returns to the previous task . here , Old mission TSS Descriptors B position , And EFLAGS The register of NT Bits are restored to "0".

and call Different , Use jmp Command initiated task switching , It will not form a nested relationship between tasks . When performing task switching , Current task ( Old mission )TSS Descriptors B A reset , Become non busy ,EFLAGS The register of NT A constant ; new task TSS Descriptors B Location "1", Enter a busy state ,EFLAGS The register of NT Bit hold from TSS The state when loading in does not change .

Tasks are not reentrant .

The non reentrant nature of tasks is , When performing task switching , The status of the new task cannot be busy .

First case , When performing task switching , The new task cannot be the current task itself . Because if allowed , The processor is not good at performing on-site protection and recovery .

The second situation , Not allowed CALL Command from task 3 Switch to task 2 And tasks 1 On . If this is not prohibited , The nested relationship between tasks will be due to TSS The task link field is damaged and disordered .

The processor is through TSS Descriptors B Bit to detect reentrant . Due to interruption ,iret,call and jmp When the command initiates task switching , The processor firmware will detect new tasks TSS Descriptors B position , If "1", Such switching is not allowed .

---next

边栏推荐

- Time series data in industrial Internet of things

- Redis的过期策略以及内存淘汰机制,Key过期了为什么没释放内存

- 基于Matlab的SSB信号调制和解调(内附源码)

- [7.16] code source - [array division] [disassembly] [select 2] [maximum common divisor]

- C语言经典例题-贷款余额

- 冒泡排序-看着一篇就够啦

- C语言经典例题-逆序打印输入的两位数

- [try to hack] SQL injection less7 (into outfile and Boolean blind annotation)

- MD5 strong collision, secondary decoding,

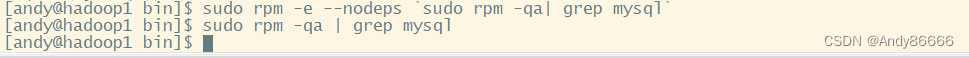

- centos7 中彻底卸载mysql

猜你喜欢

随机推荐

备份内容哈哈哈

MySQL execution order

【2023提前批 之 面经】~ 京东方

[attack and defense world web] difficulty Samsung 9 points introductory question (Part 2): shrink, lottery

The landing process of 800V high-voltage fast charging was accelerated, and Junsheng Electronics was designated for the 500million euro project

php:filter伪协议之[BSidesCF 2020]Had a bad day

C # calculate the number of times a character appears in the string

Camera flashlight modification

aws篇4 一机一密

云服务器ECS远程监控

3D数学 - 矢量

冒泡排序-看着一篇就够啦

day1

Bug modification

Where can I download airserver? How to use tutorial

老照片上色——DeOldify快速上手

Idea starts multiple projects at once

用rpm -e --nodeps进行批量删除

没有了华为,高通任意涨价,缺乏核心技术的国产手机只能任由宰割

STL deque