当前位置:网站首页>PLL of IP core

PLL of IP core

2022-07-27 06:20:00 【Three assassins】

PLL IP Introduction to nuclear

PLL Schematic diagram of structural model

PLL frequency doubling

PLL frequency division

PLL Basic configuration

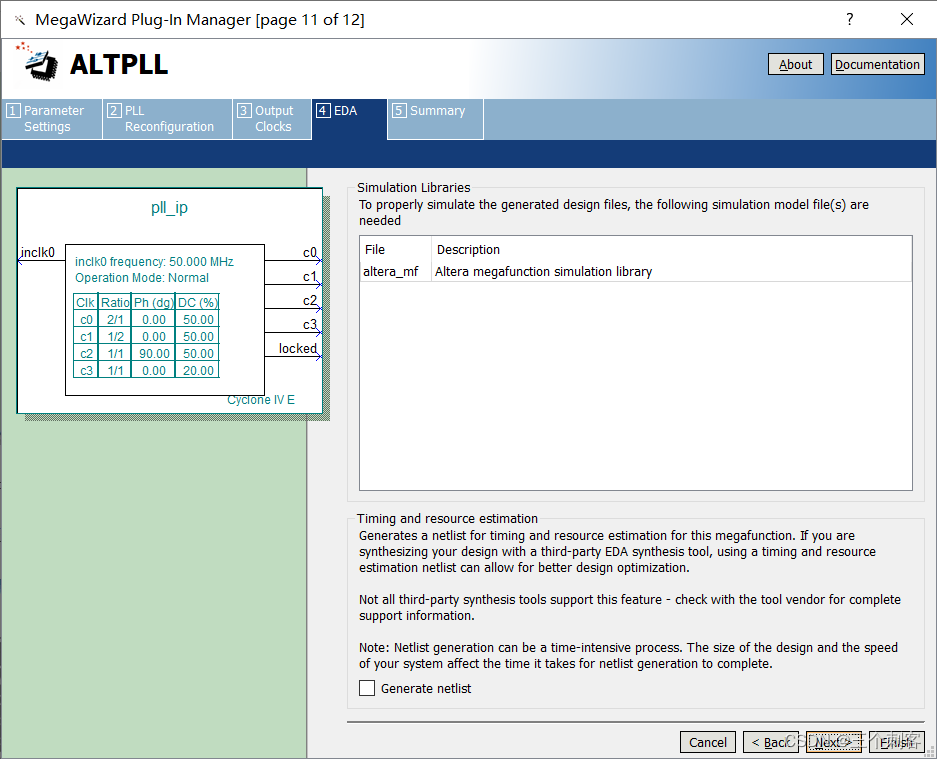

PLL IP Kernel call

pll_ip pll_ip_inst (

.inclk0 ( inclk0_sig ),

.c0 ( c0_sig ),

.c1 ( c1_sig ),

.c2 ( c2_sig ),

.c3 ( c3_sig ),

.locked ( locked_sig )

);

The following are instantiations PLL IP Core and application code writing

module pll

(

input wire sys_clk, // The system clock 50MHz

input wire sys_rst_n,

output wire clk_mul_2, // The system clock passes 2 Clock after frequency doubling

output wire clk_div, // The system clock passes 2 The clock after frequency division

output wire clk_pha_90, // The system clock is phase shifted 90° After the clock

output wire clk_duc_20, // The system clock becomes duty cycle 20% The clock of

output reg [1:0] cnt,

output wire locked // Check whether the PLL is locked , The output clock is stable only when the signal is high

);

pll_ip pll_ip_inst (

.inclk0 ( sys_clk ),

.c0 ( clk_mul_2 ),

.c1 ( clk_div ),

.c2 ( clk_pha_90 ),

.c3 ( clk_duc_20 ),

.locked ( locked )

);

[email protected](posedge clk_div or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 2'd0;

else

cnt <= cnt + 1'b1;

endmodule

PLL IP Nuclear simulation

`timescale 1ns/1ns

module tb_pll();

reg sys_clk;

wire clk_mul_2;

wire clk_div;

wire clk_pha_90;

wire clk_duc_20;

wire locked;

// Initialize the system clock

initial sys_clk = 1'b1;

//sys_clk: Analog system clock , Every time 10ns Level flip once , The period is 20ns, The frequency is 50MHz

always #10 sys_clk = ~sys_clk;

pll pll_inst

(

.sys_clk (sys_clk),

.clk_mul_2 (clk_mul_2),

.clk_div (clk_div),

.clk_pha_90(clk_pha_90),

.clk_duc_20(clk_duc_20),

.locked (locked)

);

endmodule

Then add the prepared simulation file to the project , Conduct simulation , Check the waveform .

边栏推荐

- IP核之ROM

- 多线程CAS、synchronized锁原理 、JUC以及死锁

- 论文报告-Linear Regression for face recognition

- Install Wireshark correctly

- shell script if嵌套for循环脚本

- socket 长链接

- Dynamic programming for solving problems (1)

- Unity engine starts to migrate from mono to.Net coreclr

- Li Kou 236. the nearest common ancestor of binary tree

- Wireshark graphical interface capture

猜你喜欢

Multi threaded CAS, synchronized lock principle, JUC and deadlock

ROS distributed communication

Communication mechanism cases

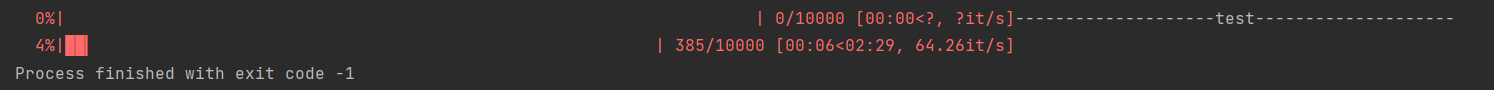

The problem that tqdm cannot display in a single line

Wireshark IP address domain name resolution

Remote sensing image recognition - making data sets

文件内容的读写——数据流

Pycharm installation and import project considerations

Acwing the number of square arrays of one question per day

UnityShader-LowPoly

随机推荐

正确安装wireshark

yum获取rpm软件包的三种方法

5G网络身份识别---详解5G-GUTI

哈夫曼树的求法,代码实现及证明,图文解释

Dynamic planning for solving problems (5)

Pzk learns string function of C language (1)

技术和理论知识学习的一点心得

tqdm无法单行显示的问题

Wireshark IP address domain name resolution

Strategies for common locks in multithreading

Dynamic planning for solving problems (4)

Li Kou 236. the nearest common ancestor of binary tree

The principle of hash table and the solution of hash conflict

多线程常见锁的策略

Linear progression for face recognition

One of the usage of operator()

ROS节点名称重名

Tangent space and TBN matrix

wireshark IP地址域名解析

Callback uses lambda