当前位置:网站首页>Batch load/store instructions of arm instruction set

Batch load/store instructions of arm instruction set

2022-06-12 11:50:00 【fanxiaoyu321】

List of articles

Batch Load-Store Instruction can realize the data exchange between a continuous memory block and a set of registers , It is usually used to save in the running environment 、 recovery , And the data copy between two memory blocks .

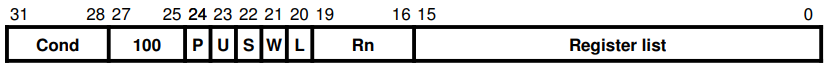

Instruction encoding format

- Register list

Every bit Represents a register , If 1 Indicates that the corresponding register participates in the transmission ,bit0 representative R0, And so on . - Rn

Specifies the base address of the memory block to be operated on . Out of commission PC Register as base register . - Load/Store Bit

0 by Store operation ,1 by Load operation . - Write-Back Bit

Specifies whether to update the base register after the instruction is executed Rn Value ,0 Not updated ,1 to update . - PSR & Force User Bit(S position )

0 It means no operation CPSR and SPSR Register or user mode ,1 Indicates that the operating program status register or is in non user mode . Because these two cases are mutually exclusive , So we can use the same bit to express . For a more detailed description, see the introduction below . - Up/Down Bit

0 Indicates that the offset is decremented from the base register ,1 Indicates incremental . - Pre/Post Indexing Bit

0 It means that after every data transfer between register and memory, it is based on U Bit updates the current offset ( After the event ),1 Indicates that the offset is updated before data transmission ( Prior operation ).

Particular attention : Do not associate pre event and post event with whether to update the base register Rn On .

About S position

First S Bits should only be used in privileged mode . Whether the command is set S Bit depends on whether there is "^" Symbol .S=1 after , According to whether there is... In the register list PC, There are several cases :

- If PC In the register list ,LDM Instructions and STM Instructions are handled differently :

- about LDM Instructions , The processor will be set up PC When the register , Synchronization will SPSR_mode Put the content of CPSR in ;

- about STM Instructions , The processor will put the user mode register into memory , Instead of registers in the current mode . This situation should not make W=1, That is, change the base register ; Be careful : At this point PC+12 Save to memory ;

- PC Not in register list ,LDM and STM Same treatment , Data is transferred between user mode register and memory . For safety reasons , belong LDM Insert a after the directive NOP Instructions , Then access the register contents ( incomprehension , It should have something to do with the assembly line );

Addressing mode

From the introduction of instruction coding format , It can be seen that , Batch Load/Store The addressing mode of the instruction should be determined by the base register Rn、U position 、 and P It's decided together .

This is a bit of a detour to understand , There are two principles to keep in mind , These principles should be followed no matter which addressing method is used .

- During data transmission , It must be according to R0~R15 In order to transmit ;

- After transmission , It must be R0 Low address in memory ,R1 High address in memory ;

The following is an example to illustrate the supported 4 Address mode . The example assumes that the base register Rn by 0x1000, The list of registers participating in batch transmission is R1、R5、R7, It is assumed that after data transmission , Will update Rn register (W=1).

In understanding the following 4 A scene , Imagine , Break down the batch operation into individual Load/Store step , This makes it easy to understand the difference .

Post incremental approach IA

Assume that the memory address of the current operation is A(A The initial value of Rn), Incrementing afterwards means that the current register and address are executed first A Data transmission of , And then it goes up A Value .

The generic pseudocode is as follows :

start_address = Rn

end_address = Rn + (Number_Of_Set_Bits_In(register_list) * 4) - 4

if CondPassed(cond) and W == 1 then

Rn = Rn + (Number_Of_Set_Bits_In(register_list) * 4)

Increment in advance IB

Assume that the memory address of the current operation is A(A The initial value of Rn), Increasing in advance means increasing in advance A Value , Then execute the current register and address A Data transmission of .

The generic pseudocode is as follows :

start_address = Rn + 4

end_address = Rn + (Number_Of_Set_Bits_In(register_list) * 4)

if CondPassed(cond) and W == 1 then

Rn = Rn + (Number_Of_Set_Bits_In(register_list) * 4)

Ex post decrement method DA

Assume that the memory address of the current operation is A(A The initial value of Rn-12+4), Decrement after the event means that the current register and address are executed first A Data transmission of , Then decrease A Value .

The generic pseudocode is as follows :

start_address = Rn - (Number_Of_Set_Bits_In(register_list) * 4) + 4

end_address = Rn

if CondPassed(cond) and W == 1 then

Rn = Rn - (Number_Of_Set_Bits_In(register_list) * 4)

Decreasing in advance DI

Assume that the memory address of the current operation is A(A The initial value of Rn-12), Decreasing in advance means decreasing first A Value , Then execute the current register and address A Data transmission of .

The generic pseudocode is as follows :

start_address = Rn - (Number_Of_Set_Bits_In(register_list) * 4)

end_address = Rn - 4

if CondPassed(cond) and W == 1 then

Rn = Rn - (Number_Of_Set_Bits_In(register_list) * 4)

Batch memory access instruction

ARM There are the following batches Load/Store Instructions .

| Mnemonic symbol | explain |

|---|---|

| LDM(1) | Bulk word data read instruction |

| LDM(2) | User mode bulk word data read instruction |

| LDM(3) | Bulk word data read instruction with status register |

| STM(1) | Batch word data write instruction |

| STM(2) | User mode bulk word data write instruction |

The general syntax of these instructions is as follows :

<LDM|STM>{

cond}<FD|ED|FA|EA|IA|IB|DA|DB> Rn{

!},<Rlist>{

^}

- !: If there is this symbol , Indicates that after the instruction is executed , Modify the base register Rn Value , namely W=1;

- ^: If there is this symbol , Presentation settings S position , At this time, the instruction will be based on whether there is... In the register list PC, And then let PSR Participate in data transmission , Or perform user mode processing , For details, see the previous section on S Bit introduction .

LDM(1)( Bulk word data read instruction )

LDM{<cond>}<address_mode> <Rn>{!}, <registers>

if CondPassed(cond) then

address = start_address

for i in [0, 14]

if register_list[i] == 1 then

Ri = Mem[address, 4]

address += 4

if register_list[15] == 1 then

value = Mem[address, 4]

if (arch version 5 or above) then

pc = value & 0xFFFF_FFFE

T Bit = value[0]

else

pc = value & 0xFFFF_FFFC

address += 4

assert end_address == address - 4

LDM(2)( User mode bulk word data read instruction )

and LDM(1) The function is similar to , The difference is that when the instruction is used in privileged mode , The memory system will access memory as a normal user mode , And finally, the data in the memory unit is stored in the user mode register .

LDM{<cond>}<address_mode> <Rn>, <registers_without_pc>^

if CondPassed(cond) then

address = start_address

for i in [0, 14]

if register_list[i] == 1 then

Ri_usr = Mem[address, 4]

address += 4

assert end_address == address - 4

LDM(3)( Bulk word data read instruction with status register )

The register list of this instruction must contain PC.

LDM{<cond>}<address_mode> <Rn>{!}, <registers_and_pc>^

if CondPassed(cond) then

address = start_address

for i in [0, 14]

if register_list[i] == 1 then

Ri = Mem[address, 4]

address += 4

CPSR = SPSR

value = Mem[address, 4]

if (arch version 4T, 5 or above) and (T Bit == 1) then

pc = value & 0xFFFF_FFFE

else

pc = value & 0xFFFF_FFFC

address += 4

assert end_address == address - 4

STM(1)( Batch word data write instruction )

STM{<cond>}<address_mode> <Rn>{!}, <registers>

if CondPassed(cond) then

address = start_address

for i in [0, 15]

if register_list[i] == 1 then

Mem[address, 4] = Ri

address += 4

assert end_address == address - 4

STM(2)( User mode bulk word data write instruction )

STM{<cond>}<address_mode> <Rn>, <registers>^

if CondPassed(cond) then

address = start_address

for i in [0, 15]

if register_list[i] == 1 then

Mem[address, 4] = Ri_usr

address += 4

assert end_address == address - 4

Stack operation

Batch Load/Store Instructions are often also used for stack operations , Due to stack FIFO Handling characteristics , First define 4 A concept :

- If the stack pointer points to the address of the last stacked element , Then call the stack Full Stack ; If you point to the next empty position of the last element , Then call the stack Empty Stack ;

- If the stack grows toward the high address , Then call the stack Ascending Stack ; contrary , If you increase to a lower address , Then call the stack Descending Stack ;

Understanding skills : When putting data on the stack , If you can put data first and then update the stack pointer , So for Empty Stack , Otherwise Full Stack , It means Full Stack corresponds to pre addressing ,Empty Corresponds to post addressing .

Sum up , share FA、FD、EA、ED Four combinations , These four combinations correspond to the previous four addressing methods one by one , They have the following corresponding relationship . And the instructions can be flexibly switched according to different contexts .

边栏推荐

- 【藍橋杯單片機 國賽 第十一届】

- ARM指令集之乘法指令

- ARM指令集之伪指令

- Windows10 install mysql-8.0.28-winx64

- Doris记录服务接口调用情况

- Why is there no traffic after the launch of new products? How should new products be released?

- Design of tablewithpage

- 6.6 分离卷积

- [QNX hypervisor 2.2 user manual] 4.1 method of building QNX hypervisor system

- TinyMCE series (IV) introduction to common built-in UI components of TinyMCE

猜你喜欢

Socket implements TCP communication flow

Design of secure chat tool based on C #

UML series articles (31) architecture modeling - deployment diagram

TinyMCE series (I) TinyMCE environment construction

转载--win10打开任务管理器就蓝屏的问题

TinyMCE realizes automatic uploading of pasted pictures

UML series articles (30) architecture modeling -- product diagram

M-arch (fanwai 10) gd32l233 evaluation -spi drive DS1302

字节序 - 如何判断大端小端

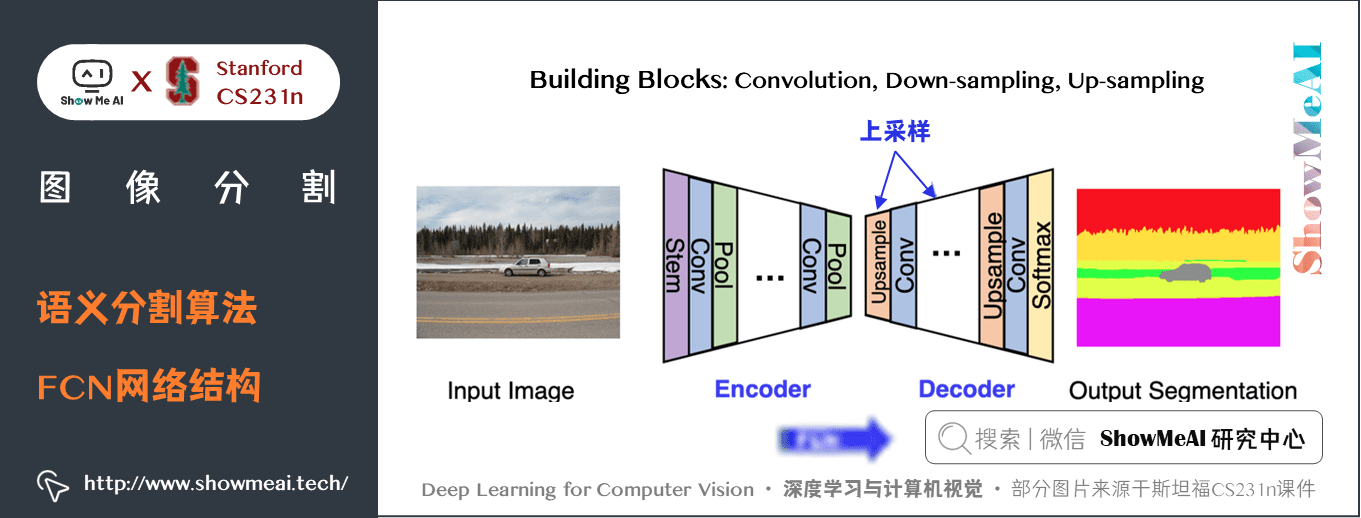

Deep learning and CV tutorial (14) | image segmentation (FCN, segnet, u-net, pspnet, deeplab, refinenet)

随机推荐

ARM指令集之数据处理指令寻址方式

Windows10 install mysql-8.0.28-winx64

Channel Shuffle类

Byte order (network / host) conversion

When you have a server

UML系列文章(30)体系结构建模---制品图

单元测试用例框架--unittest

Spark常用封装类

5g NR Protocol Learning - - ts38.211 downlink channel

【深度学习基础】神经网络的学习(4)

Promise controls the number of concurrent requests

PDSCH 相关

Golang Foundation (6)

C# 37. Textbox scroll bar and multiline

Design of virtual scrolling list

邻居子系统之邻居项状态更新

MySQL lock leak detection and defect filling

System. IO. Fileloadexception exception

How to operate the newly revised Taobao merchants and what should be paid attention to

Basic principle of Doppler effect