当前位置:网站首页>Network equipment hard core technology insider router Chapter 21 reconfigurable router

Network equipment hard core technology insider router Chapter 21 reconfigurable router

2022-07-27 15:28:00 【User 8289326】

in front 20 In this topic , We see that , Routers can be implemented through these methods :

- Home router , In general use Broadcom or MTK Of SoC Scheme realization , Such as Broadcom Of BCM7218X, One chip can realize integration Wi-Fi6 and IPTV Functional home router box .

- Enterprise level ,1Gbps-200Gbps Performance range router , have access to Marvell (Cavium),Broadcom(RMI) Of MIPS or ARM Multi core processor implementation . It can also be used in the future x86+DPDK Realization .

- Enterprise high-end and operator level ,200G-20T Performance range router , Current general use NP Realization .

We found that , The higher the performance of the router , The less flexible the forwarding chip is . With NP For example ,NP The message processing pipeline of is limited . In practice , There have been such cases :

Internet enterprises need to send the traffic separated from metro lines to the back end for analysis , Due to the limited performance of a single analyzer , By stream required ( Business flow TCP Quintuples ) Load balancing .

As shown in the figure below :

among , The number on the right refers to the offset of the beginning of each header field of the packet .

actually , What users expect is , According to the inner layer IP/TCP Shunting packets onto multiple analyzers . But because of the inner layer IP/TCP Encapsulated in 70 After many bytes , And general NP/ASIC The built-in analyzer can only extract the message header 64 Byte parsing , Therefore, it is difficult to realize such a function . For multicore processors , Although there is also a hardware parsing accelerator inside , similarly , For this deep encapsulated tunnel , It is also difficult to deal with .

Now , We need a programmable hardware acceleration unit to realize this function . Engineers have set their sights on a class of reconfigurable devices ——FPGA.

FPGA yes "Field Programmable Gate Array" ( Field programmable gate array ) Abbreviation . The Chinese name of this tongue twister can actually be disassembled into several parts :

A programmable —— Its processing logic can be modified , Unlike ASIC That is relatively solidified ;

gate array —— Its internal minimum programming allocation unit is gate circuit and trigger , Therefore, it can be programmed to a high degree , Various processing logic can be reconstructed ;

The scene ——FPGA built-in SRAM Store compiled code , It can be upgraded at runtime through software , Complete the upgrade without even restarting ;

Because of these characteristics ,FPGA It is often used to accelerate packet processing in the network , Typically, it is used for the acceleration of routers or firewalls .

For the previously mentioned scenario of metropolitan area network image traffic analysis , Namely FPGA Where it comes in handy . Engineers only need to FPGA Programming , Let it come from 78 Begin to extract the inner layer at byte IP/UDP( Real business address / port ) The quintuple of , Calculation hash after , Send to the corresponding analyzer , You can do it NP And multi-core routers have a difficult task .

because FPGA Reconfigurable features of , Its reconfigurable router is more open , More powerful , It also makes up for the weakness of the performance degradation of multi-core processors when services are superimposed .

You know the most classic reconfigurable FPGA What kind of router is it ?

When the answer is announced tomorrow , Also tell you a router story …

边栏推荐

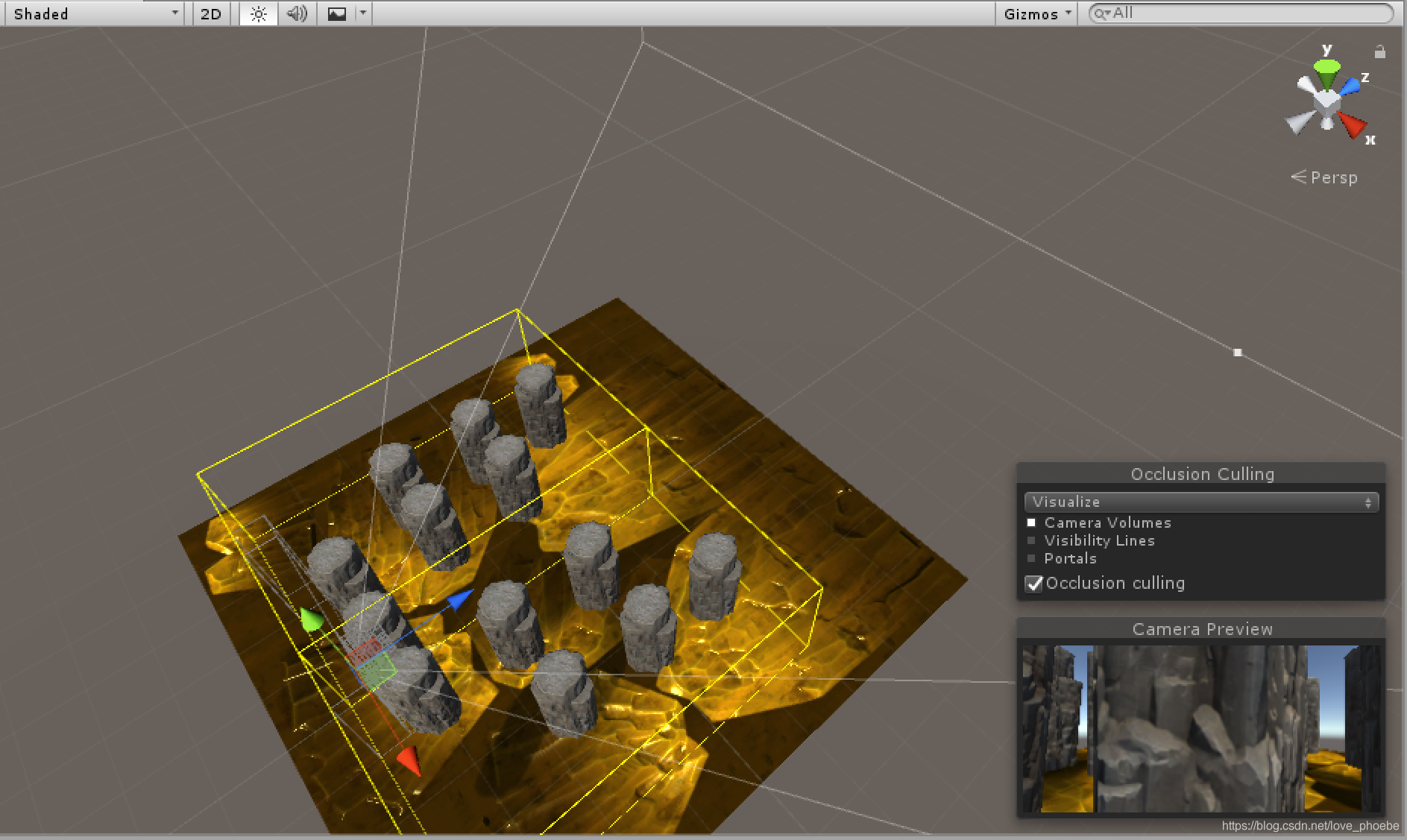

- Unity性能优化------渲染优化(GPU)之LOD(Level of detail)

- Unity performance optimization ----- occlusion culling of rendering optimization (GPU)

- How "Crazy" is Hefu Laomian, which is eager to be listed, with capital increasing frequently?

- How to package AssetBundle

- LeetCode 191. Number of 1 Bits(位1的个数) 位运算/easy

- 网络设备硬核技术内幕 路由器篇 10 CISCO ASR9900拆解 (三)

- 适配验证新职业来了!华云数据参与国家《信息系统适配验证师国家职业技能标准》编制

- LeetCode 341.扁平化嵌套列表迭代器 dfs,栈/ Medium

- 多线程环境下CountDownLatch的用法

- JUC(JMM、Volatile)

猜你喜欢

Method of removing top navigation bar in Huawei Hongmeng simulator

TL431-2.5v基准电压芯片几种基本用法

IJCAI 2022 outstanding papers were published, and 298 Chinese mainland authors won the first place in two items

Leetcode 240. search two-dimensional matrix II medium

Unity性能优化------渲染优化(GPU)之Occlusion culling(遮挡剔除)

LeetCode 190. 颠倒二进制位 位运算/easy

Several basic uses of tl431-2.5v voltage reference chip

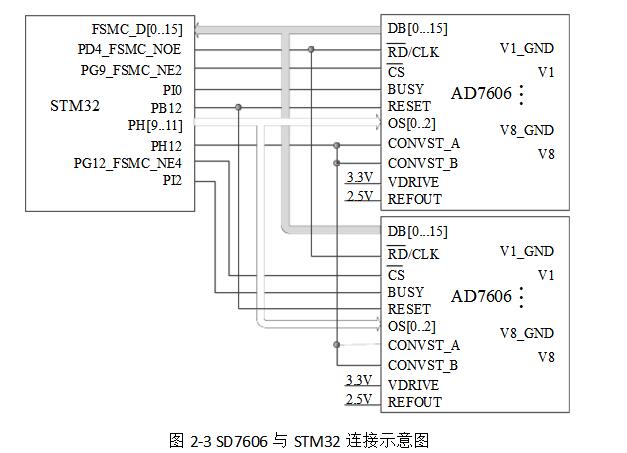

Introduction of the connecting circuit between ad7606 and stm32

Unity performance optimization ----- LOD (level of detail) of rendering optimization (GPU)

Leetcode interview question 17.21. water volume double pointer of histogram, monotonic stack /hard

随机推荐

The mobile terminal uses the list component of vantui. When multiple tab items are switched back and forth, the list is loaded many times, resulting in the failure of normal display of data

Sword finger offer merges two sorted linked lists

网络设备硬核技术内幕 路由器篇 18 DPDK及其前传(三)

华云数据打造完善的信创人才培养体系 助力信创产业高质量发展

适配验证新职业来了!华云数据参与国家《信息系统适配验证师国家职业技能标准》编制

《剑指Offer》 链表反转

MySQL 面试40连问,面试官你再问下去我可要翻脸了

Unity mouse controls the first person camera perspective

网络设备硬核技术内幕 路由器篇 6 汤普金森漫游网络世界(中)

Distributed lock

《剑指Offer》 合并两个排序的链表

Basic usage of kotlin

《终身成长》读书笔记(一)

How to edit a framework resource file separately

《剑指Offer》数组中的逆序对

Principle of MOS tube to prevent reverse connection of power supply

STM32F10x_硬件I2C读写EEPROM(标准外设库版本)

3.3-5v转换

USB2.0接口的EMC设计方案

JUC(JMM、Volatile)