当前位置:网站首页>Verilog avoid latch

Verilog avoid latch

2022-07-02 03:02:00 【Da Xi】

Verilog avoid Latch

key word : trigger , Latch

Latch The meaning of

Latch (Latch), Is a level triggered storage unit , The action of data storage depends on the input clock ( Or enable ) The level value of the signal . Only when the latch is enabled , The output will change with the data input .

When the level signal is invalid , The output signal varies with the input signal , It's like passing the buffer ; When the level is active , The output signal is latched . Any change in the excitation signal , Will directly cause the change of latch output state , It is very likely that oscillation will occur due to the instability of transient characteristics .

The schematic diagram of latch is as follows :

trigger (flip-flop), Is an edge sensitive storage unit , The act of storing data ( State transition ) Synchronized by the rising or falling edge of a signal ( Limit the storage unit state transition in a very short time ).

The schematic diagram of the trigger is as follows :

register (register), stay Verilog Variables used to temporarily store the data involved in the operation and the operation results . When a variable is declared as a register , It can be synthesized into triggers , It may also be integrated into Latch, Even wire Type variable . But in most cases we want it to be integrated into triggers , But sometimes due to code writing problems , It will be synthesized into unexpected Latch structure .

Latch The main hazards are :

- 1) The input state may change many times , It's easy to burr , The uncertainty of the next stage circuit is increased ;

- 2) In most FPGA In the resources of , It may require more resources than triggers to implement Latch structure ;

- 3) The emergence of latches makes the static timing analysis more complex .

Latch It is mostly used for gating clock (clock gating) The control of , In general design , We should avoid Latch The birth of .

if The structure is incomplete

In combinatorial logic , incomplete if - else structure , Will produce latch.

For example, the following model ,if Missing in statement else structure , System default else Branch lower register of q The value of remains unchanged , That is, it has the function of storing data , So register q Will be integrated into latch structure .

example

module module1_latch1(

input data,

input en ,

output reg q) ;

always @(*) begin

if (en) q = data ;

end

endmodule

Avoid this latch There are mainly 2 Kind of , One is to complete if-else structure , Or assign an initial value to the signal .

for example , In the model above always sentence , It can be changed into the following two forms :

example

// Complete the conditional branch structure

always @(*) begin

if (en) q = data ;

else q = 1'b0 ;

end

// Assign initial value to

always @(*) begin

q = 1'b0 ;

if (en) q = data ; // If en It works , rewrite q Value , otherwise q Will remain as 0

end

But in temporal logic , incomplete if - else structure , Will not produce latch, For example, the following model .

This is because ,q Register has storage function , And its value will change only under the edge of the clock , This is the characteristic of triggers .

example

module module1_ff(

input clk ,

input data,

input en ,

output reg q) ;

always @(posedge clk) begin

if (en) q <= data ;

end

endmodule

In combinatorial logic , When there are many assignment statements in a conditional statement , The incompleteness of the assignment statement under each branch condition will also produce latch.

In fact, for the logical split of each signal , This is also equivalent to if-else The structure is incomplete , The related register signal lacks the assignment behavior under other conditions . for example :

example

module module1_latch11(

input data1,

input data2,

input en ,

output reg q1 ,

output reg q2) ;

always @(*) begin

if (en) q1 = data1 ;

else q2 = data2 ;

end

endmodule

This situation can also be avoided by adding complete assignment statements or assigning initial values latch. for example :

example

always @(*) begin

//q1 = 0; q2 = 0 ; // Or right here q1/q2 Assign initial value to

if (en) begin

q1 = data1 ;

q2 = 1'b0 ;

end

else begin

q1 = 1'b0 ;

q2 = data2 ;

end

end

case The structure is incomplete

case Statements produce Latch The principle of is almost the same as if The sentences are consistent . In combinatorial logic , When case The list of options is incomplete and there is no addition default keyword , Or when multiple assignment statements are incomplete , There will be Latch. for example :

example

module module1_latch2(

input data1,

input data2,

input [1:0] sel ,

output reg q ) ;

always @(*) begin

case(sel)

2'b00: q = data1 ;

2'b01: q = data2 ;

endcase

end

endmodule

Of course , Eliminate such latch The way to do that is 2 Kind of , take case The list of options is complete , Or assign an initial value to the signal .

Complete case Option list , You can list all the options and results , It can also be used. default Keyword instead of other options results .

for example , Above always The statement has the following 2 Two modification methods .

example

always @(*) begin

case(sel)

2'b00: q = data1 ;

2'b01: q = data2 ;

default: q = 1'b0 ;

endcase

end

always @(*) begin

case(sel)

2'b00: q = data1 ;

2'b01: q = data2 ;

2'b10, 2'b11 :

q = 1'b0 ;

endcase

end

Assign or judge the original signal

In combinatorial logic , If the assignment source of a signal has its own signal , Or there is the logic of the signal itself in the judgment condition , Then there will be latch. Because at this time, the signal also needs to have the storage function , But there is no clock drive . Such problems are if sentence 、case sentence 、 Question mark expressions can appear , for example :

example

//signal itself as a part of condition

reg a, b ;

always @(*) begin

if (a & b) a = 1'b1 ; //a -> latch

else a = 1'b0 ;

end

//signal itself are the assigment source

reg c;

wire [1:0] sel ;

always @(*) begin

case(sel)

2'b00: c = c ; //c -> latch

2'b01: c = 1'b1 ;

default: c = 1'b0 ;

endcase

end

//signal itself as a part of condition in "? expression"

wire d, sel2;

assign d = (sel2 && d) ? 1'b0 : 1'b1 ; //d -> latch

Avoid this Latch Methods , There's only one , That is to avoid this kind of writing in combinatorial logic , Don't assign a value to the signal itself , And do not use the assignment signal itself to participate in the judgment of conditional logic .

for example , If no immediate output is required , The signal can be delayed by one clock cycle and then combined with related logic . The first one mentioned above produces Latch The code of can be described as :

example

reg a, b ;

reg a_r ;

always (@posedge clk)

a_r <= a ;

always @(*) begin

if (a_r & b) a = 1'b1 ; //there is no latch

else a = 1'b0 ;

end

The list of sensitive signals is incomplete

If in combinatorial logic [email protected]() The sensitive list in the block is not complete , There is no trigger when it should be triggered , Then the relevant register will still save the previous output , Thus a latch is generated .

This situation , Complete the sensitive signal or use it directly [email protected](*) Can eliminate latch.

Summary

All in all , To avoid latch The birth of , In combinatorial logic , The following points need to be noted :

- 1)if-else or case sentence , The structure must be complete

- 2) Do not place the assignment signal at the assignment source , Or conditional judgment

- 3) The list of sensitive signals is recommended to be multi-purpose [email protected](*)

边栏推荐

- Face++ realizes face detection in the way of flow

- Qualcomm platform wifi-- WPA_ supplicant issue

- [learn C and fly] 1day Chapter 2 (exercise 2.2 find the temperature of Fahrenheit corresponding to 100 ° f)

- How to create an instance of the control defined in SAP ui5 XML view at runtime?

- 批量检测url是否存在cdn—高准确率

- 2022 safety officer-c certificate examination questions and mock examination

- Delphi xe10.4 installing alphacontrols15.12

- C shallow copy and deep copy

- The video number will not be allowed to be put on the shelves of "0 yuan goods" in the live broadcasting room?

- SAML2.0 笔记(一)

猜你喜欢

Soul app released the annual report on generation Z behavior: nearly 20% of young people love shopping in the vegetable market

About DNS

Special symbols in SAP ui5 data binding syntax, and detailed explanation of absolute binding and relative binding concepts

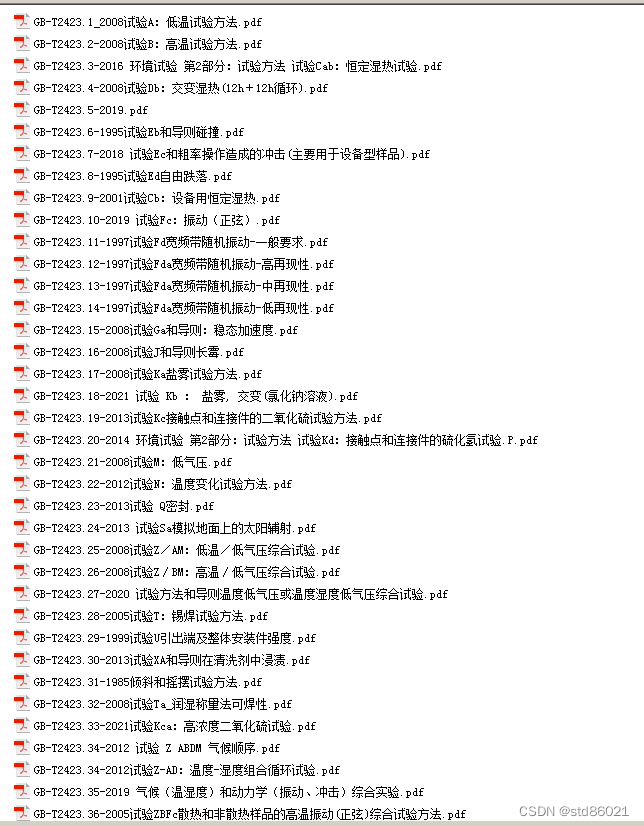

GB/T-2423.xx 环境试验文件,整理包括了最新的文件里面

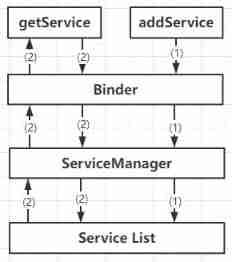

Systemserver service and servicemanager service analysis

Which kind of sports headphones is easier to use? The most recommended sports headphones

How to create an instance of the control defined in SAP ui5 XML view at runtime?

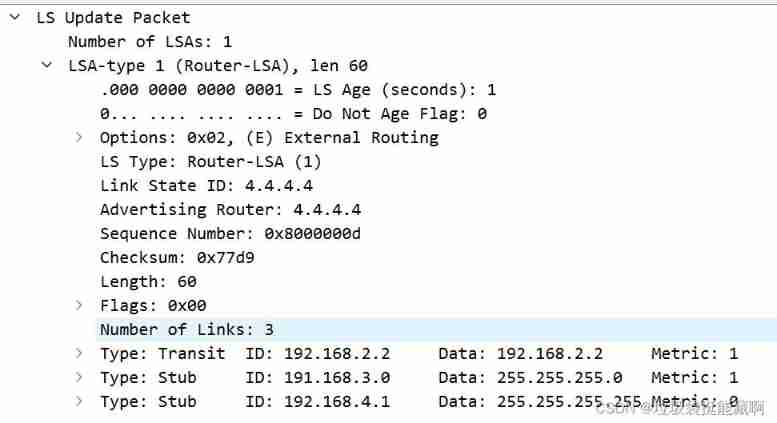

OSPF LSA message parsing (under update)

Baohong industry | four basic knowledge necessary for personal finance

Mongodb non relational database

随机推荐

After marriage

Coordinatorlayout + tablayout + viewpager2 (there is another recyclerview nested inside), and the sliding conflict of recyclerview is solved

Delphi xe10.4 installing alphacontrols15.12

New programmer magazine | Li Penghui talks about open source cloud native message flow system

Build a modern data architecture on the cloud with Amazon AppFlow, Amazon lake formation and Amazon redshift

結婚後

What are the characteristics of common web proxy IP

QT environment generates dump to solve abnormal crash

[staff] pitch representation (treble clef | C3 60 ~ B3 71 pitch representation | C4 72 pitch representation | C5 84 pitch representation)

Addition without addition, subtraction, multiplication and division (simple difficulty)

2022-2028 global deep sea generator controller industry research and trend analysis report

[JSON] gson use and step on the pit

Verilog 避免 Latch

[staff] diacritical mark (ascending sign | descending sign B | double ascending sign x | double descending sign BB)

Special symbols in SAP ui5 data binding syntax, and detailed explanation of absolute binding and relative binding concepts

Use the open source project [banner] to achieve the effect of rotating pictures (with dots)

[staff] the direction of the symbol stem and the connecting line (the symbol stem faces | the symbol stem below the third line faces upward | the symbol stem above the third line faces downward | the

Baohong industry | 6 financial management models at different stages of life

[JVM] detailed description of the process of creating objects

Start a business