当前位置:网站首页>Detailed explanation of memory addressing in 8086 real address mode

Detailed explanation of memory addressing in 8086 real address mode

2022-06-12 07:09:00 【Fat fat is the sun】

Catalog

Physical segmentation of memory and the disadvantages of physical segmentation

Register related to memory address

Logical segmentation of memory

The maximum number of logical segments ?

The distribution of logical segments in memory space

Data segment and additional segment overlap

A physical unit can have multiple logical addresses

The special place where data is stored in the stack segment

What is a program module ?

A large program is generally divided into several program modules , Each program module can implement a specific function . Compared with assembly language, a low-level language , Some high-level languages have the concept of subroutines , stay C A subroutine in a language is a function block . A large program must consist of many program modules , These program modules can be run on the same block of memory in time sharing , It can also run simultaneously in different memory locations :

Physical segmentation of memory and the disadvantages of physical segmentation

The above segmentation operation in the physical space in the memory is called the physical segmentation of the memory , Its drawback lies in the waste of resources , This waste can be reduced from “ Physical segmentation will fix the storage space of each segment, resulting in inflexible memory allocation ” It is concluded that :

Suppose our program has 2 Two program modules are running and the two program modules use a lot of code , But the stack and data take up very little memory , This makes the code segment out of memory , But if you use logical segmentation, you can solve this problem :

Register related to memory address

We also see the drawbacks of physical segmentation , Therefore, the memory is segmented in a logical way . Logical segments in memory are also called logical segments for short , We've seen before 8086CPU Inside 14 A register , Besides 4 In addition to the segment base address register, there are also related to the memory address 4 individual , Respectively :

Base pointer register BP | The offset address of the memory unit storing the data segment |

Source index register SI | The source address of the data operation |

Target index register DI | The destination address of the data operation |

Top of stack pointer register SP | Point to the top of the stack |

Logical segmentation of memory

Logical segmentation of memory is performed by the operating system , Therefore, the segment base address of a logical segment is artificially uncontrollable , The operating system uses “ to make use of every bit of time ” Memory allocation mode , Efficient use of memory space , So we don't know where the memory is free at a certain time , Where free memory can hold a logical segment of a program module .

A program module has at most 4 Logical segment ( Data segment 、 Code segment 、 Additional segment 、 stack segment ) And the maximum number of each logical segment is 1 individual , Let's recall that “16 The segment base address register of bit can generate up to 64K An address code , That means through the instruction pointer register IP The segment base address register can address up to 64K Memory units ”, This results in the following restrictions on logical segments in each program module :

1. A program module has at most 4 Logical segment ( Data segment 、 Code segment 、 Additional segment 、 stack segment );

2. The maximum number of each logic segment in a program module is 1 individual ;

3. The maximum length of each logical segment in a program module is 64K;

The registers used by the logical segment are as follows :

The code snippet only needs The base register of a code segment CS And instruction pointers IP The program can be automatically executed one by one , Instruction pointer IP Offset address stored in Point to the next code segment memory list that needs to be accessed element , Instructions until the program is accessed until ;

In the stack segment SP Store the offset address of the stack top pointer ,BP It stores the offset address of the memory unit relative to the beginning of the segment ,SP and BP Although they all store offset addresses , however SP Dedicated to the stack and BP Universal ;

Both data segment and additional segment store data , Operations involving data transfer require index registers SI and DI Sometimes you need a register to store the base address of the data segment BX( In the following, the batch transfer of data in memory cells is taken as an example ).

Address code of memory

8086CPU To manage / visit 1MB Memory must have 1MB An address is enough , This requires 20 Physical address of bit ( The physical address is independent of the physical segment , The physical address refers to the specific location of the memory unit in the memory module , It is similar to the house number of each room in the building , The house number is fixed and does not change according to external transformation ).

20 The bit address is calculated by the address adder :

Operation logic of address adder :16 Bit segment base address <<4+ offset =20 Bit physical address

A logical segment must end with a section ( The end address of each logical segment must be able to be 16 to be divisible by , That is, the end address of the logical segment must be 0000B) Can only be , This is to ensure that 16 The data stored in the bit architecture is 16 Bit length stored .

The maximum number of logical segments ?

Although a program module has at most 4 There are different kinds of logical segments , But a large project project contains many logical segments , We can imagine the maximum number of logical segments in a project , The answer is “1MB/16B=64K A logical segment ”, That is, when the total space occupied by the project is 1MB And the length of each logical segment is the minimum length 16B, At this time, the number of logical segments is the largest , achieve 64K individual .

The distribution of logical segments in memory space

The distribution of a memory unit in memory can take many forms :

1. A memory unit belongs to the same at different times / Different logical segments ( Time division multiplexing )

2. At the same time, a memory unit belongs to different logical segments ( Only data segments and additional segments can overlap )

We can see T1 The time address is 5F00H:1009H The memory unit of is not only a data segment but also an additional segment .

Data segment and additional segment overlap

To copy a set of data from a certain section of the memory to another section of the memory :

When transferring data , We are often “ Data segments and additional segments are used together ”:

use DS:[SI] Indicates the address of the data storage unit in the source data area , use ES:[DI] Indicates the address of the data storage unit in the destination data area . hypothesis DS=250AH,ES=2EF0H, Execute the following program segments , The source data area can be 100 A word (Word) Data is copied to the destination data area :

MOV CX, 100 ; In the count register CX Set the number of cycles in

MOV SI,1 ; The source address of the operation object ( Relative address )

MOV DI,1 ; Destination address of operation object ( Relative address )

LP1:

MOV DX, DS:[SI] ; Address ( Segment base address + offset ) Content stored in copy Enter into DX In the data register

MOV ES:[DI], DX ; take DX Content copy The entry address is ES+DI In the storage unit of

INC SI

INC DI

LOOP LP1 ; Cycle until CX The value in is 0 The program execution logic is as follows :

Be careful : An additional segment is an extension of a data segment , We can also call the additional paragraph “ Additional data segments ”, This shows that both the additional segment and the data segment are used to store data , Besides , such Batch data operation Also known as “ String operation ”.

As mentioned earlier, when operating data segments ,BX Base register 、SI Source index register 、DI The three target index registers are combined with the data segment base register DS After that, the data segment data transfer operation similar to the above can be realized :

hypothesis DS=250AH,BX=2EF0H, Execute the following program segments , The source data area can be 100 A word (Word) Data is copied to the destination data area :

MOV CX, 100 ; In the count register CX Set the number of cycles in

MOV SI,1 ; The source address of the operation object ( Relative address )

MOV DI,1 ; Destination address of operation object ( Relative address )

LP1:

MOV DX, DS:[SI] ; take “ Segment base address + offset ”copy Enter into DX In the data register

MOV BX:[DI], DX ; take DX Content copy The entry address is BX+DI In the storage unit of

INC SI

INC DI

LOOP LP1 ; Cycle until CX The value in is 0 In fact, here BX Acted as ES The role of ,BX The destination address where the data transfer is stored , We use a loop to keep the data copy To the destination address .

A physical unit can have multiple logical addresses

As mentioned earlier “ Data segments and additional segments can overlap ”, in other words “ A memory unit can belong to both data segment and additional segment at the same time ”:

stack segment

When the stack top pointer = Bottom of stack pointer , Empty stack ; When the stack top pointer = Stack segment base address , Full stack . Again , Stack segments belong to logical segments and have logical segments in number ( At most one in a program module ) And length (MAX=64KB) The limit on .

The special place where data is stored in the stack segment

The stack section holds some “ Very important data that needs to be saved and may not be available at present ”, For example, the return address of a function ( The execution of the function body is independent of the return address of the function body , But where the function body returns after execution is determined by the return address of the function ) etc. . The return address of a function and the storage address of a variable are common function names and variable names , These name symbols represent the relative position of data storage ( The offset address ), As mentioned earlier, the segment base address is randomly assigned by the operating system. We can't decide it manually .

边栏推荐

- 网络丢包问题排查

- Detailed explanation of convirt paper (medical pictures)

- Summary from November 29 to December 5

- 5、 El expression & JSTL tag library

- 5 statement

- 9 Sequence container

- RT thread studio learning (I) new project

- 【数据聚类】本专栏中涉及数据集、可视化及注意事项

- leetcode:剑指 Offer 67. 把字符串转换成整数【模拟 + 分割 +讨论】

- Freshmen are worried about whether to get a low salary of more than 10000 yuan from Huawei or a high salary of more than 20000 yuan from the Internet

猜你喜欢

美团获得小样本学习榜单FewCLUE第一!Prompt Learning+自训练实战

![[Li Kou] curriculum series](/img/eb/c46a6b080224a71367d61f512326fd.jpg)

[Li Kou] curriculum series

leetcode:剑指 Offer 63. 股票的最大利润【记录前缀最小和 or 无脑线段树】

libprint2

leetcode:剑指 Offer 66. 构建乘积数组【前后缀积的应用】

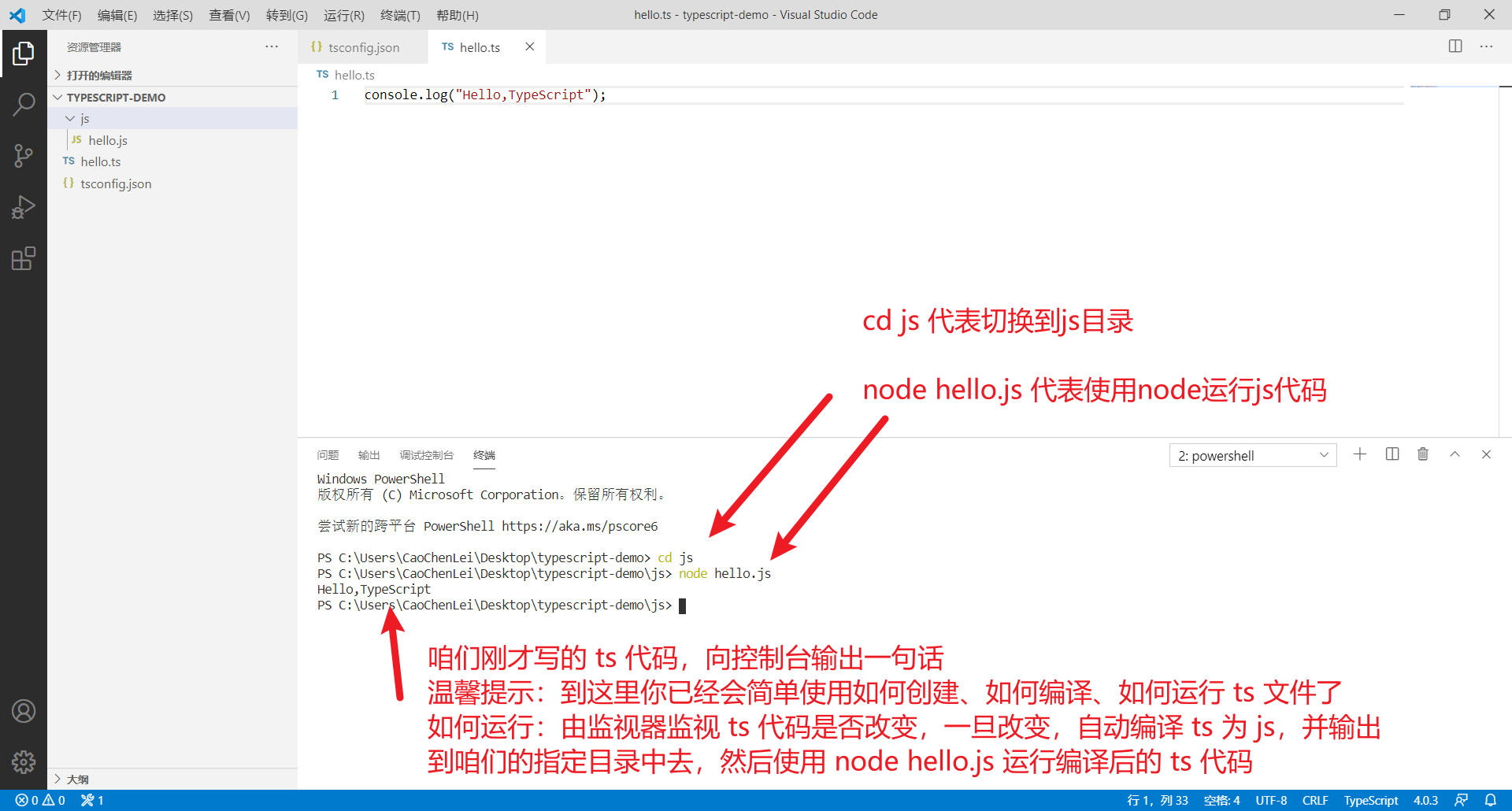

TypeScript基础知识全集

SQL Server 2019 installation error. How to solve it

【图像检测】基于深度差分和PCANet实现SAR图像变化检测附matlab代码

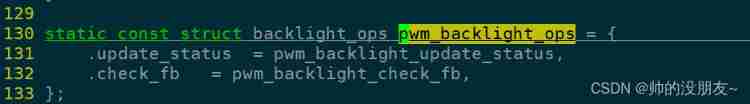

Imx6q PWM drive

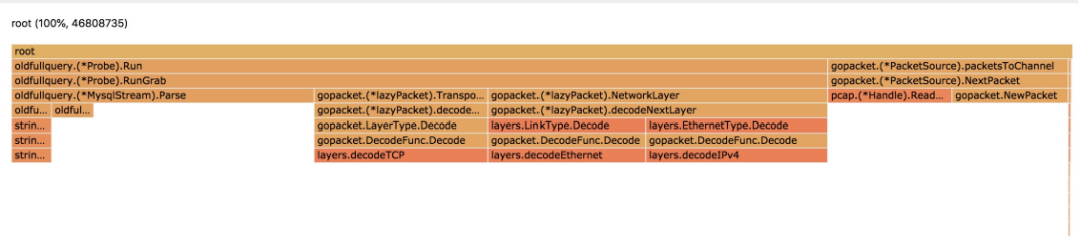

A journey of database full SQL analysis and audit system performance optimization

随机推荐

XML special character escape

Explain in detail the use of dynamic parameter adjustment and topic communication in ROS (principle + code + example)

1. Foundation of MySQL database (1- installation and basic operation)

android studio 利用数据库实现登录注册界面功能

Pyhon的第五天

8. form label

Apache POI import export excel file

Kali与编程:如何快速搭建OWASP网站安全实验靶场?

leetcode.39 --- 组合总和

Node, topic, parameter renaming and global, relative and private namespaces in ROS (example + code)

Installation and use of eigen under vs2017

【图像去噪】基于偏微分方程(PDE)实现图像去噪附matlab代码

Detailed explanation of convirt paper (medical pictures)

(14) The software version number is displayed in the flash window of blender source code analysis

Redis supports data structure types

How to update kubernetes certificates

[image denoising] image denoising based on partial differential equation (PDE) with matlab code

Kotlin插件 kotlin-android-extensions

Zhang Chi: is process a panacea?

5 statement