当前位置:网站首页>GM8775C规格书,MIPI转LVDS,MIPI转双路LVDS分享

GM8775C规格书,MIPI转LVDS,MIPI转双路LVDS分享

2022-08-02 03:29:00 【TE13530609500】

1 产品概述

2 产品特征

3 产品功能框图

4 封装及引脚功能说明

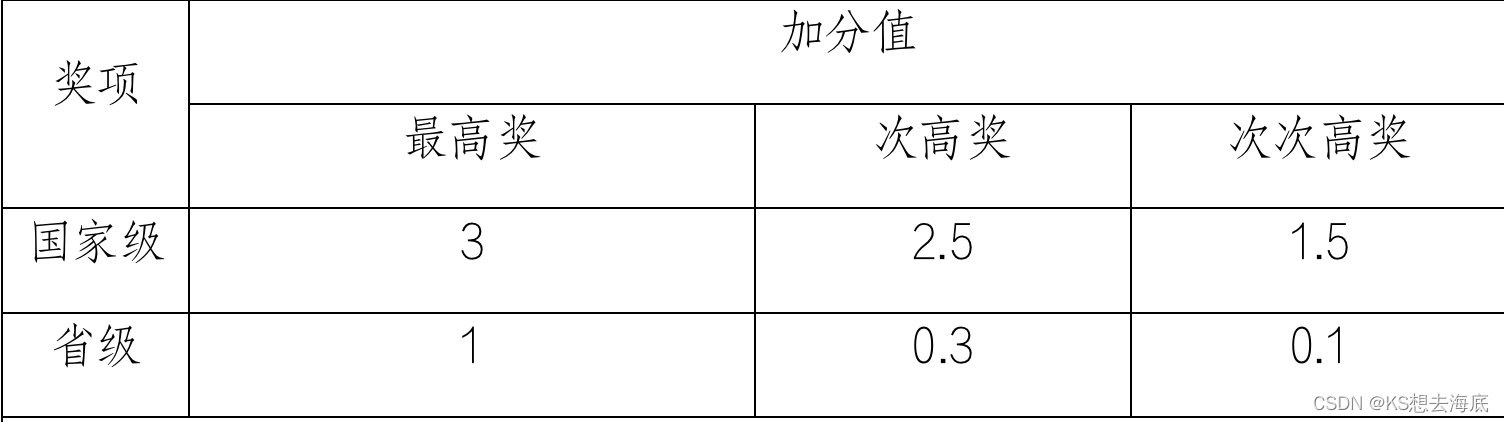

| 尺寸符号 | 数值 | ||

| 最小 | 公称 | 最大 | |

| A | 0.70 | ― | 0.80 |

A1 | 0 | ― | 0.05 |

b | 0.18 | ― | 0.30 |

c | 0.18 | ― | 0.23 |

D | ― | ― | 7.10 |

E | ― | ― | 7.10 |

e | ― | 0.50 | ― |

D2 | 5.30 | ― | 5.50 |

E2 | 5.30 | ― | 5.50 |

L | 0.35 | ― | 0.45 |

Z | ― | 0.75 | ― |

| 引脚号 | 引脚名称 | IO 方向 | 功能说明 |

| MIPI 输入端口 | |||

| 14/15 | DA0P/ DA0N | In | MIPI DSI 数据 0 通道差分输入正/负端 |

| 16/17 | DA1P/ DA1N | In | MIPI DSI 数据 1 通道差分输入正/负端 |

| 20/21 | DA2P/ DA2N | In | MIPI DSI 数据 2 通道差分输入正/负端 |

| 22/23 | DA3P/ DA3N | In | MIPI DSI 数据 3 通道差分输入正/负端 |

| 18/19 | DACP/ DACN | In | MIPI DSI 时钟差分输入正/负端 |

| LVDS 输出端口 | |||

| 34/33 | A_Y0P/A_Y0N | Out | A 通道 LVDS 数据 0 路差分输出正/负端 |

| 32/31 | A_Y1P/A_Y1N | Out | A 通道 LVDS 数据 1 路差分输出正/负端 |

| 30/29 | A_Y2P/A_Y2N | Out | A 通道 LVDS 数据 2 路差分输出正/负端 |

| 26/25 | A_Y3P/A_Y3N | Out | A 通道 LVDS 数据 3 路差分输出正/负端 |

| 28/27 | A_CLKP/A_CLKN | Out | A 通道 LVDS 时钟差分输出正/负端 |

| 48/47 | B_Y0P/B_Y0N | Out | B 通道 LVDS 数据 0 路差分输出正/负端 |

| 46/45 | B_Y1P/B_Y1N | Out | B 通道 LVDS 数据 1 路差分输出正/负端 |

| 44/43 | B_Y2P/B_Y2N | Out | B 通道 LVDS 数据 2 路差分输出正/负端 |

| 40/39 | B_Y3P/B_Y3N | Out | B 通道 LVDS 数据 3 路差分输出正/负端 |

| 42/41 | B_CLKP/B_CLKN | Out | B 通道 LVDS 时钟差分输出正/负端 |

| 数字及控制端口(TTL 电平) | |||

| 1 | SCL | InOut | I2C Master/Slave 的 SCL 管脚 |

| 2 | SDA | InOut | I2C Master/Slave 的 SDA 管脚 |

| 8 | I2C_TYPE | In | 高:SCL/SDA 为 Master,上电复位后自动读取外部 EEPROM的内容,EEPROM 地址为 0xA0; 低:SCL/SDA 为 Slave |

| 7 | I2C_ADDR | In | 1)当 I2C_TYPE 为低时,该芯片的 I2C 地址为: (1) I2C_ADDR 为高, 芯片 I2C 地址为 0x5A; (2) I2C_ADDR=Low, 芯片 I2C 地址为 0x58; 2)当 I2C_TYPE 为高时,外部 EEPROM 的地址为 0xA0。 |

| 6 | IRQ | Out | 通过寄存器配置输出信号 |

| 3 | GPO_0 | Out | 通过寄存器配置输出信号 |

| 4 | GPO_1 | Out | 通过寄存器配置输出信号 |

| 9 | RESERVE | In | 保留管脚,接地。 |

| 12 | EN | In | 芯片使能控制输入端: 1)为高时,芯片正常工作; 2) 为低时,芯片进入关断状态。 |

| 24 | REFCLK | In | 外部参考时钟输入管脚。当不用该管脚的参考时钟时, 该管脚接 GND。 |

| 电源端口 | |||

| 35/38 | VDD_LVDS | Power | 1.8V LVDS 电源,电源纹波≤±100mV |

| 36 | VDD_PLL | Power | 1.8V PLL 电源,电源纹波≤±100mV |

| 10 | VDDIO | Power | 1.8V/3.3V I/O 电源,与 VDD_RX 电压相同,电源波动≤10% |

| 13 | VDD_RX | Power | 1.8V/3.3VMIPI 电源,与 VDDIO 电压相同,电源纹波≤± 10% |

| 11 | Vcore | Power | 芯片内部 1.2V 电源,该管脚必须接到地电容。电容至少 为一个 0.1uF 和一个 1uF 并联。 |

| 37 | VSS_PLL | GND | PLL 地。 |

| 5 | GND | GND | VDDIO 地。 |

| DAP | GND | GND | 芯片地 |

边栏推荐

猜你喜欢

Arduino点亮数码管

cmd控制台窗体大小设置

![[DS3231 RTC real-time clock module and Arduino interface to build a digital clock]](/img/47/ac46e99a6a6dd44aa4478dd48f06a0.png)

[DS3231 RTC real-time clock module and Arduino interface to build a digital clock]

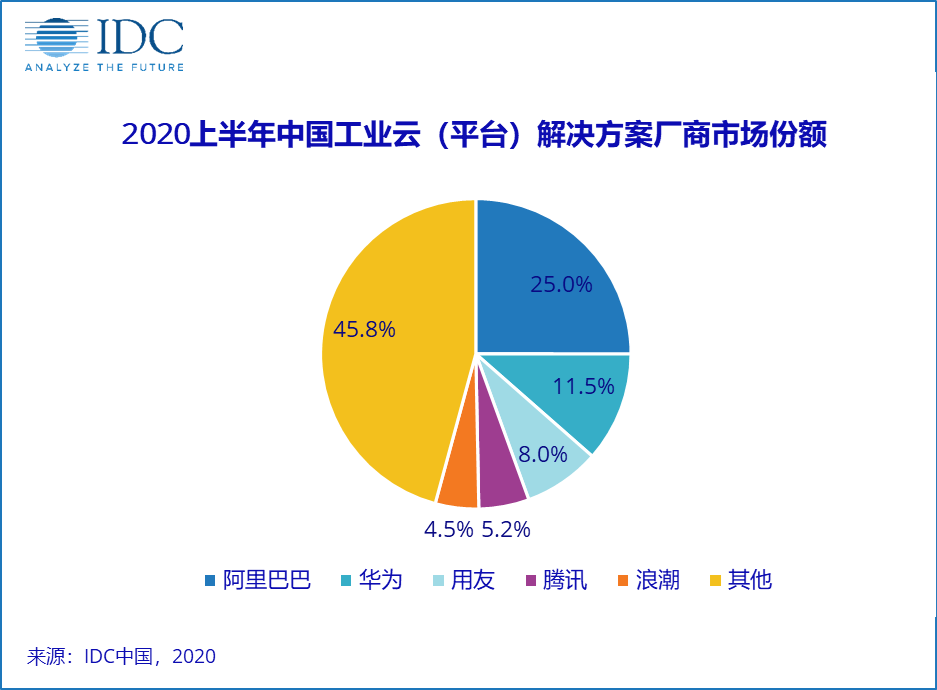

阿里云华为云对比分析

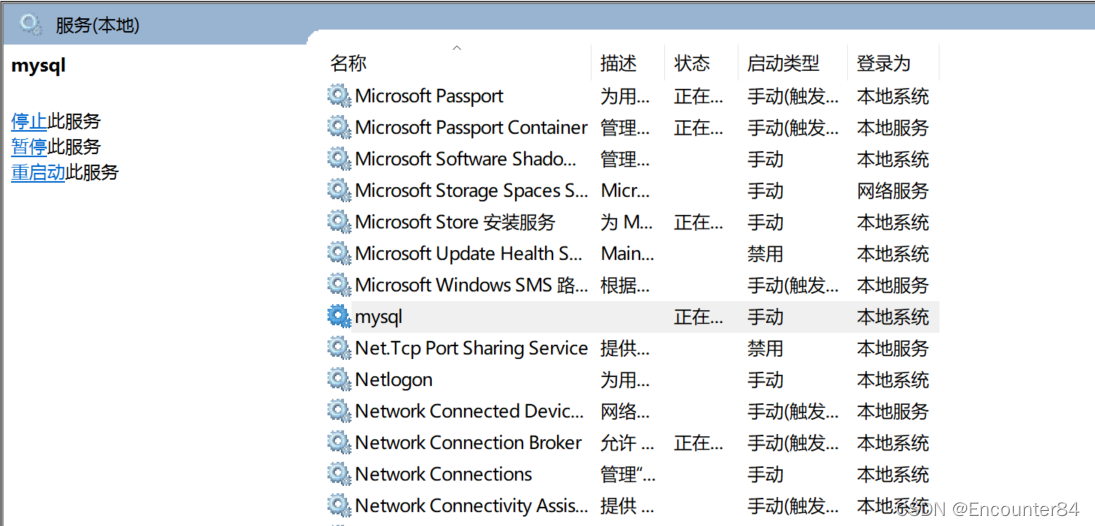

连接本地MySql时出现2003-Can‘t connect to MySql server on ‘localhost‘(10061)

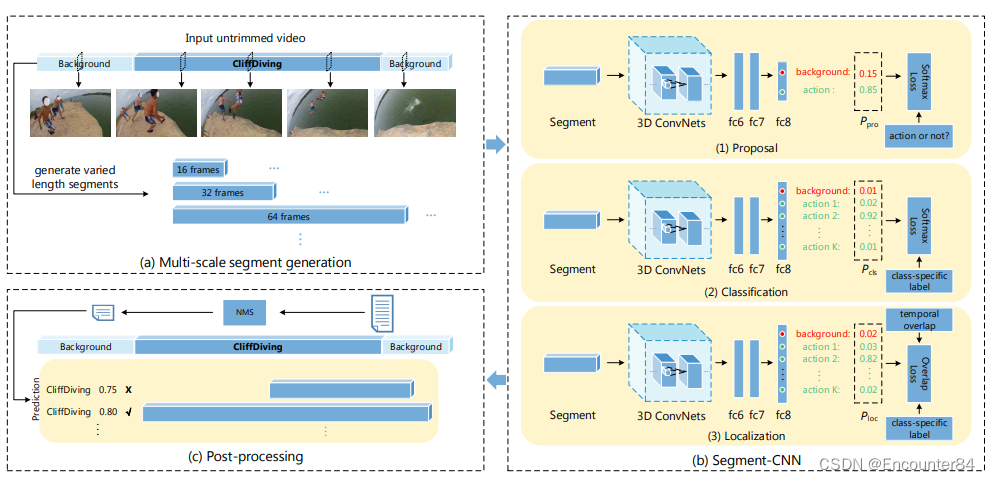

Temporal action localization in untrimmed videos via Multi-stage CNNs SCNN论文阅读笔记

USB2.0一致性测试方法_高速示波器

蓝桥杯:国二选手经验贴 附蓝桥杯历年真题

十大实用的办公工具网站,可以解决你日常100%的问题

单火线开关设计详解

随机推荐

Quo Vadis, Action Recognition? A New Model and the Kinetics Dataset I3D论文精读

C#从入门到精通

自定义view实现半圆弧进度条

Go 程序太大了,能要个延迟初始化不?

uniCloud使用

保证接口数据安全的10种方案

聊一聊数据库的行存与列存

远程调试PLC,到底如何操作?

Modify hosts file using batch script

【Arduino 连接DHT11 湿度和温度传感器】

【Arduino连接GPS 模块 (NEO-6M)读取定位数据】

【科普贴】MDIO接口详解

TQP3M9009电路设计

Flutter入门之网络请求篇

[Spark]-LSH局部敏感哈希

Glide中图片处理

【Popular Science Post】Detailed explanation of MDIO interface

[Spark]-RDD详解之变量&操作

Arduino D1----Mlx90614红外温度传感器接线和安装包

【科普贴】SPI接口详解