当前位置:网站首页>Learn the customization and testing of fpga---ram IP from the bottom structure

Learn the customization and testing of fpga---ram IP from the bottom structure

2022-07-01 05:34:00 【Lonely single blade】

List of articles

2、RAM IP Example and simulation test of

2.1、 Exemplify a RAM IP nucleus

Series catalog and portal

《 Start with the underlying structure FPGA》 Directory and portal

Customizing one RAM IP Before nuclear , It is strongly recommended that you read : Start with the underlying structure FPGA----RAM IP Introduction to nuclear and key parameters . In this article , Have been to RAM IP The key factors of nuclear are explained in detail .

1、RAM IP The custom of

- After creating a new project , Click on IP Catalog

- It will appear after clicking IP Catalog page , stay IP Search in the search box of the kernel block

- According to the screening , Double click to select RAM & ROM nucleus “Block Memory Generator”

①、 first page

②、 The second page

③、 The third page

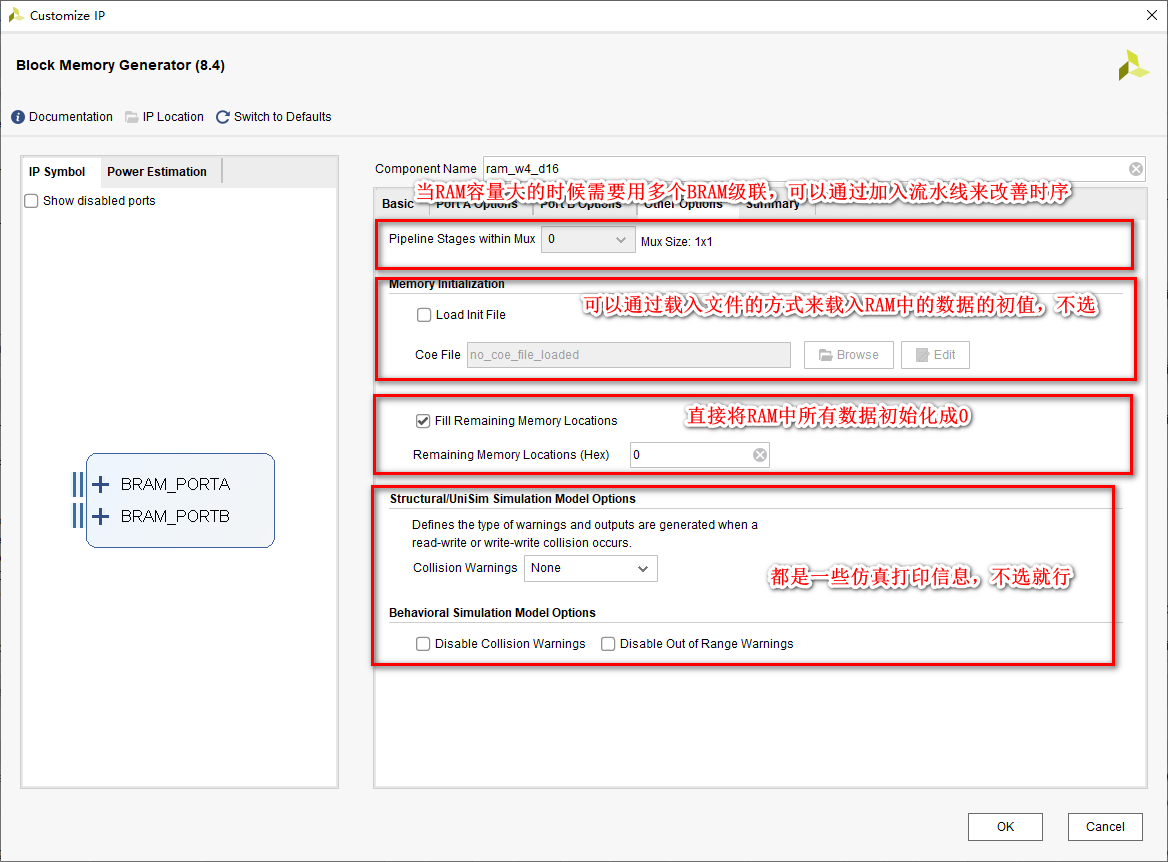

④、 Page four

⑤、 Page 5

2、RAM IP Example and simulation test of

2.1、 Exemplify a RAM IP nucleus

Follow the above steps to generate IP after , Copy IP nucleus The self-contained instantiation template .

And then in our RTL In the code , Instantiate to generate a 4*16 Of SDP RAM.

The RTL No other functions , Only instantiate RAM that will do .

module test(

input clk, // Input clock

input [3:0] data_in, // input data

input en_wr, // Write enable signal

input en_rd, // Read enable signal

input [3:0] addr_wr, // Write the address

input [2:0] addr_rd, // Read the address

input we_wr, // Write enable

output [7:0] data_out // Output data

);

// Exemplification RAM IP nucleus

ram_w4_d16 ram_w4_d16_inst (

// port A-- Write the port

.clka (clk),

.ena (en_wr),

.wea (we_wr),

.addra (addr_wr),

.dina (data_in),

// port B-- Read the port

.clkb (clk),

.enb (en_rd),

.addrb (addr_rd),

.doutb (data_out)

);

endmodule

2.2、 The simulation test

Write a testbench, Yes RAM IP Test it .

Test behavior : First go to the address 0-15 Write data 0-15, And then from the address 0-7 Read the data ( Because the read data bit width is the write data bit width 2 times , So reading the data once will read 2 Write address data ).

`timescale 1ns / 1ns

module tb_test();

reg clk;

reg [3:0] data_in;

reg en_wr;

reg en_rd;

reg [3:0] addr_wr;

reg [2:0] addr_rd;

reg we_wr;

wire [7:0] data_out;

initial begin

clk = 0;

en_wr = 0;en_rd = 0;we_wr = 0;

data_in = 4'd0;

addr_wr = 4'd0;

addr_rd = 3'd0;

#110

en_wr = 1;we_wr = 1; // Start writing data

repeat(15) begin // To address 0-15 Write data 0-15

#10

data_in = data_in + 1;

addr_wr = addr_wr + 1;

end

#10

en_wr = 0; // Stop writing data

en_rd = 1;we_wr = 0; // Start reading data

repeat(10) begin // From address 0-7 Reading data

#10 addr_rd = addr_rd + 1;

end

en_rd = 0; // Stop reading data

#20 $finish; // End the simulation

end

always #5 clk = ~clk; // Generate clock , cycle 10ns

// Instantiate the tested module test

test test_inst(

.clk (clk ),

.data_in (data_in ),

.en_wr (en_wr ),

.en_rd (en_rd ),

.addr_wr (addr_wr ),

.addr_rd (addr_rd ),

.we_wr (we_wr ),

.data_out (data_out )

);

endmoduleUse vivado Built in simulation tools simulator Run the simulation , The simulation results are as follows :

In line with the expected results .

3、 Summary and reference

- You can see RAM IP The customization of is quite simple , After knowing its parameters , It can be fast 、 It is very convenient to instantiate one that you need RAM modular .

- It's not easy to create , If this article helps you , Please give me more praise 、 Reviews and collections . Your support is the biggest driving force for me to continuously update !

Reference material 1:Block Memory Generator v8.4

边栏推荐

- Unity uses SQLite

- And search: the suspects (find the number of people related to the nth person)

- Web Security (x) what is OAuth 2.0?

- CentOS 7使用yum安装PHP7.0

- Multi table operation - foreign key cascade operation

- 第05天-文件操作函数

- How to create a progress bar that changes color according to progress

- 如何开始学剪辑?零基础详细解析

- 基于TI DRV8424驱动步进电机实现调速和行程控制

- Variable binding and deconstruction for rudimentary rust

猜你喜欢

LevelDB源码分析之LRU Cache

C WPF uses dockpanel to realize screenshot box

【QT】qt加减乘除之后,保留小数点后两位

![[RootersCTF2019]babyWeb](/img/b4/aa8f8e107a9dacbace72d4717b1834.png)

[RootersCTF2019]babyWeb

Causes of short circuit of conductive slip ring and Countermeasures

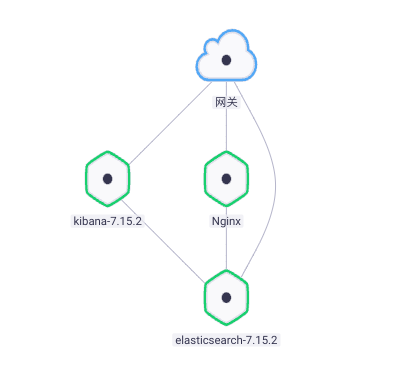

轻松上手Fluentd,结合 Rainbond 插件市场,日志收集更快捷

Unity drags and modifies scene camera parameters under the editor

JDBC常见面试题

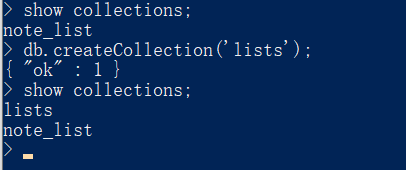

Mongodb学习篇:安装后的入门第一课

Ebpf cilium practice (2) - underlying network observability

随机推荐

Dynamic verification of new form items in El form; El form verifies that the dynamic form V-IF does not take effect;

Application and principle of ThreadPoolExecutor thread pool

ssm+mysql二手交易网站(论文+源码获取链接)

CockroachDB 分布式事务源码分析之 TxnCoordSender

[ffmpeg] [reprint] image mosaic: picture in picture with wheat

el-cascader回显失败;el-cascader回显不出来

Spanner 论文小结

Summary of spanner's paper

担心侵权?必备无版权素材网站分享,不用担心视频剪辑缺素材

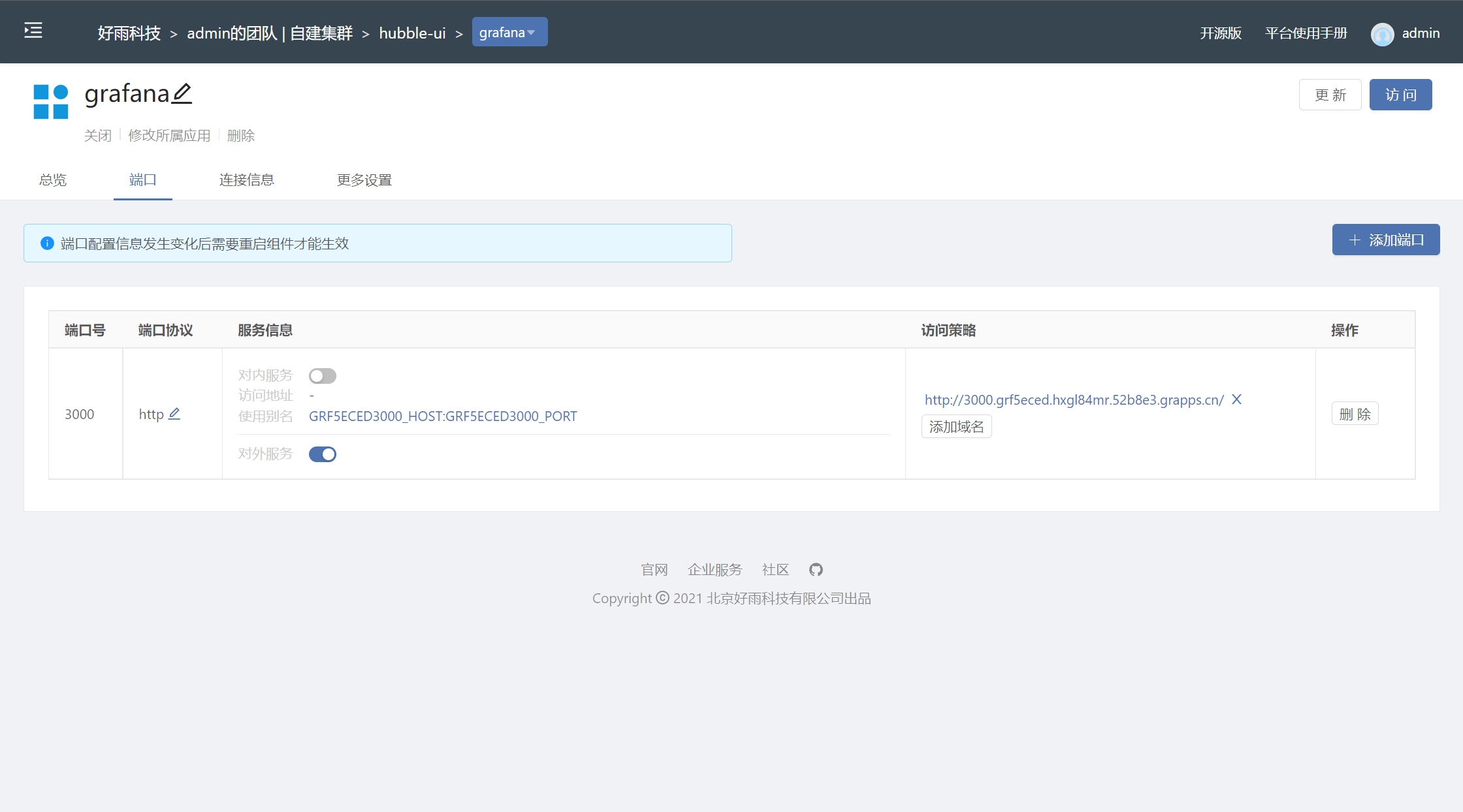

提高企业产品交付效率系列(1)—— 企业应用一键安装和升级

Introduction of 3D Modeling and Processing Software Liu Ligang, Chinese University of Science and Technology

Practice of combining rook CEPH and rainbow, a cloud native storage solution

Txncoordsender of cockroachdb distributed transaction source code analysis

Redis database deployment and common commands

新手在挖财开通证券账户安全吗?

Tar command

Web Security (x) what is OAuth 2.0?

LevelDB源码分析之LRU Cache

了解 JVM 中几个相关问题 — JVM 内存布局、类加载机制、垃圾回收

导电滑环短路的原因以及应对措施