当前位置:网站首页>FPGA刷题——计数器(简易秒表、可置位计数器、加减计数器)

FPGA刷题——计数器(简易秒表、可置位计数器、加减计数器)

2022-07-30 10:29:00 【居安士】

继续牛客网刷题,这篇是计数器部分:

目录

计数器是非常基本的使用,没有计数器就无法处理时序。

简易秒表

这一题实现了秒和分的计数器,当秒计数器从1-60,分计数器+1,当分计数器=60,清零分计数器。用一段always就可以实现,代码如下:

module count_module(

input clk,

input rst_n,

output reg [5:0]second,

output reg [5:0]minute

);

[email protected](posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

second <= 6'd0;

minute <= 6'd0;

end

else begin

if(minute==6'd59)begin

minute <= 6'd60;

end

else if(second == 6'd60)begin

second <= 6'd1;

minute <= minute + 1'b1;

end

else begin

second <= second + 1'b1;

minute <= minute;

end

end

end

endmodule这里需要注意的是计数器的初值,比如计数器60次一清零,如果清零时为计数器赋0,那么清零的条件应该写60-1(0~59是60个数)如果清零时为计数器赋1,那么清零的条件应该写60

可置位计数器

题目要求编写一个十六进制计数器,即输出数值number每次变化1,在0-15之间循环。输出set信号的值为一时,将输出数值num置为set_num。

module count_module(

input clk,

input rst_n,

input set,

input [3:0] set_num,

output reg [3:0]number,

output reg zero

);

reg [3:0]num;

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

zero <= 1'd0;

end

else if (num == 4'd0)

begin

zero <= 1'b1;

end

else

begin

zero <= 1'b0;

end

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

num <= 4'b0;

end

else if(set)

begin

num <= set_num;

end

else

begin

num <= num + 1'd1;

end

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

number <= 1'd0;

end

else

begin

number <= num;

end

endmodule加减计数器

题目要求编写一个十进制计数器,即输出数值number每次变化1,在0-9之间循环。根据mode信号的值,更改输出数值number的变化方向。当mode=1,计数器递增。当mode=0,计数器递减。可以将mode作为判断条件,使用if-else语句实现不同的变化方向。

注意,这一题的zero信号是用时序逻辑来赋值,利用number的过程值num进行判断;

- 题目的testbench要求输出都延后一个时钟,因此增加一个寄存器tmp来暂存计数。

- 根据mode来判断计数何时跳变;zero输出时刻在tmp为0的下一周期,因此用tmp==0来判断。

module count_module(

input clk,

input rst_n,

input mode,

output reg [3:0]number,

output reg zero

);

reg [3:0]num;

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

zero <= 1'd0;

end

else if (num == 4'd0)

begin

zero <= 1'b1;

end

else

begin

zero <= 1'b0;

end

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

num <= 4'b0;

end

else if(mode)

begin

if(num == 9)

num <= 0;

else

num <= num + 1'd1;

end

else if(!mode)

begin

if(num == 0)

num <= 9;

else

num <= num - 1'd1;

end

else num <= num;

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

number <= 4'd0;

end

else

begin

number <= num;

end

endmodule从上面三道题可以看出,计数器基本都使用 if-else 语句进行实现,使用if-else语句时,要注意代码是从上到下执行,如果if里面的语句可以实现,就不会跳转到else,因此,应该把条件判断的部分(不容易实现的部分)写在最前面,以此类推。

边栏推荐

- Beyond Stream Processing !第四届实时计算 Flink 挑战赛启动,49 万奖金等你来拿!

- The method of parameter passing

- SST-Calib:结合语义和VO进行时空同步校准的lidar-visual外参标定方法(ITSC 2022)

- 死锁的理解

- 关于verilog的时延研究

- 神经网络学习笔记3——LSTM长短期记忆网络

- Soft test system architects introductory tutorial | system operation and software maintenance

- 阿里云OSS对象存储

- Re17: Read the paper Challenges for Information Extraction from Dialogue in Criminal Law

- 数据库脏读、不可重复读、幻读以及对应的隔离级别

猜你喜欢

AB测试 总结归纳

typescript入门之helloworld

![[Deep Learning] (Problem Record) <What do I get by calculating the gradient of a variable> - Linear Regression - Small Batch Stochastic Gradient Descent](/img/28/834aac16859fd26ab69de30f5fed55.png)

[Deep Learning] (Problem Record)

- Linear Regression - Small Batch Stochastic Gradient Descent

Meikle Studio-Look at Hongmeng Device Development Practical Notes 7-Network Application Development

梅科尔工作室-看鸿蒙设备开发实战笔记五——驱动子系统开发

Neural Network Study Notes 3 - LSTM Long Short-Term Memory Network

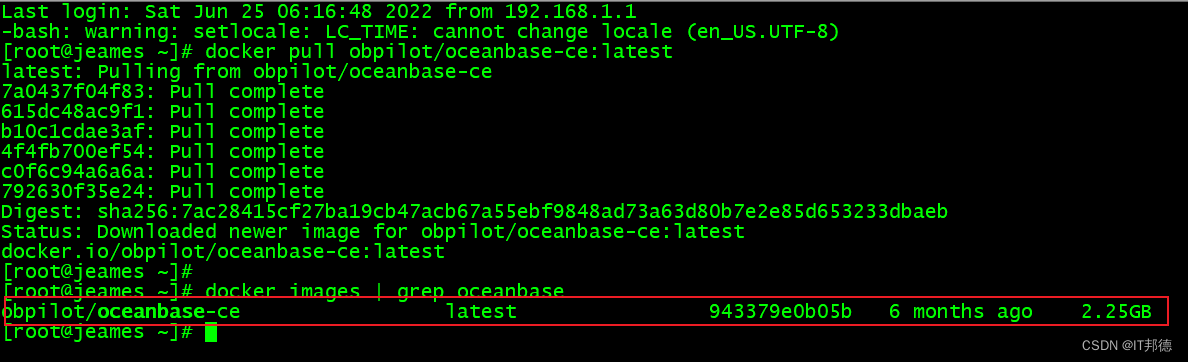

【云原生】-Docker安装部署分布式数据库 OceanBase

唯物辩证法-条件论

Classes and Objects - 6 Default Member Functions

死锁的理解

随机推荐

阿里云OSS对象存储

Flink_CDC construction and simple use

Neural Network Study Notes 4 - Autoencoder (including sparse, stacked) (updated)

Security tip: FreeType in Qt

TestNg整合Retry代码

spark udf 接受并处理 null值.

Quick Start Tutorial for flyway

[100 Solidity Skills] 1. Contract reentrancy attack

Soft Exam System Architect Concise Tutorial | Case Analysis | Requirement Analysis

Classes and Objects - 6 Default Member Functions

Scrapy crawler website image crawling

电压跟随器不要随便加

Swift 常用扩展类和简单封装

Domino Server SSL Certificate Installation Guide

Meikle Studio-Look at the actual combat notes of Hongmeng device development six-wireless networking development

In 2022, the top will be accepted cca shut the list

WEB3之路(一)-- solidity学习笔记

死锁的理解

New in GNOME: Warn users when Secure Boot is disabled

kubernetes的一些命令