当前位置:网站首页>Chapter VI exercises (678) [microcomputer principles] [exercises]

Chapter VI exercises (678) [microcomputer principles] [exercises]

2022-06-26 00:49:00 【Sun star moon cloud】

Chapter six exercises 【 Microcomputer principle 】【 exercises 】

Preface

The following is derived from the principle of Microcomputer ( The Fourth Edition ) Edited by Wang Zhongmin

For learning and communication only

Please read the article statement , By default, I agree with this statement

recommend

Chapter six Semiconductor memory 【 Microcomputer principle 】

Chapter six exercises

Negative logic and gate

Symbol

Is to add a small circle at the input and output of the positive logic and gate

Truth table

Let's start with positive logic and gates

Positive logic and gate Truth table

0 Invalid 1 It works

Only the whole 1 Only then 1

| A | B | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Negative logic and gate Truth table

0 It works 1 Invalid

Only the whole 0 Only then 0

| A | B | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

It is the same as the truth table of positive logic or gate

6

6、 It is known that :8 Bit microcomputer address , Bus 16 position , Design 12KB The storage system , among ROM Occupy 0000H At the beginning 8KB,RAM Occupy 2000H At the beginning 4KB, Memory chips are selected respectively INTEL 2716 and 2114

The analysis is as follows :

(1)

ROM 8Kx8 2716 2K×8 chip , Need to be 4 slice , Do word expansion , On chip addressing line 11 root

RAM 4kx8 2114 1K×4 chip , Need to be 8 slice , Do bit expansion , On chip addressing line 10 root

(2) Address range : A15 A14 A13 A12 A11 A10 A9~A0

0k

ROM1:0000H~07FFH 0 0 0 0 0 whole 0~ whole 1

+2K

ROM2:0800H~0FFFH 0 0 0 0 1 whole 0~ whole 1

+2K

ROM3:1000H~17FFH 0 0 0 1 0 whole 0~ whole 1

+2K

ROM4:1800H~1FFFH 0 0 0 1 1 whole 0~ whole 1

8k

RAM1、2:2000H~23FFH 0 0 1 0 0 0 whole 0~ whole 1

+1K

RAM3、4:2400H~27FFH 0 0 1 0 0 1 whole 0~ whole 1

+1K

RAM5、6:2800H~2BFFH 0 0 1 0 1 0 whole 0~ whole 1

+1K

RAM7、8:2C00H~2FFFH 0 0 1 0 1 1 whole 0~ whole 1

12k

(3)

A13 A12 A11 3:8 Decoder Decoding input ( First level decoding )

0 0 0 ROM1 :!Y0

0 0 1 ROM2 :!Y1

0 1 0 ROM3 :!Y2

0 1 1 ROM4 :!Y3

1 0 0 RAM1、2 :!Y4 And A10 ( Two stage decoding ) This and is a negative logical and

0

1 0 0 RAM3、4 :!Y4 And A10

1

1 0 1 RAM5、6 :!Y5 And A10

0

1 0 1 RAM7、8 :!Y5 And A10

1

Ignore the following

(3)

A13 A12 A11 A10 4-16 Decoder Decoding input ( First level decoding )

0 0 0 1 ROM1 :!Y1

0 0 1 1 ROM2 :!Y3

0 1 0 1 ROM3 :!Y5

0 1 1 1 ROM4 :!Y7

1 0 0 0 RAM1、2 :!Y8

1 0 0 1 RAM3、4 :!Y9

1 0 1 0 RAM5、6 :!Y10

1 0 1 1 RAM7、8 :!Y11

Ignore the above

(4) Draw connections

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2716

2716

2716

2716

7

7 existing Inter 6264(8 K X 8) static state RAM Several memory chips , It is required to design one 64K X 8 Memory system , Its address bus is 16 position (A0 ~ A15), Address range is 0000~FFFFH.

The analysis is as follows :

(1)

RAM 64K X 8 6264 8 K X 8 chip need 8 slice , Do word expansion , On chip addressing line 13 root

(2) Address range : A15 A14 A13 A12~A0

0k

RAM1 0000H~1FFFH 0 0 0 whole 0~ whole 1

+8k

RAM2 2000H~3FFFH 0 0 1 whole 0~ whole 1

+8k

RAM3 4000H~5FFFH 0 1 0 whole 0~ whole 1

+8k

RAM4 6000H~7FFFH 0 1 1 whole 0~ whole 1

+8k

RAM5 8000H~9FFFH 1 0 0 whole 0~ whole 1

+8k

RAM6 A000H~BFFFH 1 0 1 whole 0~ whole 1

+8k

RAM7 C000H~DFFFH 1 1 0 whole 0~ whole 1

+8k

RAM8 E000H~FFFFH 1 1 1 whole 0~ whole 1

64k

(3)

A15 A14 A13 3:8 Decoder Decoding input ( First level decoding )

0 0 0 RAM1 :!Y0

0 0 1 RAM2 :!Y1

0 1 0 RAM3 :!Y2

0 1 1 RAM4 :!Y3

1 0 0 RAM5 :!Y4

1 0 1 RAM6 :!Y5

1 1 0 RAM7 :!Y6

1 1 1 RAM8 :!Y7

(4) Draw connections

Word extension A15 A14 A13 3-8 Decoder CS

6264

6264

6264

6264

6264

6264

6264

6264

8

8. Of a microcomputer system CPU The word is 8 position , The address signal line is 16 root . After power on reset , Program counter

PC Point to 0000H Address storage unit . Required 2716 EPROM chip (2Kx8) form 4KB Of ROM Store the system monitoring program , And reserve 4KB Users of ROM Space ; Use 2114SRAM chip (1Kx4) form 8KB System and users RAM. Try to design the memory system of the machine .

(1)

ROM 8K X 8 2716 2 K X 8 chip need 4 slice , Do word expansion , On chip addressing line 11 root

RAM 8K X 8 2114 1 K X 4 chip need 16 slice , Do bit expansion , On chip addressing line 10 root

(2) Address range : A15 A14 A13 A12 A11 A10 A9~A0

0k

ROM1:0000H~07FFH 0 0 0 0 0 whole 0~ whole 1

+2K

ROM2:0800H~0FFFH 0 0 0 0 1 whole 0~ whole 1

+2K

ROM3:1000H~17FFH 0 0 0 1 0 whole 0~ whole 1

+2K

ROM4:1800H~1FFFH 0 0 0 1 1 whole 0~ whole 1

8k

RAM1、2:2000H~23FFH 0 0 1 0 0 0 whole 0~ whole 1

+1K

RAM3、4:2400H~27FFH 0 0 1 0 0 1 whole 0~ whole 1

+1K

RAM5、6:2800H~2BFFH 0 0 1 0 1 0 whole 0~ whole 1

+1K

RAM7、8:2C00H~2FFFH 0 0 1 0 1 1 whole 0~ whole 1

+1K

RAM9、10:3000H~33FFH 0 0 1 1 0 0 whole 0~ whole 1

+1K

RAM11、12:3400H~37FFH 0 0 1 1 0 1 whole 0~ whole 1

+1K

RAM13、14:3800H~3BFFH 0 0 1 1 1 0 whole 0~ whole 1

+1K

RAM15、16:3C00H~3FFFH 0 0 1 1 1 1 whole 0~ whole 1

16K

(3)

A13 A12 A11 3-8 Decoder Decoding input ( First level decoding )

0 0 0 ROM1 :!Y0

0 0 1 ROM2 :!Y1

0 1 0 ROM3 :!Y2

0 1 1 ROM4 :!Y3

1 0 0 RAM1、2 :!Y4 And A10 ( Two stage decoding ) This and is a negative logical and

0

1 0 0 RAM3、4 :!Y4 And A10

1

1 0 1 RAM5、6 :!Y5 And A10

0

1 0 1 RAM7、8 :!Y5 And A10

1

1 1 0 RAM9、10 :!Y6 And A10

0

1 1 0 RAM11、12 :!Y6 And A10

1

1 1 1 RAM13、14 :!Y7 And A10

0

1 1 1 RAM15、16 :!Y7 And A10

1

Ignore the following

(3)

A13 A12 A11 A10 4-16 Decoder Decoding input ( First level decoding )

0 0 0 1 ROM1 :!Y1

0 0 1 1 ROM2 :!Y3

0 1 0 1 ROM3 :!Y5

0 1 1 1 ROM4 :!Y7

1 0 0 0 RAM1、2 :!Y8

1 0 0 1 RAM3、4 :!Y9

1 0 1 0 RAM5、6 :!Y10

1 0 1 1 RAM7、8 :!Y11

1 1 0 0 RAM9、10 :!Y12

1 1 0 1 RAM11、12 :!Y13

1 1 1 0 RAM13、14 :!Y14

1 1 1 1 RAM15、16 :!Y15

Ignore the above

----16k

Word extension A13 A12 A11 A10 3-16 Decoder control cs

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

----8k

2716

2716

----4k

2716

2716

Last

Please read the article statement , By default, I agree with this statement

Reward channels

边栏推荐

- 1-10vmware builds customized network architecture

- “Method Not Allowed“,405问题分析及解决

- 统一网关Gateway

- Installation and configuration of gradle environment

- Balanced binary tree AVL

- [TSP problem] solving traveling salesman problem based on Hopfield neural network with matlab code

- 1-9Vmware中网络配置

- How to deliver a shelter hospital within 48 hours?

- Leetcode 513. Find the value in the lower left corner of the tree

- [image detection] vascular tracking and diameter estimation based on Gaussian process and Radon transform with matlab code

猜你喜欢

Xiaohongshu microservice framework and governance and other cloud native business architecture evolution cases

Nacos注册中心

鼠标拖拽围绕某个物体旋转展示

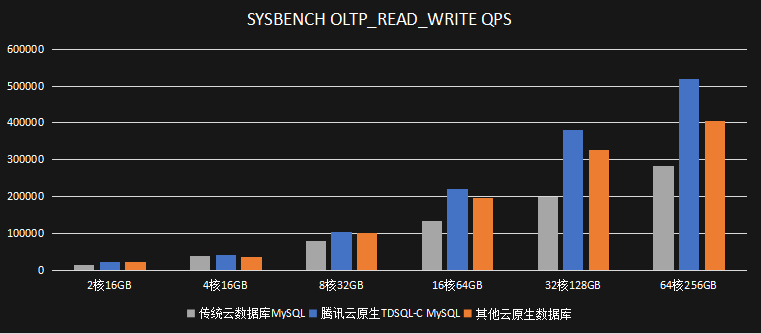

性能领跑云原生数据库市场!英特尔携腾讯共建云上技术生态

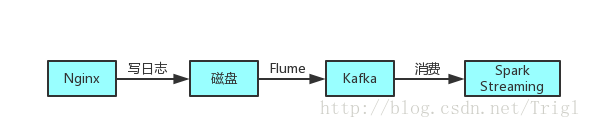

Stream data

Example: use C # Net to teach you how to develop wechat official account (21) -- using wechat to pay online collection: H5 method

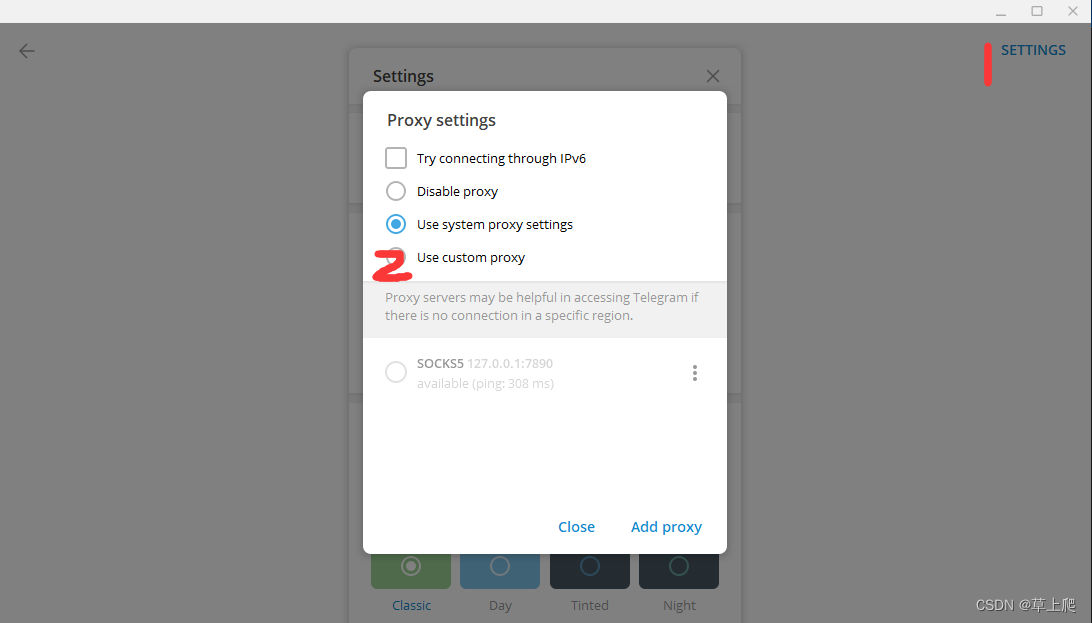

使用VS2022編譯Telegram桌面端(tdesktop)

Leetcode 513. Find the value in the lower left corner of the tree

Core ideas of SQL optimization

86. (cesium chapter) cesium overlay surface receiving shadow effect (gltf model)

随机推荐

Precautions for cleaning PCBA board in SMT chip processing

【超能云终端创领先机】如何在48小时内交付一座方舱医院?

Correct writing methods of case, number and punctuation in Chinese and English papers

What are the red lines of open source that should not be trodden on?

Penetration tool -burpsuite

Idea view unit test coverage

Methods to realize asynchrony

213. house raiding II

MySQL custom function instance

After being trapped by the sequelae of the new crown for 15 months, Stanford Xueba was forced to miss the graduation ceremony. Now he still needs to stay in bed for 16 hours every day: I should have e

QT excellent open source project 9: qtox

Megacli common command collation

[OEM special event] in the summer of "core cleaning", there are prize papers

Idea set the template of mapper mapping file

鼠标拖拽围绕某个物体旋转展示

【TSP问题】基于Hopfield神经网络求解旅行商问题附Matlab代码

Permission design = function permission + Data permission

Atlas200dk刷机

Mysql5.7.31 user defined installation details

js数组中修改元素的方法