当前位置:网站首页>Miscellaneous instructions of arm instruction set

Miscellaneous instructions of arm instruction set

2022-06-12 11:50:00 【fanxiaoyu321】

List of articles

This note records the following categories ARM Instructions :

- Status register access instruction ;

- Semaphore operation instruction ;

- An abnormal interrupt generates an instruction ;

Status register access instruction

ARM Two instructions are provided to exchange data directly between the status register and the general-purpose register .

- MRS:Move Register <-- State, Transfer the value of the status register to the general-purpose register ;

- MSR:Move State <-- Register, Transfer the value of the general register to the status register of the ;

When operating the status register , We should pay attention to the following points :

- Unused bits in the status register should not be modified ;

- T Flag bits should not be manually modified , Only through BX Command to modify ;

- Access to the status register should follow “ Read - modify - Write back to ” The order of ;

MRS

MRS{<cond>} <Rd>, CPSR

MRS{<cond>} <Rd>, SPSR

if CondPassed(cond) then

if R == 1 then

Rd = SPSR

else

Rd = CPSR

MSR

MSR{<cond>} CPSR_<fields>, #<immediate>

MSR{<cond>} CPSR_<fields>, <Rm>

MSR{<cond>} SPSR_<fields>, #<immediate>

MSR{<cond>} SPSR_<fields>, <Rm>

if CondPassed(cond) then

if opcode[25] == 1 then

operand = 8bit_immediate >> (rotate_imm * 2)

else

operand = Rm

if R == 0 then

if field_mask[0] == 1 and InAPrivilegedMode() then

CPSR[7:0] = operand[7:0]

if field_mask[1] == 1 and InAPrivilegedMode() then

CPSR[15:8] = operand[15:8]

if field_mask[2] == 1 and InAPrivilegedMode() then

CPSR[23:16] = operand[23:16]

if field_mask[3] == 1 and InAPrivilegedMode() then

CPSR[31:24] = operand[31:24]

else

if field_mask[0] == 1 and InAPrivilegedMode() then

SPSR[7:0] = operand[7:0]

if field_mask[1] == 1 and InAPrivilegedMode() then

SPSR[15:8] = operand[15:8]

if field_mask[2] == 1 and InAPrivilegedMode() then

SPSR[23:16] = operand[23:16]

if field_mask[3] == 1 and InAPrivilegedMode() then

SPSR[31:24] = operand[31:24]

among <fields> Press the status register as 8bit One group is divided into 4 Domains , The distribution is as follows :

| bits | fields Mark | explain |

|---|---|---|

| bits[31:24] | f | Conditional flag bit field |

| bits[23:16] | s | Status bit field |

| bits[15:8] | x | Extension bit field |

| bits[7:0] | c | Control bit field |

Semaphore operation instruction

Software programming , Semaphores are usually used for mutual exclusion between processes , The foundation for this requires an atomic operation , That is, read and modify semaphores in one instruction ,ARM Two instructions are provided to complete the signal operation .

- SWP: Word exchange instruction ;

- SWPB: Byte exchange instruction ;

SWP Word exchange instruction

SWP Put the memory unit ( Address Rn) The value in is read to Rd in , At the same time, register Rm Write to the memory unit , If Rd and Rm For the same register , Then it is equivalent to exchanging the contents of registers and memory cells .

SWP{<cond>} <Rd>, <Rm>, [<Rn>]

if CondPassed(cond) then

if Rn[1:0] == 0b00 then

temp = Mem[Rn, 4]

elif Rn[1:0] == 0b01 then

temp = Mem[Rn, 4] >> 8

elif Rn[1:0] == 0b10 then

temp = Mem[Rn, 4] >> 16

elif Rn[1:0] == 0b11 then

temp = Mem[Rn, 4] >> 24

Mem[Rn, 4] = Rm

Rd = temp

SWPB Byte exchange instruction

and SWP Instruction similar , The only difference is that the instructions exchange 8bit byte .

SWPB{<cond>} <Rd>, <Rm>, [<Rn>]

if CondPassed(cond) then

temp = Mem[Rn, 4]

Mem[Rn, 4] = Rm

Rd = temp

An abnormal interrupt generates an instruction

ARM Two instructions are provided for the software to actively trigger abnormal interrupts :

- SWI: Soft interrupt instruction . This instruction can generate SWI abnormal ,ARM This instruction can be used to call the program in privileged mode in the operating system in user mode , That is, the basis of system call implementation ;

- BKPT: Breakpoint interrupt instruction . seeing the name of a thing one thinks of its function , This instruction is used to generate software endpoints , For use by the debugger ;

SWI Soft interrupt instruction

SWI{<cond>} <immed_24>

if CondPassed(cond) then

R14_svc = address of next instruction after then SWI instruction

SPSR_svc = CPSR

CPSR[4:0] = 0b10011 // Enter SVC Pattern

CPSR[5] = 0 // ARM Pattern

CPSR[7] = 1 // close IRQ, But don't close FIQ

if high vectors configured then

PC = 0xFFFF_0008

else

PC = 0x0000_0008

BKPT Breakpoint interrupt instruction

BKPT <immed_16>

if (not overriden by debug hardware)

R14_abt = address of BKPT instruction + 4

SPSR_abt = CPSR

CPSR[4:0] = 0b10111 // Enter ABT Pattern

CPSR[5] = 0 // ARM Pattern

CPSR[7] = 1 // close IRQ, But don't close FIQ

if high vectors configured then

PC = 0xFFFF_000C

else

PC = 0x0000_000C

边栏推荐

- When you have a server

- ARM指令集之跳转指令

- K53. Chapter 2 installing kubernetes v1.22 based on binary packages -- cluster deployment

- 当自己有台服务器之后

- QT based travel query and simulation system

- Windows10安装mysql-8.0.28-winx64

- Windows10 install mysql-8.0.28-winx64

- 【藍橋杯單片機 國賽 第十一届】

- Analyze the implementation principle of the onion model, and connect the onion model in your own project

- TinyMCE series (I) TinyMCE environment construction

猜你喜欢

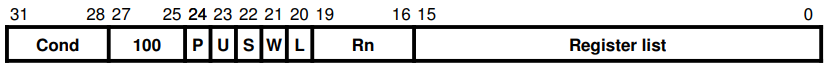

ARM指令集之批量Load/Store指令

![[the 11th national competition of Blue Bridge Cup single chip microcomputer]](/img/da/3c8a9efd5b28f67816f239531a0339.png)

[the 11th national competition of Blue Bridge Cup single chip microcomputer]

K52. Chapter 1: installing kubernetes v1.22 based on kubeadm -- cluster deployment

【深度学习基础】神经网络的学习(4)

JS to load and display Excel files

5g NR Protocol Learning - - ts38.211 downlink channel

C# 35. Select default network card

VirtualBox virtual machine shut down due to abnormal system. The virtual machine startup item is missing

QT添加QObject类(想使用信号和槽)遇到的问题汇总,亲测解决有效error: undefined reference to `vtable for xxxxxx(你的类名)‘

Rich text editor copying pictures in word documents

随机推荐

[the 11th national competition of Blue Bridge Cup single chip microcomputer]

PDSCH related

B.刷墙(C语言)

Cookie和Session

PDSCH 相关

Go sends SMS based on alicloud

Byte order (network / host) conversion

Google Earth Engine(GEE)——Kmeans聚类快速进行土地分类(双for循环快速调参)

Network topology

6.6 RL:MDP及奖励函数

Mysql45 lecture 01 | infrastructure: how is an SQL query executed?

UML系列文章(30)体系结构建模---制品图

Analyze the implementation principle of the onion model, and connect the onion model in your own project

TinyMCE series (II) TinyMCE plug-in development

Unity connect to Microsoft SQLSERVER database

Reasons for SSL introduction and encryption steps

Deep learning and CV tutorial (14) | image segmentation (FCN, segnet, u-net, pspnet, deeplab, refinenet)

Inter class and intra class relations in video classification -- regularization

【藍橋杯單片機 國賽 第十一届】

5g NR Protocol Learning - - ts38.211 downlink channel