当前位置:网站首页>Section 5: zynq interrupt

Section 5: zynq interrupt

2022-06-28 07:35:00 【youbin2013】

ZYNQ interrupt

1 Interrupt type

ARM Processor support 7 An abnormal situation : Reset 、 Undefined instruction 、 Instruction prefetching terminated 、 Data termination 、 Interrupt request (IRQ) And quick interrupt request (FIQ).

Reset (RESET): But when the reset pin of the processor is valid , The system has reset abnormal interrupt , Program jumps to reset exception interrupt handler for execution . Reset abnormal interrupt is usually used in the following two cases , First, when the system is powered on and reset ; The second is to jump to the reset interrupt vector ;

Data access aborted (data abort): If the destination address of the data access instruction does not exist , Or the address does not allow the current instruction to access , The processor generates a data access abort exception interrupt ;

Fast interrupt request (FIQ): When the external fast interrupt request pin of the processor is valid , and CPSR The register of F When the control bit is cleared , The processor generates an external interrupt request (FIQ) Abnormal interruption ;

External interrupt request (IRQ): When the external interrupt request pin of the processor is valid , and CPSR The register of I When the control bit is cleared , The processor generates an external interrupt request (IRQ) Abnormal interruption . The peripherals in the system usually request the processor service through this abnormal interrupt ;

Prefetch instruction aborted (prefech abort): If the address of the processor prefetch instruction does not exist , Or the address does not allow the current instruction to access , When the prefetched instruction is executed , The processor generates an instruction prefetch abort exception interrupt ;

Software interrupt (software interrupt SWI): This is a user-defined interrupt instruction , It can be used for program call privilege operation instructions in user mode . In real-time operating systems (RTOS) The system function call can be realized through this mechanism ;

Undefined instructions (undefined instructin): When ARM When the processor or coprocessor in the system thinks that the current instruction is undefined , An undefined instruction exception interrupt is generated , Floating point vector operation can be simulated through this abnormal interrupt mechanism .

2 Interrupt architecture

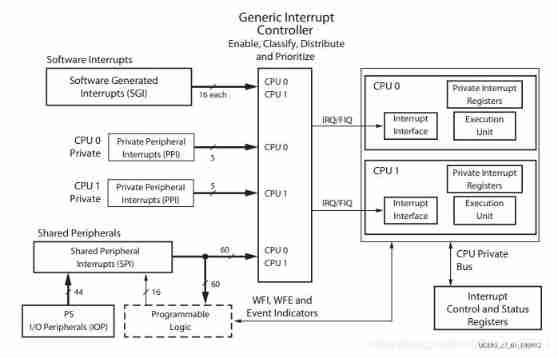

Zynq There are two cortex-a9 The processor and GIC pl390 Interrupt controller , The interrupt architecture is shown in the figure 1 Shown . Interrupt types mainly include private interrupts 、 Software interrupts and shared interrupts , In its architecture, the general interrupt controller is used to manage interrupts .

Every CPU There is a set of private peripheral interrupts (PPI),PPI Including global timer 、 Private watchdog timer 、 Private timer and from PL Of FIQ/IRQ.

Software interrupt (SGI) Connect to one of CPU Or all of it CPU, By writing ICDSGIR Register generation SGI.

Sharing interrupted (SPI) It's through PS and PL Internal variety I/O And memory controller . chart 2 The interrupt source is given , They are connected to one of them CPU Or all of it CPU.

General interrupt controller (GIC) Is the core resource , Used to manage from PS perhaps PL The interrupt , These interrupts are sent to CPU.

chart 1 Interrupt architecture

GIC Used to classify hundreds of interrupt sources in the system 、 President, etc , It is the core component of system interrupt processing , Its position in the whole system is shown in the figure 1 Shown .GIC Between the interrupt source and CPU Between , Be responsible for controlling the interrupt trigger signal 、 classification 、 code 、 Priority setting and other operations , Finally, the interrupt signal is sent to CPU. Send in CPU Each interrupt signal of has a unique ID code ,CPU By inquiring ID Coding can determine the location of the interrupt source , The internal structure is shown in the figure 2 Shown .

chart 2 Interrupt controller framework

interrupt ID surface :

Software interrupt SGI The interrupt ID Distribution as shown in the table 1 Shown .

surface 1 SGI interrupt ID

CPU Private peripheral interrupt PPI The interrupt ID Distribution as shown in the table 2 Shown .

surface 2 PPI interrupt ID

Shared peripheral interrupt SPI The interrupt ID Distribution as shown in the table 3 Shown

3 Timer interrupt usage instance

Zynq The following features of the private timer on the :

1,32 Bit counter , When it reaches zero , Create an interrupt ;

2,8 Bit prescaler , It can better control the interrupt cycle ;

3, Configurable one-time or automatic reload mode ;

4,2 The second time interval can be calculated by : The time interval =[( Prescaler value +1)( Load values +1)]/ The timer frequency . All private timers and Watchdog Timers always work at CPU Frequency 1/2(CPU_3x2x).

The steps to configure the private timer are as follows :

First of all ,GIC Initialization of interrupt controller

- Connect to hardware , Map the corresponding interrupt to GIC Interrupt request ;

- find GIC interrupt , fill GIC Interrupt register base address and some related information ;

- Find the timer interrupt source , Fill in timer interrupt register base address and some related information ;

- Map timer interrupt to interrupt service function of timer interrupt ;

- Time can GIC interrupt ;

- Mapping between interrupt vector table and interrupt vector table ;

second , Initialization of timer peripherals :

- Find the timer peripheral , Fill in timer peripheral register base address and some related information ;

- Timer peripheral self-test ;

- Load timer timing time ;

- Enable automatic reload function ;

- Timer peripheral interrupt ;

- Start timer ;

- Write timer interrupt service function ;

initialization GIC Source code :

void Init_GIC_Timer(void)

{

XScuGic_Config *IntcConfig;

//1,GIC The initialization

//connect to hardware

Xil_ExceptionInit();

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_IRQ_INT,

(Xil_ExceptionHandler)XScuGic_InterruptHandler,

(void *)&Intc);

//find device

IntcConfig = XScuGic_LookupConfig(INTC_DEVICE_ID);

//config XScuGic data

XScuGic_CfgInitialize(&Intc, IntcConfig,IntcConfig->CpuBaseAddress);

//GIC connect to handler

XScuGic_Connect(&Intc, TIMER_IRPT_INTR,(Xil_ExceptionHandler)TimerIntrHandler,(void*)&Timer);

//enable xscugic

XScuGic_Enable(&Intc,TIMER_IRPT_INTR);

//enable exception

Xil_ExceptionEnable();

Xil_ExceptionEnableMask(XIL_EXCEPTION_IRQ);

}

Timer peripheral initialization source code :

void Init_Timer(void)

{

XScuTimer_Config *TMRConfigPtr;

//2, Private timer initialization

//find device

TMRConfigPtr = XScuTimer_LookupConfig(TIMER_DEVICE_ID);

//config XScuTimer data

XScuTimer_CfgInitialize(&Timer,TMRConfigPtr,TMRConfigPtr->BaseAddr);

//self test

XScuTimer_SelfTest(&Timer);

//loader value

XScuTimer_LoadTimer(&Timer,TIMER_LOAD_VALUE);

//enable auto reload

XScuTimer_EnableAutoReload(&Timer);

//enable interrupt

XScuTimer_EnableInterrupt(&Timer);

//start timer

XScuTimer_Start(&Timer);

}

Timer interrupt service function source code :

void TimerIntrHandler(void *CallBackRef)

{

staticint sec = 0;

XScuTimer* TimerInstancePtr = (XScuTimer*)CallBackRef;

XScuTimer_ClearInterruptStatus(TimerInstancePtr);

sec++;

printf("%d Second\n\r",sec);

}

边栏推荐

- Path alias specified in vite2.9

- Kubelet garbage collection (exiting containers and unused images) source code analysis

- Top 25 most popular articles on vivo Internet technology in 2021

- Self discipline challenge 30 days

- goland IDE和delve调试位于kubernetes集群中的go程序

- Application and Optimization Practice of redis in vivo push platform

- Force buckle 515 Find the maximum value in each tree row

- Huawei cloud computing physical node cna installation tutorial

- Devtools implementation principle and performance analysis practice

- Is it safe for flush to open an account online

猜你喜欢

kubelet垃圾(退出的容器和未使用的镜像)回收源码分析

vite2.9 中指定路径别名

Vivo browser rapid development platform practice - Overview

Practice of traffic recording and playback in vivo

2021 programming language ranking summary

Comment la passerelle BACnet / IP recueille - t - elle les données du système central de contrôle des bâtiments?

The practice of traffic and data isolation in vivo Reviews

No suspense about the No. 1 Internet company overtime table

卸载重装最新版mysql数据库亲测有效

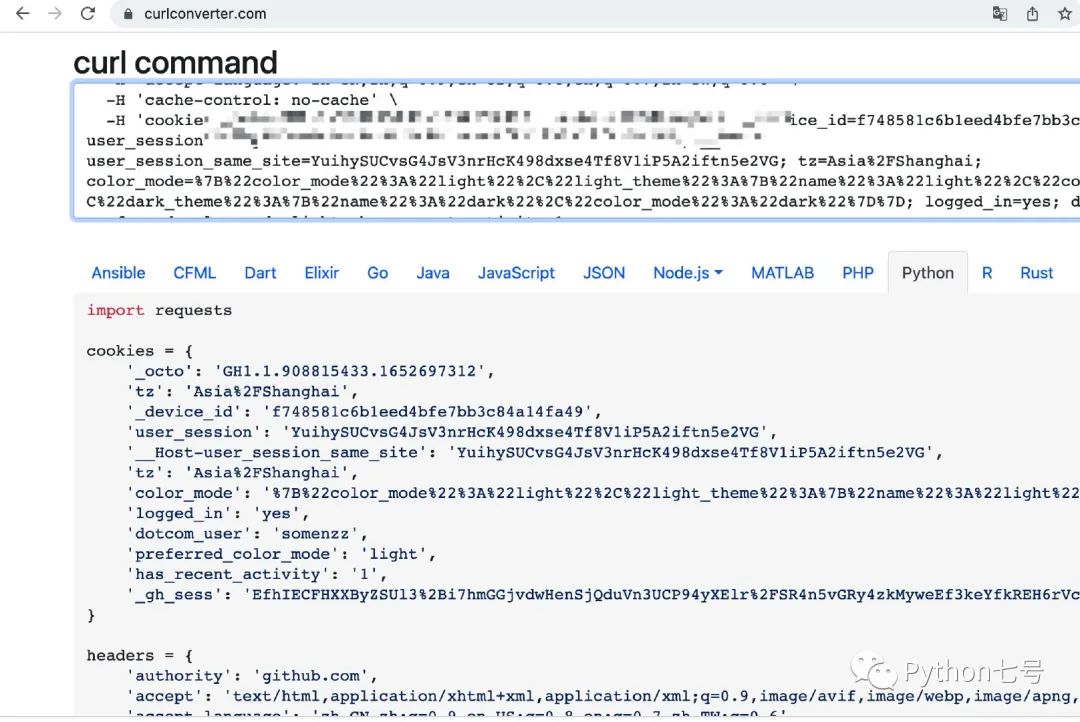

A gadget can write crawlers faster

随机推荐

MMR重排(相似度通过编辑距离和重复度计算)

7-2 芬兰木棋 结构体排序

MySQL installation steps - installing MySQL on Linux (3)

Open62541 import nodeset file directly

DOM parsing of XML file case code sentence by sentence analysis

2021 programming language ranking summary

Using interceptor and cache to complete interface anti brushing operation

In idea, the get and set methods may be popular because the Lombok plug-in is not installed

剑指offer II 091.粉刷房子

Real time database - Notes

ACM notes

HTTP Caching Protocol practice

一个小工具可以更快的写爬虫

NDK cross compilation

The practice of traffic and data isolation in vivo Reviews

LeetCode+ 51 - 55 回溯、动态规划专题

R language ggmap

PLC -- 笔记

XML序列化向后兼容

QT -- communication protocol