当前位置:网站首页>NLog使用

NLog使用

2022-07-02 03:27:00 【天天代码码天天】

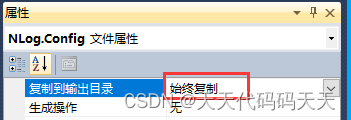

NLog.Config

<?xml version="1.0" encoding="utf-8" ?>

<nlog xmlns="http://www.nlog-project.org/schemas/NLog.xsd"

xmlns:xsi="http://www.w3.org/2001/XMLSchema-instance"

xsi:schemaLocation="http://www.nlog-project.org/schemas/NLog.xsd NLog.xsd"

autoReload="true"

throwExceptions="false"

internalLogLevel="Off"

internalLogFile="d:\nlog\nlog-internal.log">

<!-- optional, add some variables

https://github.com/nlog/NLog/wiki/Configuration-file#variables

-->

<!--<variable name="myvar" value="myvalue"/>-->

<variable name="logDir" value="${basedir}/nlog"/>

<variable name="logFileName" value="${date:format=yyyyMMdd}.txt"/>

<variable name="logArchiveFileName" value="${date:format=yyyyMMdd}_{#}.txt"/>

<variable name="logLayout" value="Logger:${logger}${newline}Date:${longdate}${newline}Level:${uppercase:${level}}${newline}Message:${message} ${newline}${onexception:Exception:${exception:format=toString}${newline}}" />

<!--

See https://github.com/nlog/nlog/wiki/Configuration-file

for information on customizing logging rules and outputs.

-->

<targets>

<!--

add your targets here

See https://github.com/nlog/NLog/wiki/Targets for possible targets.

See https://github.com/nlog/NLog/wiki/Layout-Renderers for the possible layout renderers.

-->

<!--

Write events to a file with the date in the filename.

<target xsi:type="File" name="f" fileName="${basedir}/logs/${shortdate}.log"

layout="${longdate} ${uppercase:${level}} ${message}" />

-->

<target xsi:type="File" name="info"

layout="${logLayout}"

fileName="${logDir}/info/${logFileName}"

archiveFileName="${logDir}/info/${logArchiveFileName}"

archiveAboveSize="10485760"

archiveNumbering="Sequence"

maxArchiveFiles="100"

concurrentWrites="true"

keepFileOpen="true"

openFileCacheTimeout="30"

encoding="UTF-8" />

<target xsi:type="File" name="debug"

layout="${logLayout}"

fileName="${logDir}/debug/${logFileName}"

archiveFileName="${logDir}/debug/${logArchiveFileName}"

archiveAboveSize="10485760"

archiveNumbering="Sequence"

maxArchiveFiles="100"

concurrentWrites="true"

keepFileOpen="true"

openFileCacheTimeout="30"

encoding="UTF-8" />

<target xsi:type="File" name="error"

layout="${logLayout}"

fileName="${logDir}/error/${logFileName}"

archiveFileName="${logDir}/error/${logArchiveFileName}"

archiveAboveSize="10485760"

archiveNumbering="Sequence"

maxArchiveFiles="100"

concurrentWrites="true"

keepFileOpen="true"

openFileCacheTimeout="30"

encoding="UTF-8" />

</targets>

<rules>

<!-- add your logging rules here -->

<!--

Write all events with minimal level of Debug (So Debug, Info, Warn, Error and Fatal, but not Trace) to "f"

<logger name="*" minlevel="Debug" writeTo="f" />

-->

<logger name="*" minlevel="Info" maxlevel="Info" writeTo="info" />

<logger name="*" minlevel="Debug" maxlevel="Debug" writeTo="debug" />

<logger name="*" minlevel="Error" maxlevel="Error" writeTo="error" />

</rules>

</nlog>不要忘记

测试代码

using System;

using System.Collections.Generic;

using System.ComponentModel;

using System.Data;

using System.Drawing;

using System.Linq;

using System.Text;

using System.Windows.Forms;

using NLog;

namespace NlogTest

{

public partial class Form1 : Form

{

public Form1()

{

InitializeComponent();

}

private Logger _log = NLog.LogManager.GetCurrentClassLogger();

private void button1_Click(object sender, EventArgs e)

{

_log.Info("信息");

_log.Error("异常");

int a = 0;

int b = 0;

try

{

int c = a / b;

}

catch (Exception ex)

{

_log.Error(ex,"操作异常");

}

}

}

}

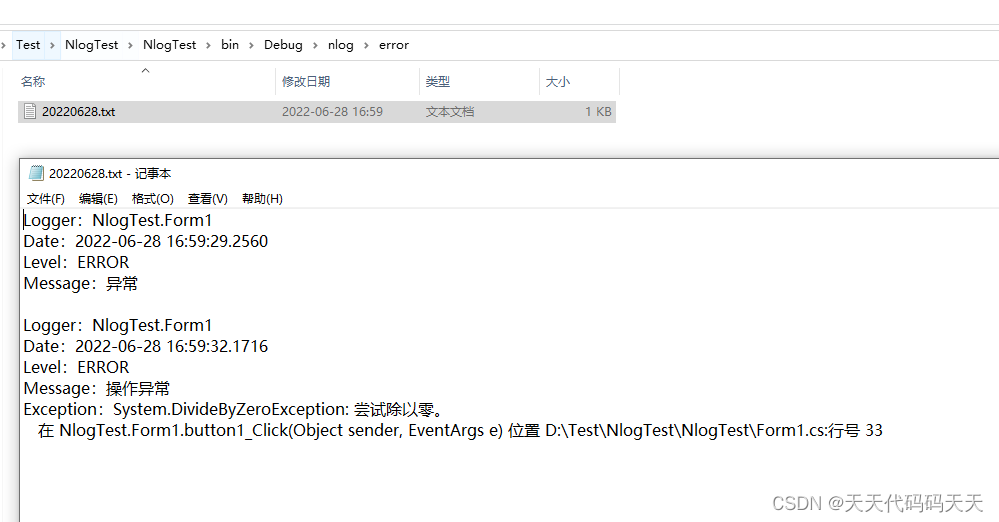

效果

边栏推荐

- JS introduction < 1 >

- Global and Chinese market of bone adhesives 2022-2028: Research Report on technology, participants, trends, market size and share

- Continuous assignment of Verilog procedure

- Verilog 线型wire 种类

- Verilog 时序控制

- Verilog state machine

- Pointer array & array pointer

- In the era of programmers' introspection, five-year-old programmers are afraid to go out for interviews

- 数据库文件逻辑结构形式指的是什么

- Kotlin基础学习 14

猜你喜欢

C shallow copy and deep copy

QT environment generates dump to solve abnormal crash

【DesignMode】原型模式(prototype pattern)

Retrofit's callback hell is really vulnerable in kotlin synergy mode

Which of PMP and software has the highest gold content?

Form custom verification rules

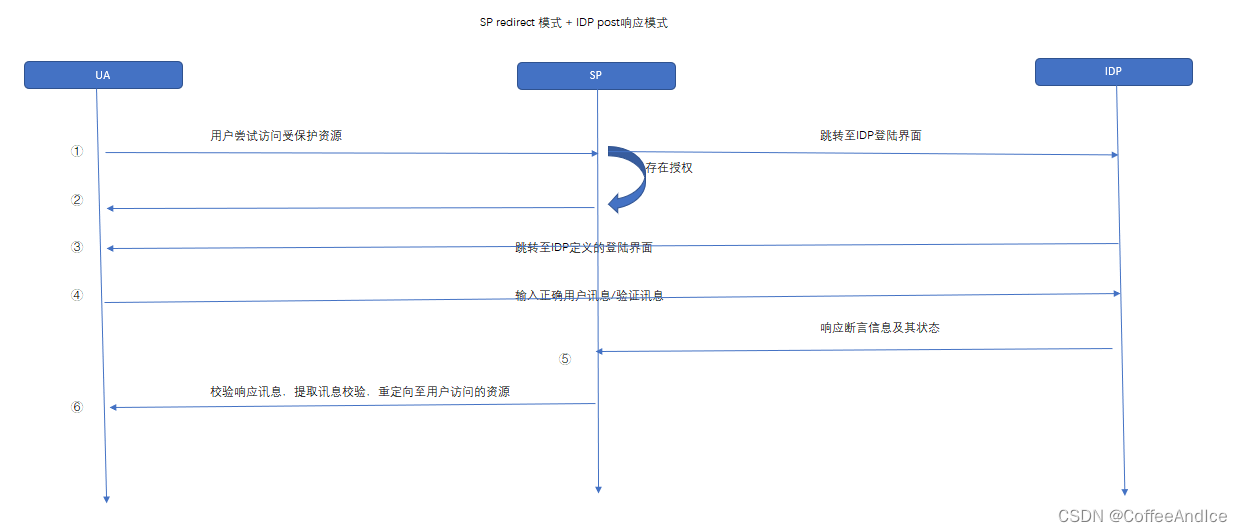

SAML2.0 笔记(一)

表单自定义校验规则

Pycharm2021 delete the package warehouse list you added

《MATLAB 神經網絡43個案例分析》:第42章 並行運算與神經網絡——基於CPU/GPU的並行神經網絡運算

随机推荐

Generate random numbers that obey normal distribution

Docker安装canal、mysql进行简单测试与实现redis和mysql缓存一致性

[数据库]JDBC

Download and use of the super perfect screenshot tool snipaste

Detailed explanation of the difference between Verilog process assignment

uniapp 使用canvas 生成海报并保存到本地

终日乾乾,夕惕若厉

在QML中加载不同字体

Verilog 状态机

C # joint halcon out of halcon Environment and various Error Reporting and Resolution Experiences

UI (New ui:: MainWindow) troubleshooting

Verilog 过程连续赋值

Unity脚本的基础语法(6)-特定文件夹

[JS reverse series] analysis of a customs publicity platform

KL divergence is a valuable article

What is the binding path of SAP ui5

Large screen visualization from bronze to the advanced king, you only need a "component reuse"!

Qualcomm platform WiFi -- Native crash caused by WiFi

PHP array processing

ThreadLocal详解

https://download.csdn.net/download/lw112190/85812952

https://download.csdn.net/download/lw112190/85812952