当前位置:网站首页>Named block Verilog

Named block Verilog

2022-07-02 03:08:00 【Da Xi】

Named blocks

We can name the block statement structure .

Local variables can be declared in named blocks , Access variables through the method of hierarchical name reference .

The simulation code is as follows :

example

`timescale 1ns/1ns

module test;

initial begin: runoob // Name the module as runoob, You can't have less semicolons

integer i ; // This variable can be passed through test.runoob.i Used by other modules

i = 0 ;

forever begin

#10 i = i + 10 ;

end

end

reg stop_flag ;

initial stop_flag = 1'b0 ;

always begin : detect_stop

if ( test.runoob.i == 100) begin //i Add up 10 Time , namely 100ns Stop simulation when

$display("Now you can stop the simulation!!!");

stop_flag = 1'b1 ;

end

#10 ;

end

endmodule

The simulation results are as follows :

Named blocks can also be disabled , With keywords disable To express .

disable The execution of named blocks can be terminated , Can be used to exit from the loop 、 Handling errors, etc .

And C In language break similar , however break You can only exit the current cycle , and disable You can disable any named block in the design .

The simulation code is as follows :

example

`timescale 1ns/1ns

module test;

initial begin: runoob_d // Name the module as runoob_d

integer i_d ;

i_d = 0 ;

while(i_d<=100) begin: runoob_d2

# 10 ;

if (i_d >= 50) begin // Add up 5 Stop accumulation for times

disable runoob_d3.clk_gen ;//stop external block: clk_gen

disable runoob_d2 ; //stop At present block: runoob_d2

end

i_d = i_d + 10 ;

end

end

reg clk ;

initial begin: runoob_d3

while (1) begin: clk_gen // Clock generation module

clk=1 ; #10 ;

clk=0 ; #10 ;

end

end

endmodule

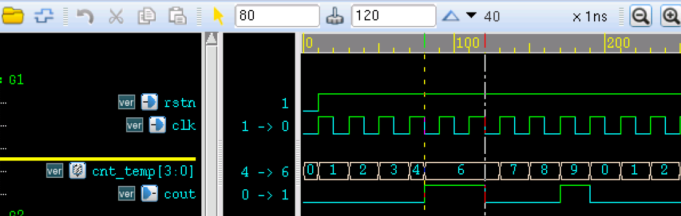

The simulation results are as follows :

It can be seen from the picture that , The signal i_d Add up to 50 in the future , No longer accumulate , in the future clk The clock is no longer produced .

so ,disable Exited the current while block .

It should be noted that ,disable stay always or forever When used in block, you can only exit the current round , The next statement will still be always or forever In the implementation of . because always Block and forever Blocks are always executed , At this time disable It's kind of similar C In language continue function .

边栏推荐

- The number one malware in January 2022: lokibot returned to the list, and emotet returned to the top

- JS <2>

- Delphi xe10.4 installing alphacontrols15.12

- Form custom verification rules

- Just a few simple steps - start playing wechat applet

- Rotating frame target detection mmrotate v0.3.1 learning model

- [staff] diacritical mark (ascending sign | descending sign B | double ascending sign x | double descending sign BB)

- Stdref and stdcref

- 命名块 verilog

- Tupu software has passed CMMI5 certification| High authority and high-level certification in the international software field

猜你喜欢

What kind of good and cost-effective Bluetooth sports headset to buy

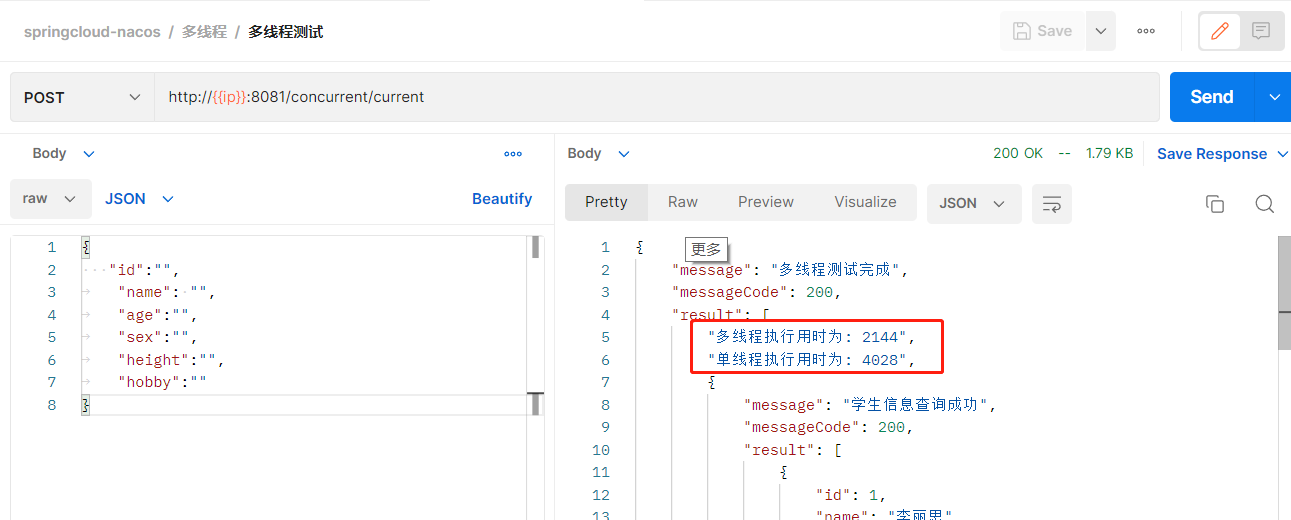

Multi threaded query, double efficiency

PHP notes - use Smarty to set public pages (include, if, else, variable settings)

QT environment generates dump to solve abnormal crash

Pychart creates new projects & loads faster & fonts larger & changes appearance

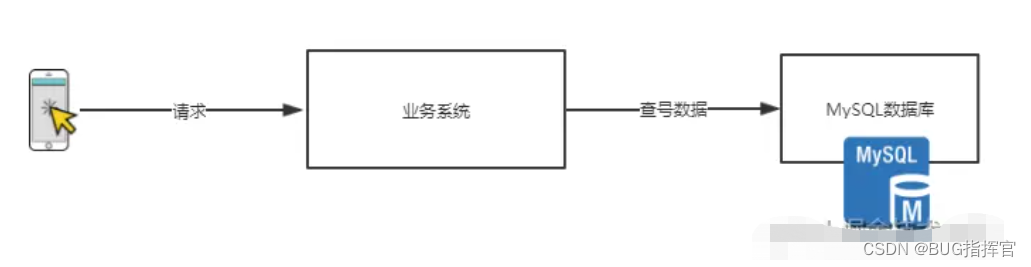

高并发场景下缓存处理方案

MongoDB非關系型數據庫

Discussion on related configuration of thread pool

JS introduction < 1 >

Verilog 过程连续赋值

随机推荐

el-table的render-header用法

Gradle notes

Websocket + spingboot realize code scanning login

A list of job levels and salaries in common Internet companies. Those who have conditions must enter big factories. The salary is really high

Remote connection to MySQL under windows and Linux system

Tupu software has passed CMMI5 certification| High authority and high-level certification in the international software field

3048. Number of words

Docker安装canal、mysql进行简单测试与实现redis和mysql缓存一致性

Principle of computer composition - interview questions for postgraduate entrance examination (review outline, key points and reference)

4. Find the median of two positive arrays

New programmer magazine | Li Penghui talks about open source cloud native message flow system

SAML2.0 笔记(一)

跟着CTF-wiki学pwn——ret2shellcode

Baohong industry | 6 financial management models at different stages of life

ZABBIX API creates hosts in batches according to the host information in Excel files

Use the open source project [banner] to achieve the effect of rotating pictures (with dots)

Is bone conduction earphone better than traditional earphones? The sound production principle of bone conduction earphones is popular science

[question 008: what is UV in unity?]

Competition and adventure burr

QT uses sqllite