当前位置:网站首页>How high does UART baud rate require for clock accuracy?

How high does UART baud rate require for clock accuracy?

2022-06-25 17:22:00 【Tianwaifeixian CUG】

A serial port communication (UART) It is an asynchronous communication , Both the sender and the receiver need to communicate according to the agreed baud rate . When baud rate error occurs , It will cause communication error . What are the factors that cause baud rate error , Today, let's analyze .

1. Frequency division error

First , The baud rate is generated according to the frequency division of the system clock , The relationship between the system clock and baud rate may not be an integer multiple , Therefore, there will be errors in frequency division . But now most of them MCU The system clock of is relatively high , Usually in the tens of MHz, Far greater than the baud rate of serial communication , So the effect of this error is very small . hypothesis MCU The clock is 48MHz, The baud rate is 115200,48MHz/115200=416.67, according to 417 frequency division , The actual baud rate is 48M/417=115108, Error is (115200-115108)/115200, about 0.08%, This error is very small , No effect on serial communication .

however , When the system clock is low , Or when the baud rate is high , That is, the difference ratio between the two is small , This error cannot be ignored .

For some earlier 51 Kernel MCU, Due to low operating frequency , Non integer crystal oscillator ( such as 11.0592M etc. ) To use the common baud rate ( such as 9600、115200), The error of frequency division shall be as small as possible .

2. Clock error

secondly , The main error of baud rate depends on the error of system clock . How high is the requirement for clock error in serial communication ?

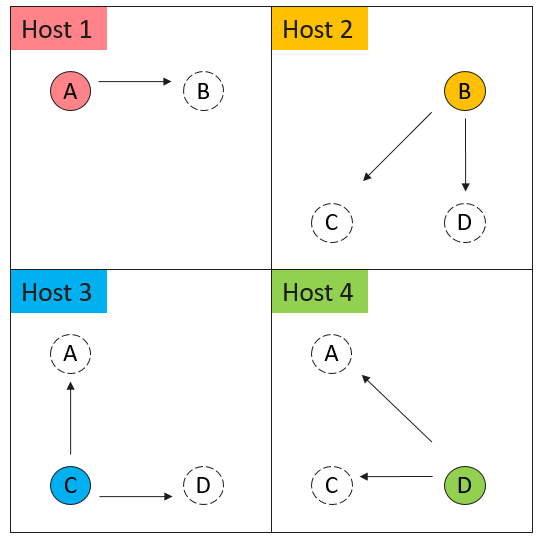

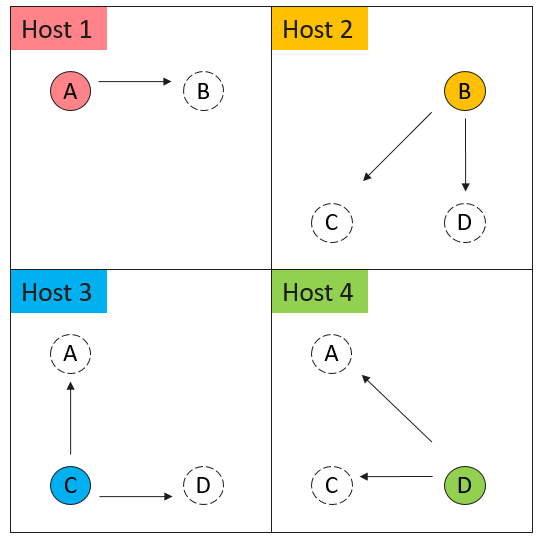

First look at the serial port communication sequence diagram :

The serial port communication consists of the starting bit 、 Data bits 、 Check bit 、 Stop bit composition . With the common 8N1 For example , namely 1 Bit start bit ,8 Digit bit , No verification ,1 Bit stop bit . That is to say, transferring a byte requires 10bits. Each byte has a start bit for synchronization , So the error will only accumulate in one byte .

It's not hard to see. , At the last bit sampling , Maximum error , The allowable limit error is 0.5 position . Per byte 10 Bit calculation , The maximum allowable error is ±0.5/10=±0.05, namely ±5%. Considering that the serial communication involves both ends of the transceiver , There may be errors at both ends , therefore , The error at each end should be controlled within ±2.5% within .

When data bit 、 When there are many parity bits, etc , The required clock error is higher . Considering the above-mentioned frequency division error , Generally speaking , The clock error is less than ±2% when , Serial communication is reliable .

Recommended reading :

adopt STM32 Built in USB-DFU Download program

Several orders USB The scheme of converting to multiple serial ports

How to measure the running time of single chip microcomputer program ?

Several common methods of generating negative power supply

Welcome to the official account " Development of Embedded Technology ", You can leave a message for me backstage . If you think the official account is helpful to you , Also welcome to recommend and share with others .

边栏推荐

- LSF如何看job预留slot是否合理?

- On Web 3.0

- Uncover ges super large scale graph computing engine hyg: Graph Segmentation

- js禁止浏览器默认事件

- try with resource

- Ten thousand volumes - list of Dali wa

- 效应与定律

- Kalman filter meets deep learning: papers on Kalman filter and deep learning

- FreeRTOS内核时钟不对的问题解决

- How to talk about salary correctly in software testing interview

猜你喜欢

六大专题全方位优化,阿里巴巴性能优化小册终开源,带你直抵性能极致

2022-06-17 advanced network engineering (IX) is-is- principle, NSAP, net, area division, network type, and overhead value

Kotlin

SnakeYAML配置文件解析器

Uncover ges super large scale graph computing engine hyg: Graph Segmentation

Vscode plug-in self use

揭秘GES超大规模图计算引擎HyG:图切分

CVPR小目标检测:上下文和注意力机制提升小目标检测(附论文下载)

ddia数据密集型应用系统设计 整理

【编译原理】概述

随机推荐

ddia数据密集型应用系统设计 整理

数学建模——非线性规划

数学建模——整数规划

这些老系统代码,是猪写的么?

Mobx学习之路----强大的“状态管理工具”

SMART PLC如何构造ALT指令

2021年5月云南省网络空间安全比赛赛题复盘

Do you know all the configurations of pychrm?

WPF development essays Collection - ECG curve drawing

Uncover ges super large scale graph computing engine hyg: Graph Segmentation

数学建模——线性规划

二十九-使用RealSenseD435进行ORBSLAM2实时三维重建

N皇后问题

Kalman filter meets deep learning: papers on Kalman filter and deep learning

How smart PLC constructs ALT instruction

FreeRTOS内核时钟不对的问题解决

效应与定律

Learning Tai Chi makers - mqtt (I) what is mqtt

远程终端控制神器——MobaXterm

The role of the project manager in the project