当前位置:网站首页>Digital IC code -- traffic lights

Digital IC code -- traffic lights

2022-06-29 14:42:00 【FPGA silicon agriculture】

subject

describe

A traffic light is required , It has three small red, yellow and green indicators and a pedestrian button , Under normal circumstances , The motorway indicator light shall be in accordance with 60 Clock cycle green ,5 A clock cycle yellow light ,10 A clock cycle, a red light cycle . When the pedestrian button is pressed , If the remaining green time is greater than 10 A clock , Is shortened to 10 A clock , Less than 10 The two clocks remain the same .

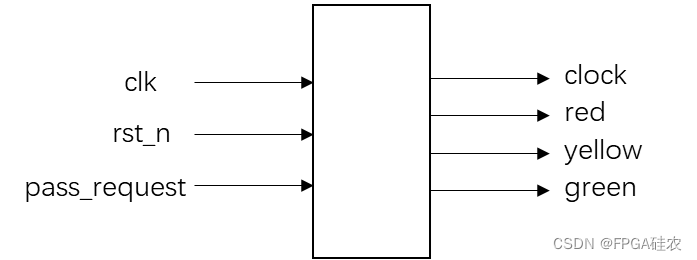

The signal interface diagram of the module is as follows :

Please use VerilogHDL Language implementation , And write testbench Verification function .

Code

Design

`timescale 1ns/1ns

module triffic_light

(

input rst_n, // Ectopic reset signal , Low level active

input clk, // Clock signal

input pass_request,

output reg [7:0]clock,

output reg red,

output reg yellow,

output reg green

);

parameter RED=0;

parameter GREEN=1;

parameter YELLOW=2;

reg [1:0] state,next_state;

//60 clk green

//5 clk yellow

//10 clk red

[email protected](posedge clk,negedge rst_n)

if(~rst_n)

state<=RED;

else

state<=next_state;

[email protected](*)

begin

case(state)

RED:if(clock==1)

next_state=GREEN;

else

next_state=RED;

YELLOW:if(clock==1)

next_state=RED;

else

next_state=YELLOW;

GREEN:if(clock==1)

next_state=YELLOW;

else

next_state=GREEN;

default:next_state=RED;

endcase

end

//led

[email protected](*)

case(state)

RED:{

red,yellow,green}=3'b100;

YELLOW:{

red,yellow,green}=3'b010;

GREEN:{

red,yellow,green}=3'b001;

default:{

red,yellow,green}=3'b000;

endcase

//clock

[email protected](posedge clk,negedge rst_n)

if(~rst_n)

clock<=10; //red

else

case(state)

RED:if(clock==1)

clock<=60;

else

clock<=clock-1;

YELLOW:if(clock==1)

clock<=10;

else

clock<=clock-1;

GREEN:

if(pass_request)

if(clock>10)

clock<=10;

else

clock<=clock-1;

else if(clock==1)

clock<=5;

else

clock<=clock-1;

default:clock<=10;

endcase

endmodule

Test platform

module test;

reg clk;

reg rst_n;

reg pass_request;

wire [7:0] clock;

wire red;

wire yellow;

wire green;

//clk

initial

begin

clk=0;

forever

#5 clk=~clk;

end

//rst_n

initial

begin

rst_n=0;

#100

rst_n=1;

end

//

initial

begin

pass_request=0;

//

repeat(20)

@(posedge clk);

wait(green&&clock==18);

pass_request<=1;

@(posedge clk);

pass_request<=0;

//

repeat(40)

@(posedge clk);

wait(green&&clock==9);

pass_request<=1;

@(posedge clk)

pass_request<=0;

end

//inst

triffic_light U

(.*

/* input rst_n, // Ectopic reset signal , Low level active input clk, // Clock signal input pass_request, output reg [7:0]clock, output reg red, output reg yellow, output reg green */

);

endmodule

result

Under normal circumstances , A green light 60 A cycle , Yellow light 5 A cycle , A red light 10 A cycle

Green and greater than 10 A cycle , Pedestrian press

Green light and less than or equal to 10 A cycle , Pedestrian press

边栏推荐

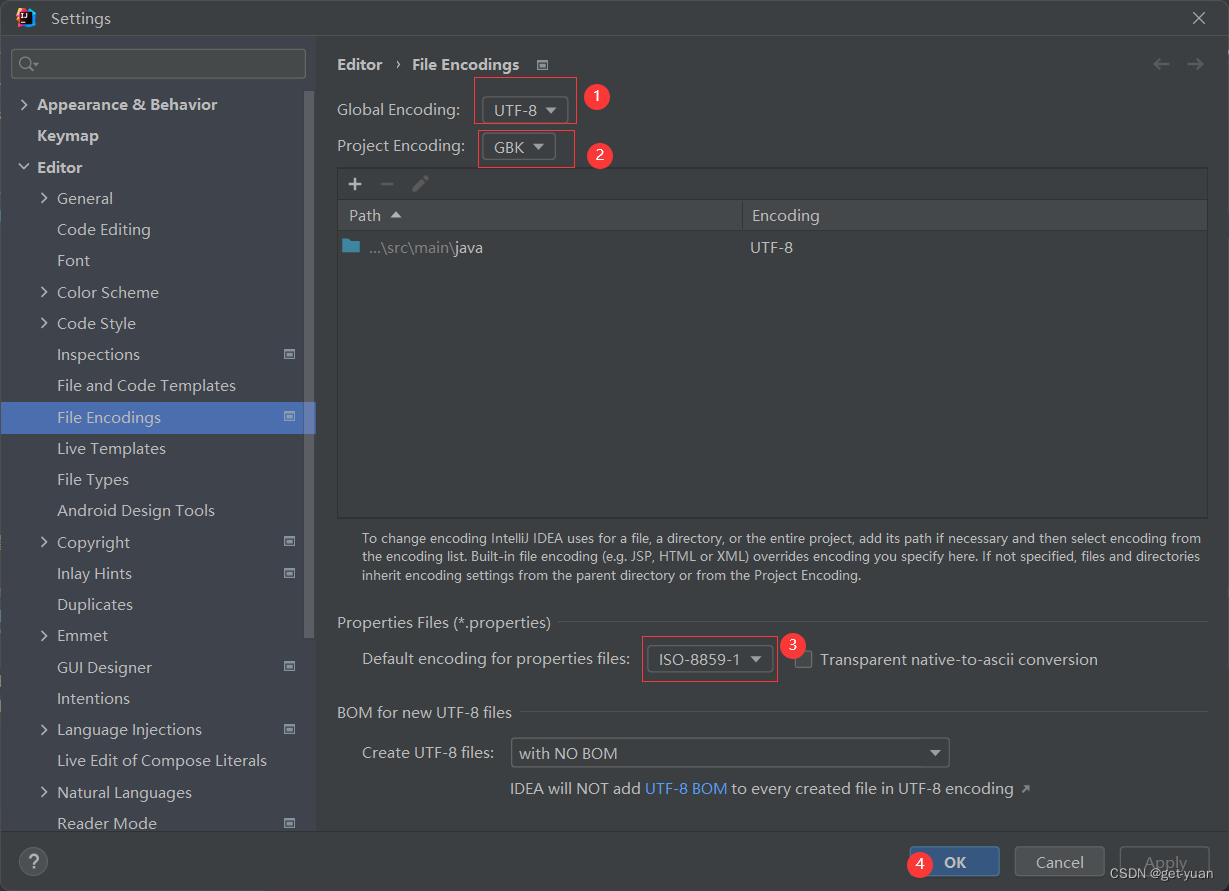

- idea输出台输出中文乱码问题

- Which is better and safer for Dongguan Humen securities company to open a stock account?

- matplotlib直方图,柱状图

- 每周 Postgres 世界动态 2022w25

- Analysis of istio -- observability

- Wechat applet: install B artifact and P diagram, modify wechat traffic main applet source code, Download funny joke diagram, make server free domain name

- 《canvas》之第13章 事件操作

- 精品商城拼团秒杀优惠折扣全功能完美双端自适应对接个人免签网站源码

- Redis fragment cluster setup and use tutorial

- [QT tutorial] QPushButton key and double click effect

猜你喜欢

广州开展瓶装气安全宣传活动,普及燃气安全知识

【置顶】博客使用须知,公告板,留言板,关于博主

云上第一课 | 建个小破站有多简单?云计算老司机带你一小时搞定

Wechat applet: install B artifact and P diagram, modify wechat traffic main applet source code, Download funny joke diagram, make server free domain name

部署搭建decentraland流程讲解

idea输出台输出中文乱码问题

第五届中国软件开源创新大赛 | openGauss赛道直播培训

Are you still reading the log by command? Use kibana, one picture is better than ten thousand lines of log

Campus errands wechat applet errands students with live new source code

Uncover the secret! Pay attention to those machines under the membership system!

随机推荐

揭秘!付费会员制下的那些小心机!

云上第一课 | 建个小破站有多简单?云计算老司机带你一小时搞定

国内十大券商,有哪些安全吗?

【Try to Hack】vulnhub DC2

delphi7中 url的编码

MySQL数据库:drop、truncate、delete的区别

吐血整理:一份不可多得的架构师图谱!

类模板案例-【数组类封装】

浅析 Istio——可观测性

每周 Postgres 世界动态 2022w25

Swagger2的配置教程

openGauss社区成立SIG KnowledgeGraph

go-zero微服务实战系列(七、请求量这么高该如何优化)

Redis的事务机制

《canvas》之第12章 其他应用

URL encoding in Delphi7

传输层 用户数据报协议(UDP)

建立自己的网站(19)

仿头条新闻资讯dz模板 Discuz新闻资讯商业版GBK模板源码

一位博士在华为的22年