当前位置:网站首页>Embedded virlog code running process

Embedded virlog code running process

2022-06-26 13:36:00 【Dressing】

be based on vivado Of virlog Operation process (Nexys A7 Development board )

The embedded virlog Code flow

One 、 New project

The chip used is Artix chip ,Nexys A7 Development board .

1. Set the project name and storage path

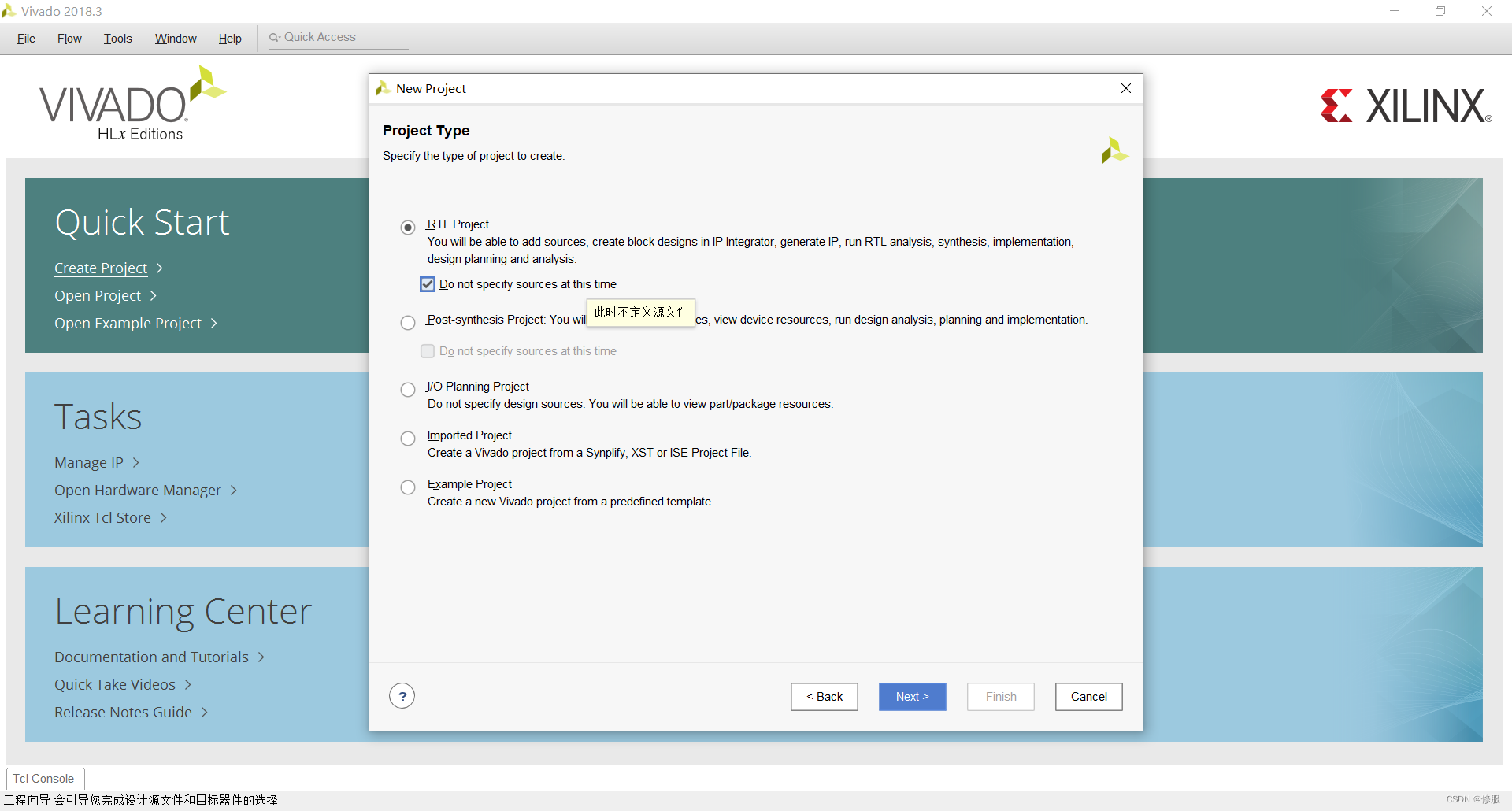

2. In general use RTL type , If there is no file you want to add , You can check

The box options below

3. Here you can use the drop-down box to add chip search options , Select as needed

4.finish

Two 、 Design input and synthesis

The code structure is :

design: Design documents

constraints: Constraint file

Simuation: Simulation file

1. Input design

increase design Code

The code is as follows :

module add(a,b,c,y);

input a,b,c;

output y;

assign y=~(a&b&c);

endmodule

2. To synthesize

3、 ... and 、 Conduct simulation

add to Simulation Code

The code is as follows ( Example ):

module add_sim( );

parameter N=3;// Is a few variable inputs ,n Just a few

reg clk=0;

reg [N-1:0] cnt;

wire a,b,c;

wire y;// Input / output port

always #10 clk=~clk;

[email protected](posedge clk)

begin

cnt=cnt+1'b1;

end

// On the rising edge cnt+1=cnt

initial

begin

cnt=3'b0;//3 Representation bit ,0 Represents the value ,b For binary

end

assign {

a,b,c}=cnt;//cnt to a,b,c Full scale change , Splicing operator

add utest(a,b,c,y);

endmodule

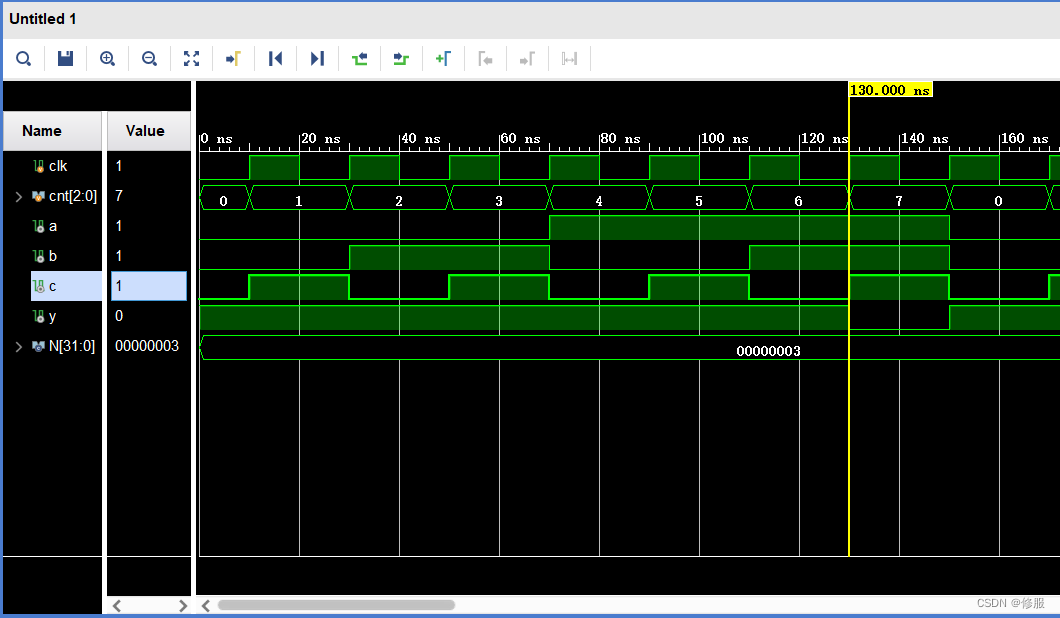

Simulation :

Behavior simulation

Functional simulation

Time series simulation

Different simulations will have different waveform effects

Four 、 Constraint

First understand the pin resources of the board

1. Configure resources in constraint Wizard mode

2.IO planning Mode configuration pin , Here I use IO Mode configuration

Find the pin name corresponding to the resource in the board resource , stay ports Set in ,IO std If it turns red, choose other black types

here J15,L16,M13 Corresponding dial switch ;H17 Corresponding LED

Save constraint file

5、 ... and 、 Implementation and download

Perform synthesis to generate bitstream

After the previous run ,BitStream It turns green , Click it to generate a bitmap file

Open the board here , After the successful opening, the program The choice of , Click and then click the... That appears program You can run on the board

边栏推荐

- Mediapipe gestures (hands)

- 12 SQL optimization schemes summarized by old drivers (very practical)

- GO语言-管道channel

- What features are added to Photoshop 2022 23.4.1? Do you know anything

- Stack, LIFO

- Coprime and non coprime of template problems of Chinese remainder theorem

- Use of wangeditor rich text editor

- 李航老师新作《机器学习方法》上市了!附购买链接

- Electron official docs series: Examples

- Basic methods for network diagnosis and hardware troubleshooting of Beifu EtherCAT module

猜你喜欢

Beifu realizes the control of time slice size and quantity through CTU and ton

Ring queue PHP

Thinking caused by the error < note: candidate expectations 1 argument, 0 provided >

MongoDB系列之Window环境部署配置

去某东面试遇到并发编程问题:如何安全地中断一个正在运行的线程

Beifu PLC model selection -- how to see whether the motor is a multi turn absolute value encoder or a single turn absolute value encoder

Log in to the server using SSH key pair

Here document interaction free and expect automatic interaction

2. Introduction to parallel interface, protocol and related chips (8080, 8060)

![[MySQL from introduction to mastery] [advanced part] (II) representation of MySQL directory structure and tables in the file system](/img/03/a1885e4740bbfdbdee2446e3dd81d0.png)

[MySQL from introduction to mastery] [advanced part] (II) representation of MySQL directory structure and tables in the file system

随机推荐

HDU 5860

Electron official docs series: Distribution

Arcpy——InsertLayer()函数的使用:掺入图层到地图文档里

Es6: iterator

Mysql database explanation (6)

Beifu PLC model selection -- how to see whether the motor is a multi turn absolute value encoder or a single turn absolute value encoder

Input text to automatically generate images. It's fun!

嵌入式virlog代码运行流程

sed编辑器

[how to connect the network] Chapter 1: the browser generates messages

ES基于Snapshot(快照)的数据备份和还原

Bigint: handles large numbers (integers of any length)

There are many contents in the widget, so it is a good scheme to support scrolling

Some conclusions about Nan

MongoDB系列之Window环境部署配置

8、【STM32】定时器(TIM)——中断、PWM、输入捕获实验(一文精通定时器)

Fire warning is completed within 10 seconds, and Baidu AI Cloud helps Kunming Guandu build a new benchmark of smart city

HDU 3709 Balanced Number

Decorator

Beifu cx5130 card replacement and transfer of existing authorization files