当前位置:网站首页>Static timing analysis OCV and time derive

Static timing analysis OCV and time derive

2022-06-27 03:34:00 【Luca cat】

List of articles

Basic concepts

OCV(on-chip variation) On the same chip , Due to the manufacturing process and environment, the characteristics of each part on the chip cannot be exactly the same , So as to cause deviation , Impact on time series analysis . These deviations affect the interconnection and cell The time delay of the is affected . because OCV The impact on the clock and data path may be different , Timing verification can be achieved by making the transmission and acquisition paths PVT The conditions are slightly different to simulate OCV effect . STA Can pass ** Derating (derate)** The delay of a particular path to include OCV effect , in other words , By making these paths faster or slower , Then use these changes to verify the design behavior . Unit delay or line delay or both can be derated to simulate OCV Influence .

time derate( Timing increase / decrease factor ), In the process of chip production , Due to etching , Temperature at different points , Uneven metal , crosstalk , Transistor channel length and other factors , As a result, the delay of each position unit on the chip is different . So we need a scaling factor to make the design more rigorous .

timing derate It's calculation OCV A simple way to , Under a single condition (BC-WC) Next , Designate path Of delay Zoom in or out , This ratio is derate.

best-case worse-case abbreviation BCWC mode. It should be noted that : consider time derate Need to be under a single condition , for instance BC perhaps WC Under the condition of , Designate path Increase or decrease the delay of , Or BC, Or WC, Don't put the BC and WC Mixed in with , Again OCV, That's too pessimistic .

Analysis mode

The static timing analysis tool provides 3 The two analysis modes are :

- single_mode

- BC-WC

- OCV mode(AOCV, POCV)

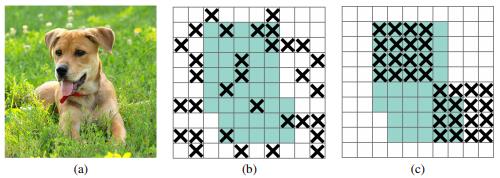

Here's the picture ,BC-WC In mode ,setup check All the inspections are worst-case Lower computation , and hold check All the inspections are best-case Lower computation

Here's the picture ,OCV In mode ,setup/hold check The inspection of is in worst-case/hold check Crossing under , See the following introduction for the specific analysis process .

How to choose path?

about setup Analysis:

- Launch lock : late path

- Data path : late path

- Capture clock : early path

about hold Analysis:

- Launch lock : early path

- Data path : early path

- Capture clock : late path

Establish time OCV analysis

Data arrival time namely data path and launch clock path Need to use -late Options , Make the path slower

Data requires time namely capture clock path Need to use -early Options , Speed up path latency

setup check commonly Working in WC PVT Under the condition of , So there's no need to be in late path On , namely lauch clock path as well as data path Plus time derate, Because in WC Under the condition of ,launch clock path as well as data path The delay on is already the worst under all conditions delay 了 , There is no need to increase the delay , however WC Under the condition of capture clock path Upper delay Certainly not the smallest , So we need to speed up .

So the top timing path do setup check,time derate Just set it like this :

set_timing_derate -early 0.9

set_timing_derate -late 1.0

For different processes ,derate The value is generally summarized from the actual engineering experience

launch clock path = (1.2+0.8)*1.0 = 2.0

max data path = 5.2 * 1.0 =5.2

capture clock path = (1.2 + 0.86) *0.9 = 1.854

So the minimum clock period T = 2.0 + 5.2 -1.854 + 0.385= 5.731

It can be seen that timing derate in the future , Will reduce the overall design Working frequency of

Keep time to check OCV

If on the chip PVT Different conditions , Then, when the initiating clock path and the data path have the OCV Conditions ( That is, the earliest initiating clock ), And the holding clock path has the function of causing the maximum delay OCV Conditions ( The latest capture clock ) when , The worst case of keeping time check will happen .

Data arrival time namely data path and launch clock path Need to use -early Options , Make the path faster

Data requires time namely capture clock path Need to use -late Options , Make the path slower

actually Hold check Generally in BC Under the condition of , therefore ,launch clock path And data path No further reduction is required delay, Because it is already the smallest delay, however BC Under the condition of capture clock path need derate, You can use the following settings

set_timing_derate -early 1.0

set_timing_derate -late 1.2

Launch clock path = 0.85 * 1.0 = 0.85

Min data path = 1.7 * 1.0 = 1.7

Capture clock path = 1.0 * 1.2 = 1.2

slack=0.85+1.7-1.2-1.25=0.1

边栏推荐

- 通信中的机器学习最佳阅读资料列表

- 2021:Greedy Gradient Ensemble for Robust Visual Question Answering

- Basic functions of promise [IV. promise source code]

- JMeter distributed pressure measurement

- PAT甲级 1023 Have Fun with Numbers

- Implementation of window encryption shell

- lodash get js代码实现

- Super détaillé, 20 000 caractères détaillés, mangez à travers es!

- TP5 spreadsheet excel table export

- Questions and answers of chlor alkali electrolysis process in 2022

猜你喜欢

GAMES101作业7提高-微表面材质的实现过程

元透实盘周记20220627

文旅灯光秀打破时空限制,展现景区夜游魅力

Ledrui ldr6035 usb-c interface device supports rechargeable OTG data transmission scheme.

Cvpr2021:separating skills and concepts for new visual question answering

Pat grade a 1025 pat ranking

Flink learning 4:flink technology stack

2019LXMERT:Learning Cross-Modality Encoder Representations from Transformers

Brief introduction of 228 dropout methods of pytorch and fast implementation of dropblock with 4 lines of code based on dropout

2021:Graphhopper: Multi-Hop Scene Graph Reasoning for Visual Question Answering

随机推荐

解码苹果手机证书文件方法

2021:Graphhopper: Multi-Hop Scene Graph Reasoning for Visual Question Answering

Test the respective roles of nohup and &

苹果手机证书构体知识

733. 图像渲染

Flink learning 4:flink technology stack

Logarithm

resnet152 辣椒病虫害图像识别1.0

2022 Chinese pastry (Advanced) recurrent training question bank and online simulation test

ESP8266

Il manque beaucoup de fichiers et de répertoires tels que scripts pendant et après l'installation d'anaconda3

How can e-commerce products be promoted and advertised on Zhihu?

Yiwen teaches you Kali information collection

2021:passage retrieval for outside knowledgevisual question answering

流沙画模拟器源码

Implementation of window encryption shell

Nacos调用微服务两个问题:1.Load balancer does not contain an instance for the service 2.Connection refused

Easy to use plug-ins in idea

Learn Tai Chi Maker - mqtt (VIII) esp8266 subscribe to mqtt topic

Further exploration of handler (Part 2) (the most complete analysis of the core principles of handler)