当前位置:网站首页>Verilog语法基础HDL Bits训练 06

Verilog语法基础HDL Bits训练 06

2022-07-26 00:14:00 【南邮学渣】

这里写目录标题

Combinational Logic:Basic Gates

一、Wire

- RTL代码

module top_module (

input in,

output out);

assign out = in;

endmodule

二、GND

- RTL代码

module top_module (

output out);

assign out = 1'b0;

endmodule

三、NOR

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1 | in2);

endmodule

四、Another gate

- RTL代码

module top_module (

input in1,

input in2,

output out);

assign out = in1 & (~in2);

endmodule

五、Two gates

- RTL代码

module top_module (

input in1,

input in2,

input in3,

output out);

assign out = ~(in1 ^ in2) ^ in3;

endmodule

六、More logic gates

- RTL代码

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and = a & b;

assign out_or = a | b;

assign out_xor = a ^ b;

assign out_nand = ~(a & b);

assign out_nor = ~(a | b);

assign out_xnor = ~(a ^ b);

assign out_anotb = a & (~b);

endmodule

- 仿真波形图

七、7420 chip

- RTL代码

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ~(p1a & p1b & p1c & p1d);

assign p2y = ~(p2a & p2b & p2c & p2d);

endmodule

- 仿真波形图

八、Truh tables

本题可以硬解,即用case语句列出所有 可能,当然,本题想要考察的是根据真值表列出逻辑表达式的知识点,推荐使用卡诺图法化简

- case语句RTL代码

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

always @(*)

case({

x3,x2,x1})

3'd2,3'd3,3'd5,3'd7:

f = 1'b1;

3'd0,3'd1,3'd4,3'd6:

f=1'b0;

default: f = 1'b0;

endcase

endmodule

- 逻辑表达式RTL代码

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

assign f = ((~x3)&x2&(~x1))|((~x3)&x2&x1)|(x3&(~x2)&x1)|(x3&x2&x1);

endmodule

九、Two-bit equality

- RTL代码

module top_module ( input [1:0] A, input [1:0] B, output z );

assign z = (A == B)? 1'b1:1'b0;

endmodule

十、Simple circuit A

- RTL代码

module top_module (input x, input y, output z);

assign z = (x ^ y) & x;

endmodule

十一、Simple circuit B

- RTL代码

module top_module ( input x, input y, output z );

assign z = (x == y)? 1'b1:1'b0;

endmodule

- 仿真波形图

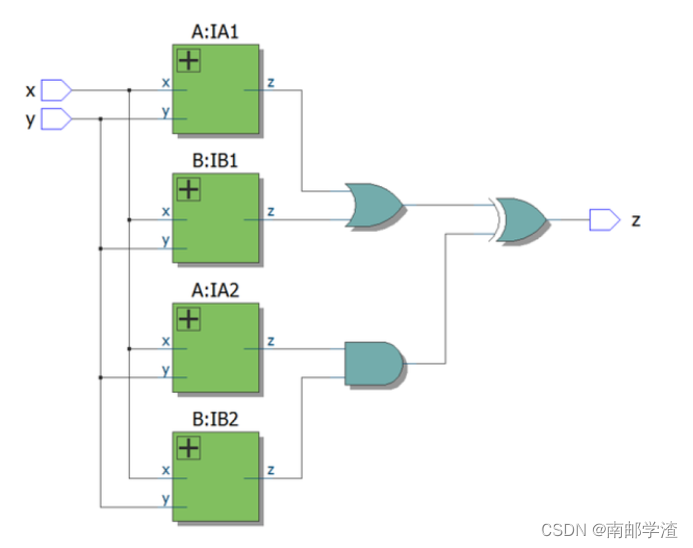

十二、Combine circuits A and B

本题需要使用前两题的语句做铺垫

- RTL代码

module top_module (input x, input y, output z);

wire z_A;

wire z_B;

assign z_A = (x ^ y) & x;

assign z_B = (x == y)? 1'b1:1'b0;

assign z = (z_A | z_B) ^ (z_A & z_B);

endmodule

十三、Ring or vibrate

看仿真波形图就可以看明白代码啦

- RTL代码

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

always @(*)

if(ring & !vibrate_mode)begin

motor = 1'b0;

ringer = 1'b1;

end

else if(vibrate_mode & ring)begin

ringer = 1'b0;

motor = 1'b1;

end

else begin

ringer = 1'b0;

motor = 1'b0;

end

endmodule

- 仿真波形图

十四、Thermostat

制作一个恒温器的控制单元

- RTL代码

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

assign heater = mode & too_cold & (!aircon);

assign aircon = (!mode) & too_hot & (!heater);

assign fan = heater | aircon | fan_on;

endmodule

- 仿真波形图

十五、3-bit population count

- RTL代码

module top_module(

input [2:0] in,

output [1:0] out );

integer i;

always @(*)begin

out = 1'b0;

for(i=0;i<3;i=i+1)

if(in[i])

out = out + 1'b1;

else

out = out;

end

endmodule

- 仿真波形图

十六、Gates and vectors

- RTL代码

module top_module(

input [3:0] in,

output [2:0] out_both,

output [3:1] out_any,

output [3:0] out_different );

integer i;

always @(*)begin

for(i=0;i<3;i=i+1)

begin

out_both[i] = in[i] & in[i+1];

out_any[3-i] = in[3-i] | in[2-i];

out_different[i] = in[i] ^ in[i+1];

end

end

assign out_different[3] = in[3] ^ in[0];

endmodule

- 仿真波形图

十七、Even longer vectors

- RTL代码

module top_module(

input [99:0] in,

output [98:0] out_both,

output [99:1] out_any,

output [99:0] out_different );

integer i;

always @(*)begin

for(i=0;i<99;i=i+1)

begin

out_both[i] = in[i] & in[i+1];

out_any[99-i] = in[99-i] | in[98-i];

out_different[i] = in[i] ^ in[i+1];

end

end

assign out_different[99] = in[99] ^ in[0];

endmodule

边栏推荐

- Use of redis

- [hero planet July training leetcode problem solving daily] 25th tree array

- 试除法--3的幂

- 【目录】mqtt、nodejs项目

- Hefei approved in advance

- 分布式事务 :可靠消息最终一致性方案

- 数据流通交易场景下数据质量综合管理体系与技术框架研究

- redis的使用

- Matlab makes the image of serial port output data in real time

- Four characteristics and isolation level of MySQL transactions

猜你喜欢

【redis】③ 数据淘汰策略、pipeline 管道命令、发布订阅

Nest. JS uses express but not completely

The bull market is not over yet, and there is still 2021-05-18 in the second half

PC website realizes wechat code scanning login function (II)

MWEC:一种基于多语义词向量的中文新词发现方法

OPENCV学习DAY6

MySQL - master-slave replication

【论文笔记】—目标姿态估计—EPro-PnP—2022-CVPR

Semaphore

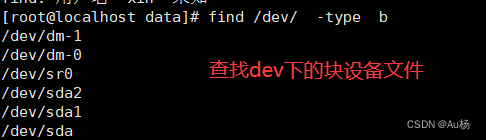

寻找命令find和locate

随机推荐

Sliding window_

Preparation of bovine serum albumin modified by low molecular weight protamine lmwp/peg-1900 on the surface of albumin nanoparticles

计算物理期刊修改

The way to understand JS: the principle of object.call and object.create() inheritance

LeetCode_ 55_ Jumping game

牛血清白蛋白修饰牛红细胞超氧化物歧化酶SOD/叶酸偶联2-ME白蛋白纳米粒的制备

这一次,彻底弄懂 Promise 原理

为了拿捏 Redis 数据结构,我画了 40 张图(完整版)

京东获取推荐商品列表 API

如何用120行代码,实现一个交互完整的拖拽上传组件?

试除法--3的幂

MySQL - database log

FreeRTOS personal notes - semaphore

Opencv learning Day6

8种MySQL常见SQL错误用法,我全中

nodejs启动mqtt服务报错SchemaError: Expected `schema` to be an object or boolean问题解决

Nodejs learning resources

Solve page refresh without attaching data

redis的使用

Semaphore