当前位置:网站首页>[in simple terms, play with FPGA learning 11 --- testbench writing skills 1]

[in simple terms, play with FPGA learning 11 --- testbench writing skills 1]

2022-07-26 01:47:00 【Ape Zhou】

Play in depth FPGA Study 11----Testbench Writing skills 1

Encapsulate useful subroutines

stay C In language , An experienced software engineer must write a subroutine for a piece of code that is often used , Then call it with different parameters . This can achieve the effect of code reuse , Reduce unnecessary repetitive labor , It also makes the code relatively simple . stay Testbench Can also be used in task Encapsulate the code , It can communicate with C The sub functions of the language are called flexibly .

The following example gives a very practical package subroutine , Maybe it can be used in the test script of every project .

// Encapsulate some useful reports for testing

// Including tasks error, warning, fatal, terminate

module print_task();

// Show warning The report , It also includes the current time and warning content ( Input by user )

task warning;

input [80*8:1] msg;

begin

$write("WARNING at %t: %s", $time,msg);

end

endtask

// Show error The report , It also includes displaying the current time and error content ( Input by user )

task error;

input [80*8:1] msg;

begin

$write("-ERROR- at %t: %s", $time, msg);

end

endtask

// Show fatal The report , It also includes the display of the current time and fatal content ( Input by user )

task fatal;

input [80*8:1] msg;

begin

$write(" *FATAL* at %t: %s", $time, msg);

terminate;

end

endtask

// Show warning The report , It also includes the current time and end information ( This task generates )

task terminate;

begin

$write("Simulation completed\n");

$ finish;

end

endtask

endmodule

When using encapsulated subroutines , As shown in the following code :

// Use print_task.v, Then you can call its encapsulated task 了

print_task print();

...

initial begin

if (...) print.error("Unexpected response\n"); // call error Mission

...

print.terminate; // call terminate Mission

end

...

endmodule

About the definition of variables

Writing Testbench when , The common mistake about the definition of variables is to apply a well-defined global variable to two different always In block ( Such as EX1C), So because of these two always Block independent and parallel working mechanism , It is likely to lead to unexpected consequences .

EX1C:

interger i;

always begin

for(i=0; i<32; i=i+1) begin

end

end

always begin

for(i=0; i<32;i=i+1) begin

...

end

end

actually , stay Verilog in ( To write Testbench when ), If in begin…end Defined between always Block name of , Then it can be as EX1C Also declare variables . These two always Variables in the block i Is irrelevant , It will not produce unpredictable results .

EX2C:

always begin

integer i;

for(i=0; i<32; i=i+1) begin

...

end

end

always

begin: block_2

integer i;

for(i=0; i<32;i=i+1) begin

...

end

end

in addition to , stay Verilog Medium function and task It also supports local variable definitions similar to the above .

HDL The parallelism of

Why? C Can't replace Verilog and VHDL As a hardware description language ? because C The most basic hardware description is missing 3 A thought : Connectivity (connectivity)、 Timeliness (Time) And parallelism (Concurrency).

Connectivity is the ability to use a simple and interconnected module to describe a design , Schematic design tools are supporting tools with perfect connectivity .

Timeliness is the ability to express the time change of the evolution of design state , This ability is different from measuring the time taken by a code to execute .

Parallelism is the ability to describe simultaneous independent behaviors .

边栏推荐

猜你喜欢

AutoCAD -- Method of calculating area

Implementation of recommendation system collaborative filtering in spark

The best way to practice Animation: cover transition

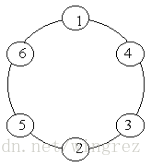

Prime Ring Problem

After reading this article, you should thoroughly understand how to do interface testing

What should I do when my blog is attacked by hackers?

Big view +500 cases, software teams should improve R & D efficiency in this way

推荐⼀款超好⽤的UI⾃动化⼯具: UiAutomator2!

MDK compilation process and arm compilation tool chain

Overview of database stress testing methods

随机推荐

6 + 1 skills of Software Test Engineer

给RestTemplate添加拦截器记录请求响应,还需解决流只读一次的问题

Is it safe to buy funds on e fund? Professional answers

npm ERR! code ETIMEDOUTnpm ERR! syscall connectnpm ERR! errno ETIMEDOUTnpm ERR! network request t

4QAM, 16QAM modulation and demodulation simulation circuit, observe and analyze QAM constellation and bit error rate curve [matlab code]

Format JS code and debug JS code

“蔚来杯“2022牛客暑期多校训练营2 K.[Link with Bracket Sequence I] 括号序列 DP

How to modify Oracle functions?

B - Krypton Factor (dfs+ backtracking method)

Dijkstra 求最短路

Understand Linglong platform unified access service from simple to deep Monet

leetcode/只出现一次的数字

PTGui Pro12垂直线纠正

Leetcode/ numbers that appear only once

快速创建题目文件夹

【深入浅出玩转FPGA学习11----Testbench书写技巧2】

保护系统日志服务器和设备

CPU的三种模式

Huawei wireless device WDS configuration command

Go operation excel library excel use