当前位置:网站首页>CubeMx DMA笔记

CubeMx DMA笔记

2022-07-02 04:53:00 【@残梦】

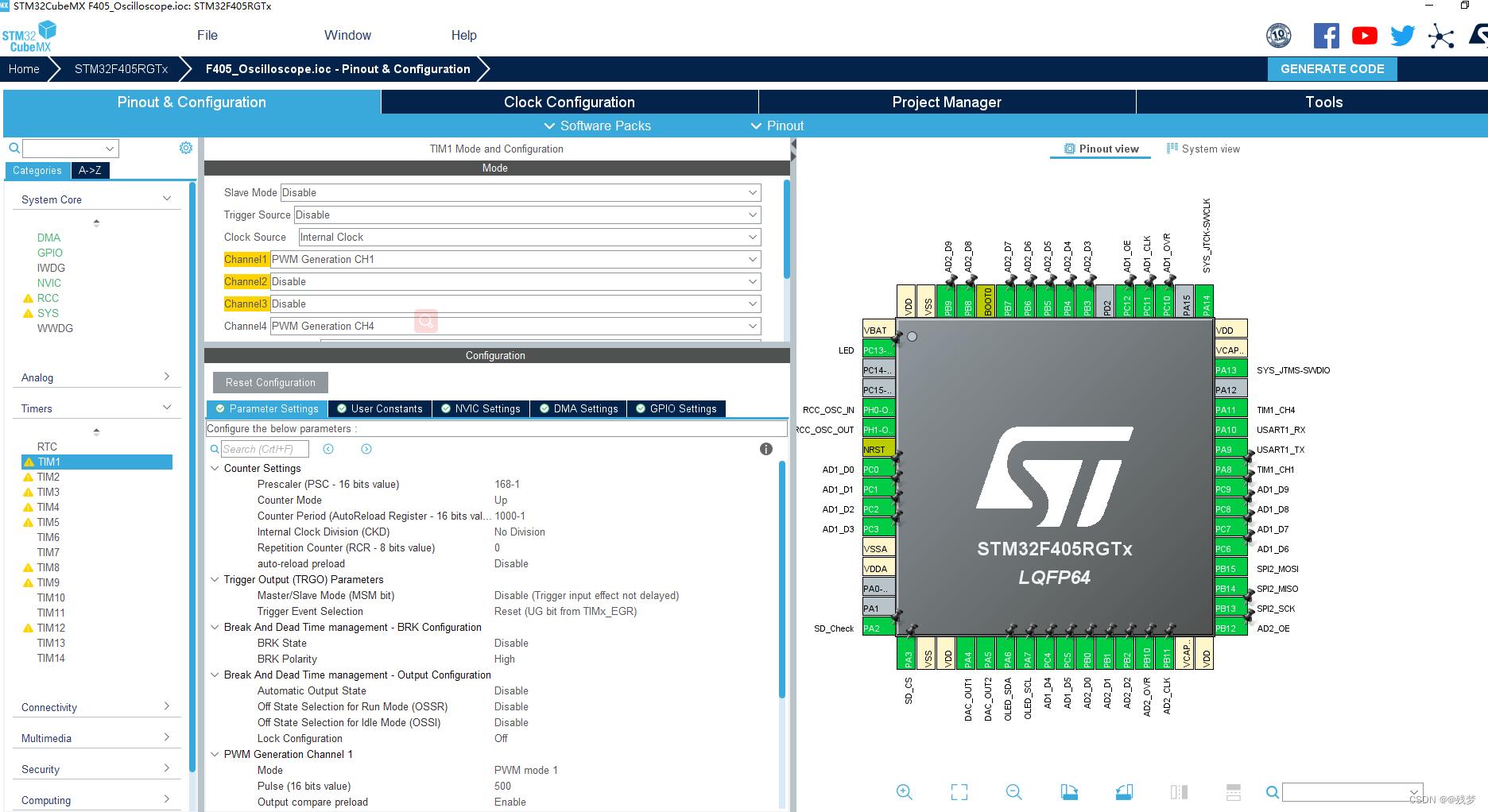

定时器开DMA:

关于DMA初始代码:

static void TIM1_CH4_DMA2_TransferComplete_Callback(DMA_HandleTypeDef *hdma)

{

//printf("TIM1_CH4_DMA2_TransferComplete_Callback\r\n");

//_LED_TURN;

}

uint32_t gpiosta[2] = {

0xFFFF0000,0x0000FFFF};

void TIM1_DMA2_Init(void)

{

HAL_NVIC_DisableIRQ(TIM1_UP_TIM10_IRQn);

HAL_NVIC_DisableIRQ(DMA2_Stream5_IRQn);

HAL_NVIC_DisableIRQ(DMA2_Stream1_IRQn);//禁止中断更新

#if 0//TIM1_UP的DMA

htim1.hdma[TIM_DMA_ID_UPDATE]->XferCpltCallback = TIM1_CH1_DMA2_TransferComplete_Callback;

HAL_DMA_Start_IT(&hdma_tim1_up,(uint32_t)(&gpiosta[0]), (uint32_t)(&(GPIOC->BSRR)),2);//(uint32_t)(&(GPIOC->BSRR))

__HAL_TIM_ENABLE_DMA(&htim1, TIM_DMA_UPDATE);

#else//TIM1_CH1 + TIM1_CH4 的DMA

htim1.hdma[TIM_DMA_ID_CC1]->XferCpltCallback = TIM1_CH1_DMA2_TransferComplete_Callback;

HAL_DMA_Start_IT(&hdma_tim1_ch1,(uint32_t)(&gpiosta[0]), (uint32_t)(&(GPIOB->BSRR)),2);

__HAL_TIM_ENABLE_DMA(&htim1, TIM_DMA_CC1);

htim1.hdma[TIM_DMA_ID_CC4]->XferCpltCallback = TIM1_CH4_DMA2_TransferComplete_Callback;//传输完成回调函数

HAL_DMA_Start_IT(&hdma_tim1_ch4_trig_com,(uint32_t)(&gpiosta[0]), (uint32_t)(&(GPIOC->BSRR)),2);//将gpiosta的数据搬移到GPIOC->BSRR

__HAL_TIM_ENABLE_DMA(&htim1, TIM_DMA_CC4);//使能定时器更新DMA请求

#endif

}

主函数启动:

HAL_TIM_PWM_Start(&htim1,TIM_CHANNEL_1);

HAL_TIM_PWM_Start(&htim1,TIM_CHANNEL_4);

TIM1_DMA2_Init();

while(1)

{

HAL_Delay(3000);

}

关于tim.c全部代码:

/** ****************************************************************************** * @file tim.c * @brief This file provides code for the configuration * of the TIM instances. ****************************************************************************** * @attention * * <h2><center>© Copyright (c) 2022 STMicroelectronics. * All rights reserved.</center></h2> * * This software component is licensed by ST under BSD 3-Clause license, * the "License"; You may not use this file except in compliance with the * License. You may obtain a copy of the License at: * opensource.org/licenses/BSD-3-Clause * ****************************************************************************** */

/* Includes ------------------------------------------------------------------*/

#include "tim.h"

/* USER CODE BEGIN 0 */

/* USER CODE END 0 */

TIM_HandleTypeDef htim1;

DMA_HandleTypeDef hdma_tim1_ch1;

DMA_HandleTypeDef hdma_tim1_ch4_trig_com;

/* TIM1 init function */

void MX_TIM1_Init(void)

{

/* USER CODE BEGIN TIM1_Init 0 */

/* USER CODE END TIM1_Init 0 */

TIM_ClockConfigTypeDef sClockSourceConfig = {

0};

TIM_MasterConfigTypeDef sMasterConfig = {

0};

TIM_OC_InitTypeDef sConfigOC = {

0};

TIM_BreakDeadTimeConfigTypeDef sBreakDeadTimeConfig = {

0};

/* USER CODE BEGIN TIM1_Init 1 */

/* USER CODE END TIM1_Init 1 */

htim1.Instance = TIM1;

htim1.Init.Prescaler = 1-1;

htim1.Init.CounterMode = TIM_COUNTERMODE_UP;

htim1.Init.Period = 168/2-1;

htim1.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1;

htim1.Init.RepetitionCounter = 0;

htim1.Init.AutoReloadPreload = TIM_AUTORELOAD_PRELOAD_DISABLE;

if (HAL_TIM_Base_Init(&htim1) != HAL_OK)

{

Error_Handler();

}

sClockSourceConfig.ClockSource = TIM_CLOCKSOURCE_INTERNAL;

if (HAL_TIM_ConfigClockSource(&htim1, &sClockSourceConfig) != HAL_OK)

{

Error_Handler();

}

if (HAL_TIM_PWM_Init(&htim1) != HAL_OK)

{

Error_Handler();

}

sMasterConfig.MasterOutputTrigger = TIM_TRGO_RESET;

sMasterConfig.MasterSlaveMode = TIM_MASTERSLAVEMODE_DISABLE;

if (HAL_TIMEx_MasterConfigSynchronization(&htim1, &sMasterConfig) != HAL_OK)

{

Error_Handler();

}

sConfigOC.OCMode = TIM_OCMODE_PWM1;

sConfigOC.Pulse = htim1.Init.Period/2;

sConfigOC.OCPolarity = TIM_OCPOLARITY_HIGH;

sConfigOC.OCNPolarity = TIM_OCNPOLARITY_HIGH;

sConfigOC.OCFastMode = TIM_OCFAST_DISABLE;

sConfigOC.OCIdleState = TIM_OCIDLESTATE_RESET;

sConfigOC.OCNIdleState = TIM_OCNIDLESTATE_RESET;

if (HAL_TIM_PWM_ConfigChannel(&htim1, &sConfigOC, TIM_CHANNEL_1) != HAL_OK)

{

Error_Handler();

}

if (HAL_TIM_PWM_ConfigChannel(&htim1, &sConfigOC, TIM_CHANNEL_4) != HAL_OK)

{

Error_Handler();

}

sBreakDeadTimeConfig.OffStateRunMode = TIM_OSSR_DISABLE;

sBreakDeadTimeConfig.OffStateIDLEMode = TIM_OSSI_DISABLE;

sBreakDeadTimeConfig.LockLevel = TIM_LOCKLEVEL_OFF;

sBreakDeadTimeConfig.DeadTime = 0;

sBreakDeadTimeConfig.BreakState = TIM_BREAK_DISABLE;

sBreakDeadTimeConfig.BreakPolarity = TIM_BREAKPOLARITY_HIGH;

sBreakDeadTimeConfig.AutomaticOutput = TIM_AUTOMATICOUTPUT_DISABLE;

if (HAL_TIMEx_ConfigBreakDeadTime(&htim1, &sBreakDeadTimeConfig) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN TIM1_Init 2 */

/* USER CODE END TIM1_Init 2 */

HAL_TIM_MspPostInit(&htim1);

}

void HAL_TIM_Base_MspInit(TIM_HandleTypeDef* tim_baseHandle)

{

if(tim_baseHandle->Instance==TIM1)

{

/* USER CODE BEGIN TIM1_MspInit 0 */

/* USER CODE END TIM1_MspInit 0 */

/* TIM1 clock enable */

__HAL_RCC_TIM1_CLK_ENABLE();

/* TIM1 DMA Init */

/* TIM1_CH1 Init */

hdma_tim1_ch1.Instance = DMA2_Stream1;

hdma_tim1_ch1.Init.Channel = DMA_CHANNEL_6;

hdma_tim1_ch1.Init.Direction = DMA_PERIPH_TO_MEMORY;

hdma_tim1_ch1.Init.PeriphInc = DMA_PINC_DISABLE;

hdma_tim1_ch1.Init.MemInc = DMA_MINC_ENABLE;

hdma_tim1_ch1.Init.PeriphDataAlignment = DMA_PDATAALIGN_WORD;

hdma_tim1_ch1.Init.MemDataAlignment = DMA_MDATAALIGN_WORD;

hdma_tim1_ch1.Init.Mode = DMA_CIRCULAR;

hdma_tim1_ch1.Init.Priority = DMA_PRIORITY_VERY_HIGH;

hdma_tim1_ch1.Init.FIFOMode = DMA_FIFOMODE_DISABLE;

if (HAL_DMA_Init(&hdma_tim1_ch1) != HAL_OK)

{

Error_Handler();

}

__HAL_LINKDMA(tim_baseHandle,hdma[TIM_DMA_ID_CC1],hdma_tim1_ch1);

/* TIM1_CH4_TRIG_COM Init */

hdma_tim1_ch4_trig_com.Instance = DMA2_Stream4;

hdma_tim1_ch4_trig_com.Init.Channel = DMA_CHANNEL_6;

hdma_tim1_ch4_trig_com.Init.Direction = DMA_PERIPH_TO_MEMORY;

hdma_tim1_ch4_trig_com.Init.PeriphInc = DMA_PINC_DISABLE;

hdma_tim1_ch4_trig_com.Init.MemInc = DMA_MINC_ENABLE;

hdma_tim1_ch4_trig_com.Init.PeriphDataAlignment = DMA_PDATAALIGN_WORD;

hdma_tim1_ch4_trig_com.Init.MemDataAlignment = DMA_MDATAALIGN_WORD;

hdma_tim1_ch4_trig_com.Init.Mode = DMA_CIRCULAR;

hdma_tim1_ch4_trig_com.Init.Priority = DMA_PRIORITY_VERY_HIGH;

hdma_tim1_ch4_trig_com.Init.FIFOMode = DMA_FIFOMODE_DISABLE;

if (HAL_DMA_Init(&hdma_tim1_ch4_trig_com) != HAL_OK)

{

Error_Handler();

}

/* Several peripheral DMA handle pointers point to the same DMA handle. Be aware that there is only one stream to perform all the requested DMAs. */

__HAL_LINKDMA(tim_baseHandle,hdma[TIM_DMA_ID_CC4],hdma_tim1_ch4_trig_com);

__HAL_LINKDMA(tim_baseHandle,hdma[TIM_DMA_ID_TRIGGER],hdma_tim1_ch4_trig_com);

__HAL_LINKDMA(tim_baseHandle,hdma[TIM_DMA_ID_COMMUTATION],hdma_tim1_ch4_trig_com);

/* USER CODE BEGIN TIM1_MspInit 1 */

/* USER CODE END TIM1_MspInit 1 */

}

}

void HAL_TIM_MspPostInit(TIM_HandleTypeDef* timHandle)

{

GPIO_InitTypeDef GPIO_InitStruct = {

0};

if(timHandle->Instance==TIM1)

{

/* USER CODE BEGIN TIM1_MspPostInit 0 */

/* USER CODE END TIM1_MspPostInit 0 */

__HAL_RCC_GPIOA_CLK_ENABLE();

/**TIM1 GPIO Configuration PA8 ------> TIM1_CH1 PA11 ------> TIM1_CH4 */

GPIO_InitStruct.Pin = GPIO_PIN_8|GPIO_PIN_11;

GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_VERY_HIGH;

GPIO_InitStruct.Alternate = GPIO_AF1_TIM1;

HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

/* USER CODE BEGIN TIM1_MspPostInit 1 */

/* USER CODE END TIM1_MspPostInit 1 */

}

}

void HAL_TIM_Base_MspDeInit(TIM_HandleTypeDef* tim_baseHandle)

{

if(tim_baseHandle->Instance==TIM1)

{

/* USER CODE BEGIN TIM1_MspDeInit 0 */

/* USER CODE END TIM1_MspDeInit 0 */

/* Peripheral clock disable */

__HAL_RCC_TIM1_CLK_DISABLE();

/* TIM1 DMA DeInit */

HAL_DMA_DeInit(tim_baseHandle->hdma[TIM_DMA_ID_CC1]);

HAL_DMA_DeInit(tim_baseHandle->hdma[TIM_DMA_ID_CC4]);

HAL_DMA_DeInit(tim_baseHandle->hdma[TIM_DMA_ID_TRIGGER]);

HAL_DMA_DeInit(tim_baseHandle->hdma[TIM_DMA_ID_COMMUTATION]);

/* USER CODE BEGIN TIM1_MspDeInit 1 */

/* USER CODE END TIM1_MspDeInit 1 */

}

}

/* USER CODE BEGIN 1 */

void HAL_TIM_PeriodElapsedCallback(TIM_HandleTypeDef *htim)

{

if(htim->Instance == TIM1)

{

//_LED_TURN;

//printf("HAL_TIM_PeriodElapsedCallback\r\n");

}

}

static void TIM1_CH1_DMA2_TransferComplete_Callback(DMA_HandleTypeDef *hdma)

{

//printf("TIM1_CH1_DMA2_TransferComplete_Callback\r\n");

//_LED_TURN;

}

static void TIM1_CH4_DMA2_TransferComplete_Callback(DMA_HandleTypeDef *hdma)

{

//printf("TIM1_CH4_DMA2_TransferComplete_Callback\r\n");

//_LED_TURN;

}

uint32_t gpiosta[2] = {

0xFFFF0000,0x0000FFFF};

void TIM1_DMA2_Init(void)

{

HAL_NVIC_DisableIRQ(TIM1_UP_TIM10_IRQn);

HAL_NVIC_DisableIRQ(DMA2_Stream5_IRQn);

HAL_NVIC_DisableIRQ(DMA2_Stream1_IRQn);//禁止中断更新

#if 0//TIM1_UP的DMA

htim1.hdma[TIM_DMA_ID_UPDATE]->XferCpltCallback = TIM1_CH1_DMA2_TransferComplete_Callback;

HAL_DMA_Start_IT(&hdma_tim1_up,(uint32_t)(&gpiosta[0]), (uint32_t)(&(GPIOC->BSRR)),2);//(uint32_t)(&(GPIOC->BSRR))

__HAL_TIM_ENABLE_DMA(&htim1, TIM_DMA_UPDATE);

#else//TIM1_CH1 + TIM1_CH4 的DMA

htim1.hdma[TIM_DMA_ID_CC1]->XferCpltCallback = TIM1_CH1_DMA2_TransferComplete_Callback;

HAL_DMA_Start_IT(&hdma_tim1_ch1,(uint32_t)(&gpiosta[0]), (uint32_t)(&(GPIOB->BSRR)),2);

__HAL_TIM_ENABLE_DMA(&htim1, TIM_DMA_CC1);

htim1.hdma[TIM_DMA_ID_CC4]->XferCpltCallback = TIM1_CH4_DMA2_TransferComplete_Callback;//传输完成回调函数

HAL_DMA_Start_IT(&hdma_tim1_ch4_trig_com,(uint32_t)(&gpiosta[0]), (uint32_t)(&(GPIOC->BSRR)),2);//将gpiosta的数据搬移到GPIOC->BSRR

__HAL_TIM_ENABLE_DMA(&htim1, TIM_DMA_CC4);//使能定时器更新DMA请求

#endif

}

/* USER CODE END 1 */

/************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

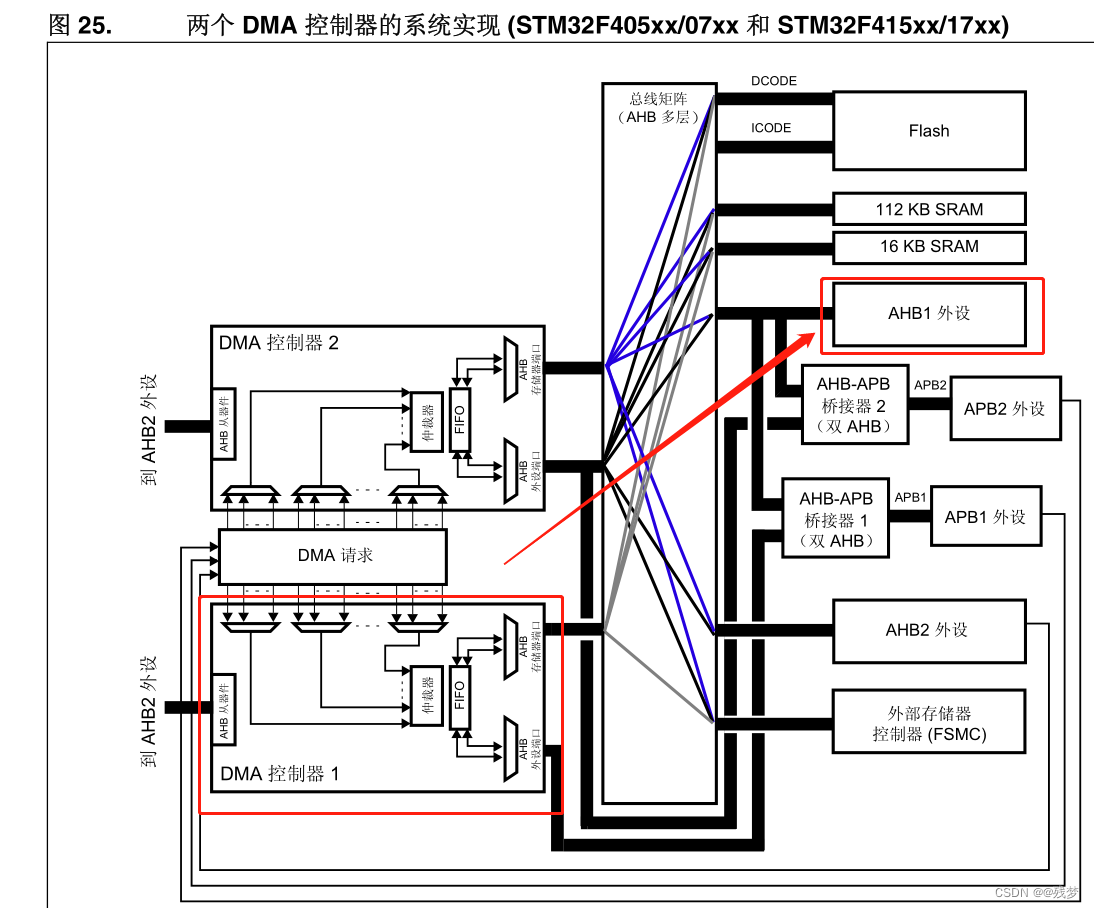

关于DMA使用的外设地址一定需要满足DMA的传输限制:比如此图中的DMA1是不能访问AHB1外设的,也就是比如不能DMA1搬移GPIOC\GPIOB等外设的数据传输

边栏推荐

- Rhcsa --- work on the fourth day

- Realize the function of data uploading

- Common errors of dmrman offline backup

- Research on the security of ognl and El expressions and memory horse

- 数学知识(欧拉函数)

- geotrust ov多域名ssl證書一年兩千一百元包含幾個域名?

- Orthogonal test method and function diagram method for test case design

- 培养中小学生对教育机器人的热爱之心

- Comp 250 parsing

- The core idea of performance optimization, dry goods sharing

猜你喜欢

Lm09 Fisher inverse transform inversion mesh strategy

Unit testing classic three questions: what, why, and how?

Interview question: do you know the difference between deep copy and shallow copy? What is a reference copy?

One click generation and conversion of markdown directory to word format

Tawang food industry insight | current situation, consumption data and trend analysis of domestic infant complementary food market

Unity particle Foundation

How do I interview for a successful software testing position? If you want to get a high salary, you must see the offer

![[Yu Yue education] autumn 2021 reference materials of Tongji University](/img/50/5136359b89a5d047fe648637643ad0.jpg)

[Yu Yue education] autumn 2021 reference materials of Tongji University

Cache consistency solution - how to ensure the consistency between the cache and the data in the database when changing data

06 decorator mode

随机推荐

Free drawing software recommended - draw io

AcrelEMS高速公路微电网能效管理平台与智能照明解决方案智慧点亮隧道

Flag bits in assembly language: CF, PF, AF, ZF, SF, TF, if, DF, of

One step implementation of yolox helmet detection (combined with oak intelligent depth camera)

Several methods of capturing packets under CS framework

oracle 存储过程与job任务设置

Cannot activate CONDA virtual environment in vscode

Lm09 Fisher inverse transform inversion mesh strategy

cs架构下抓包的几种方法

Summary of main account information of zhengdaliu 4

数据库问题汇总

GeoTrust ov multi domain SSL certificate is 2100 yuan a year. How many domain names does it contain?

Go Chan's underlying principles

Geotrust OV Multi - Domain Domain SSL Certificate rmb2100 per year contains several Domain names?

Oracle和MySQL的基本区别(入门级)

Use of typescript classes

Getting started with pytest ----- confitest Application of PY

6.30年终小结,学生时代结束

万卷共知,一书一页总关情,TVP读书会带你突围阅读迷障!

What are the rules and trading hours of agricultural futures contracts? How much is the handling fee deposit?