当前位置:网站首页>[play with FPGA learning 4 in simple terms ----- talk about state machine design]

[play with FPGA learning 4 in simple terms ----- talk about state machine design]

2022-07-02 11:01:00 【Ape Zhou】

Play in depth FPGA Study 4---- Talk about the design of state machine

The basic concept of state machine

Hardware design pays attention to the idea of concurrent design , Although with Verilog Most of the circuits described are implemented in parallel , But for practical engineering applications , It is often necessary for hardware to realize some work with a certain order , This requires the idea of state machine . To put it simply , State machine is to complete some specific sequential logic through different state migration . The parallelism of hardware determines the use of Verilog Described hardware implementation ( For example, different always sentence ) It's all in parallel , So if you want to finish a task in multiple times , What do I do ? It may be possible to use multiple enabling signals to connect multiple different modules , But doing so is somewhat cumbersome . The introduction of state machine will greatly simplify this work .

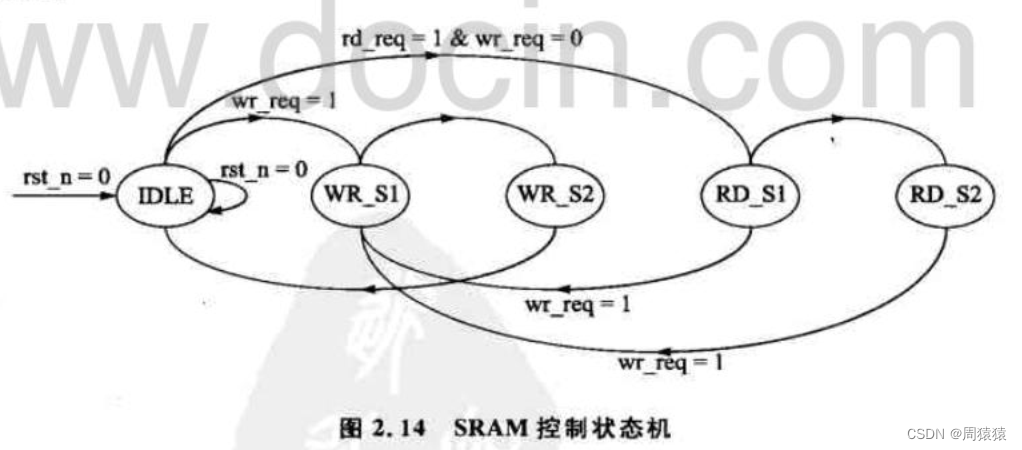

Here's one SRAM Control example to illustrate the state machine . As shown in the figure , It represents a SRAM Change of control state

First , Reset the signal in the system rst_n=0( Reset valid ) after , Get into IDLE state . whenever rst_n=0( Reset valid ) when , Will remain at IDLE state ; When rst_n=1( Reset complete ), If wr_req=1 To get into WR_S1 state , If rd_req=1 Will enter RD_S1 state , Otherwise keep IDLE The state remains the same . Corresponding , As long as certain conditions are met or sometimes no conditions are required , The system will switch between these fixed States . The advantage of doing this is that whenever you need to operate SRAM when , Other modules only need to send one wr_req perhaps rd_req The signal ( Set high ), The system will enter the corresponding state and adjust SRAM Control bus 、 Assign values to the address bus and data bus .

The basic element of the state machine is the input of the state machine 、 Output and state . Inputs are conditions that cause state changes , Like in the picture wr_req and rd_req The change of will cause the state to migrate , Then they are inputs ; Output is the change caused by the state change , The control bus in the figure 、 The output value of address bus and data bus is the change caused by the state change , State is IDLE、WR_S1、WR_S2 etc. , They are generally represented by some logical values .

State machines can be divided into two categories according to whether their state changes are related to input conditions , namely Moore State machine and Mealy State machine .Moore The state change of the type-A state machine is only related to the current state , It has nothing to do with the input conditions ;Mealy The state change of the type-A state machine is not only related to the current state , It also depends on the current input conditions .

Some classifications also propose finite state machines (FSM) And infinite state machines (ISM), But in actual design, it generally refers to finite state machine .

Three different state machines

There are generally three different ways to write a state machine , That is, one-stage 、 Two stage and three stage state machines , They are at speed 、 area 、 Code maintainability and other aspects have advantages and disadvantages . The following is a SRAM Control state machine gives three different ways to write and their combined effect .wr_req and rd_req As input ,cmd For export ,cstate、nstate Is the status register .

One stage state machine

The code of one segment state machine is as follows :

reg[3:0] cstate;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

cstate <= IDLE;

cmd <= 3'b111;

end

else

case(cstate)

IDLE: if(wr_req) begin

cstate <= WR_S1;

cmd <= 3'b011;

end

else begin

cstate <= IDLE;

cmd <= 3'b111;

end

WR_S1: begin

cstate <= WR_S2;

cmd <= 3'b101;

end

WR_S2: begin

cstate <= IDLE;

cmd <= 3'b111;

end

RD_S1: if (wr_req) begin

cstate <= WR_S2;

cmd <= 3'b101;

end

else begin

cstate <= RD_S2;

cmd <= 3'b110;

end

RD_S2: if (wr_req) begin

cstate <= WR_S1;

cmd <= 3'b011;

end

else begin

cstate <= IDLE;

cmd <= 3'b111;

end

default: cstate <= IDLE;

endcase

end

One stage state machine RTL See figure for the view :

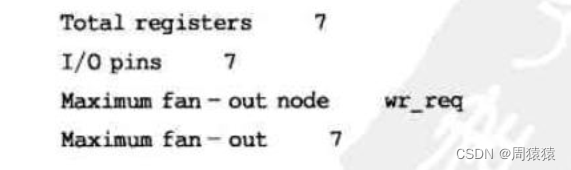

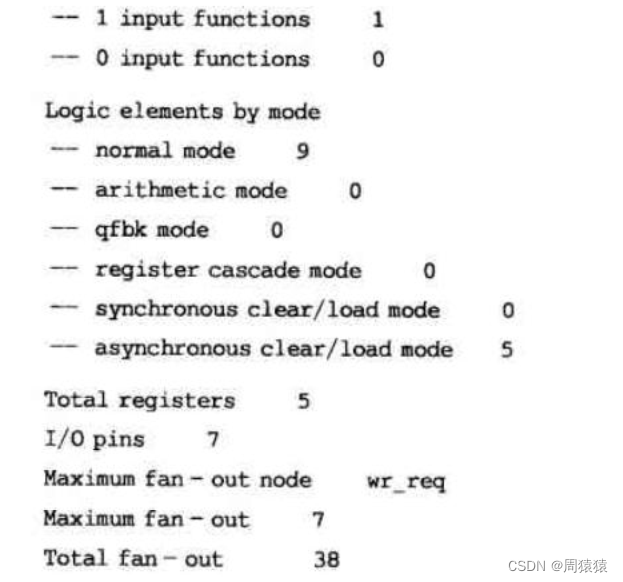

Resource usage report after one-stage state machine synthesis :

Two stage state machine

The two-stage state machine code is as follows :

reg[3:0] cstate;

reg[3:0] nstate;

always @ (posedge clk or negedge rst_n)

if(!rst_n) cstate <= IDLE;

else cstate <= nstate;

always @ (cstate or wr_req or rd_req) begin

case(cstate)

IDLE: if(wr_req) begin

nstate = WR_S1;

cmd = 3 'b011;

end

else if(rd_req) begin

nstate = RD_S1;

cmd = 3'b011;

end

else begin

nstate = IDLE;

cmd = 3'b111;

end

WR_S1: begin

nstate = WR_S2;

cmd = 3'b101;

end

WR_S2: begin

nstate = IDLE;

cmd = 3'b111;

end

RD_S1: if(wr_req) begin

nstate = WR_S2;

cmd = 3'b101;

end

else begin

nstate = RD_S2;

cmd = 3'b110;

end

RD_S2: if(wr_req) begin

nstate = WR_S1;

cmd = 3'b011;

end

else begin

nstate = IDLE;

cmd = 3'b111;

end

default: nstate = IDLE;

endcase

end

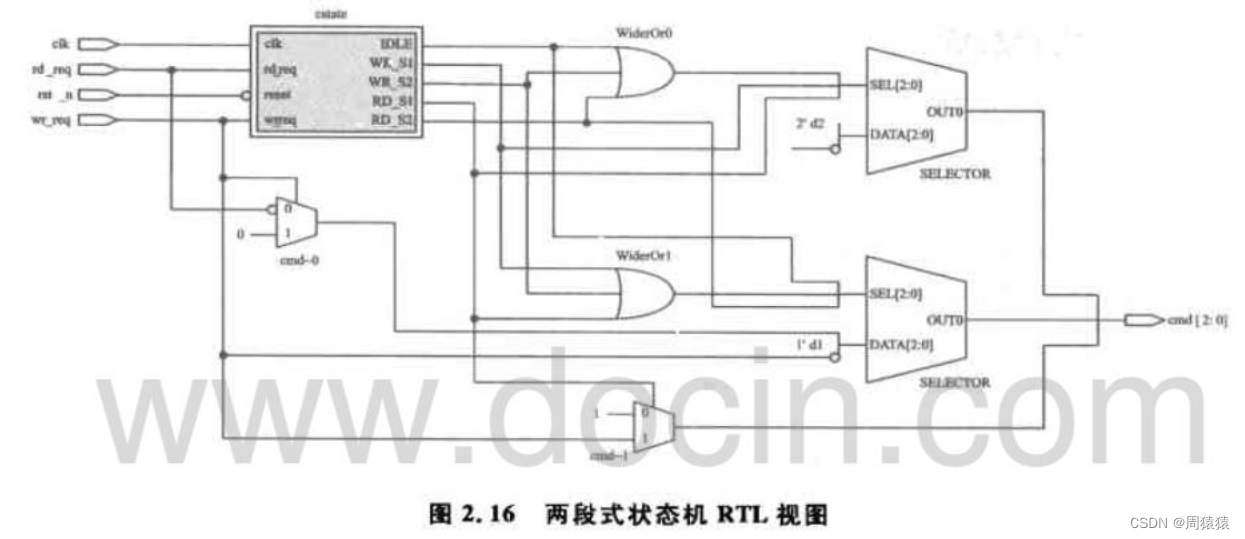

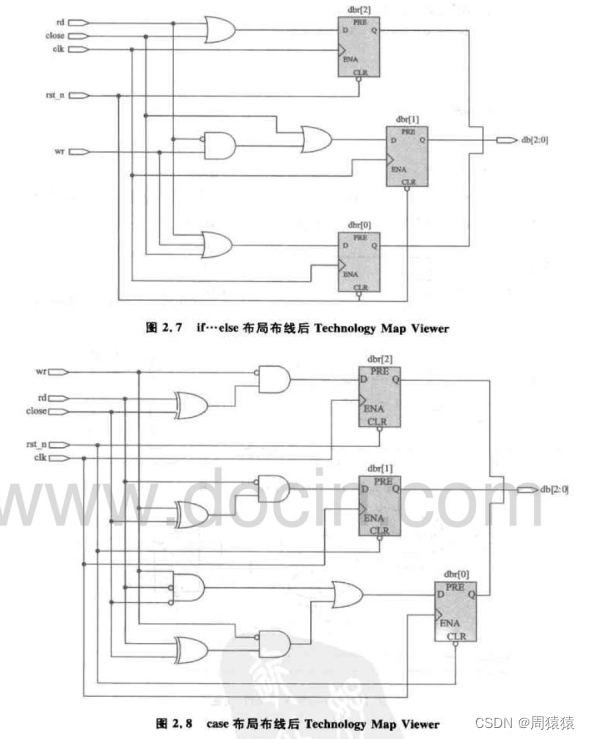

Two stage state machine RTL See figure for the view :

Resource usage report after two-stage state machine synthesis :

Three stage state machine

The three segment state machine code is as follows :

reg[3:0] cstate;

reg[3:0] nstate;

always @ (posedge clk or negedge rst_n)

if(!rst_n) cstate <= IDLE;

else cstate <= nstate;

always @ (cstate or wr_req or rd_req) begin

case(cstate)

IDLE: if(wr_req) nstate = WR_S1;

else if(rd_req) nstate = RD_S1;

else nstate = IDLE;

WR_S1: nstate = WR_S2;

WR_S2: nstate = IDLE;

RD_S1: if(wr_req) nstate = WR_S2;

else nastate = RD_S2;

RD_S2: if(wr_req) nstate = WR_S1;

else nstate = IDLE;

default: nstate = IDLE;

endcase

end

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) cmd <= 3'b111;

else

case(nstate)

IDLE: if(wr_req) cmd <= 3'b011;

else if(rd_req) cmd <= 3'b011;

else cmd <= 3'b111;

WR_S1: cmd <= 3'b101;

WR_S2: cmd <= 3'b111;

RD_S1: if(wr_req) cmd <= 3'b101;

else cmd <= 3'b110;

RD_S2: if(wr_req) cmd <= 3'b011;

else cmd <= 3'b111;

default: ;

endcase

end

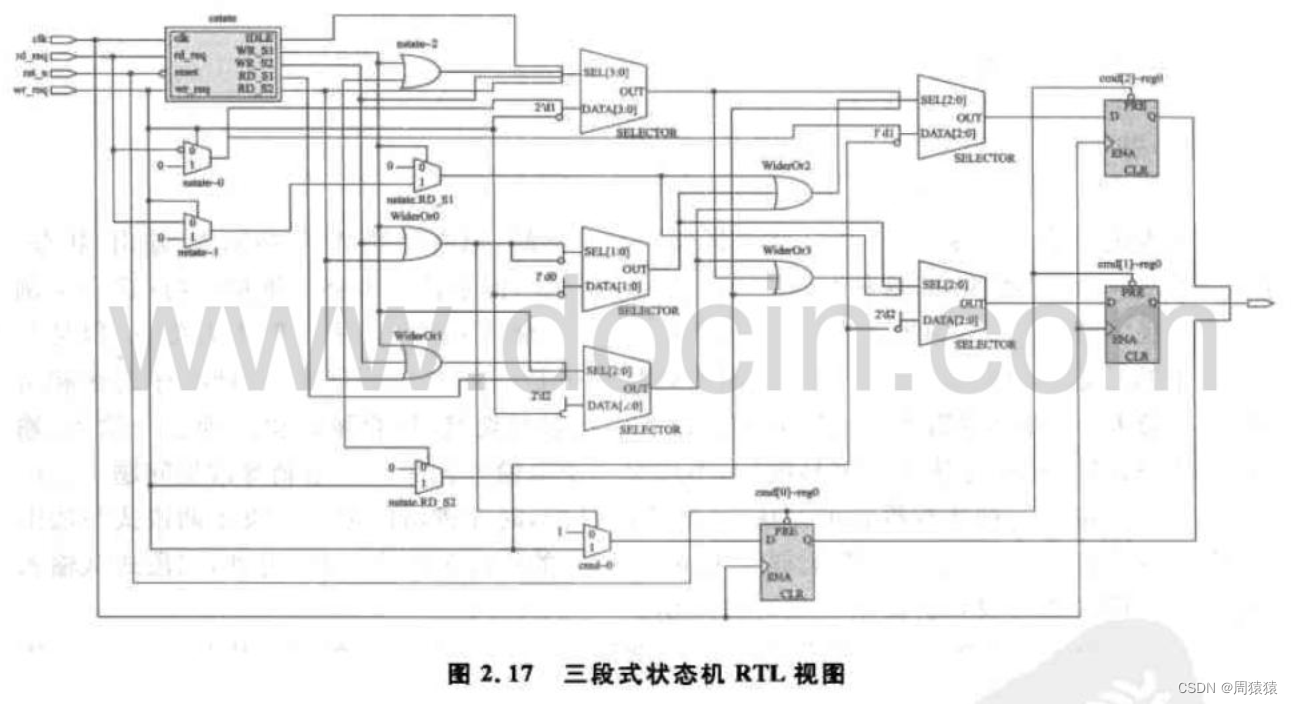

Three stage state machine RTL See figure for the view :

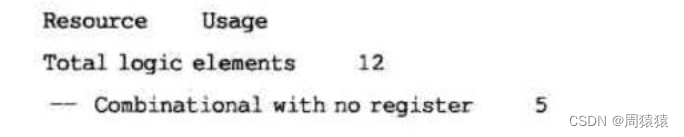

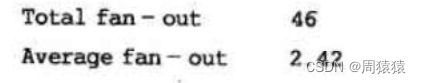

Resource usage report after three-stage state machine synthesis :

From the above three examples , One stage state machine seems to be one pot , Put all the logic ( Including the input 、 Output 、 state ) All in one always It's solved in the library ; This kind of writing seems very concise , But it is often not conducive to maintenance , Maybe this example is not so obvious , If the state is more complex, it is easy to make mistakes ; This kind of writing is generally not recommended , But it can be used in some simple state machines . The two-stage state machine is a common way of writing , He divided temporal logic and combinatorial logic , Switch between the current state and the next state in sequential logic , Combinational logic implements each input 、 Output and state judgment ; This writing method is relatively easy to maintain , However, the output of combinational logic is prone to common problems such as burrs . The three-stage state machine writing method is also a more recommended writing method , The code is easy to maintain , The output of sequential logic solves the burr problem of two-stage writing of combinatorial logic ; But in terms of resource consumption , The three-stage method consumes more resources ; in addition , Three stage mode will delay one clock cycle from input to output compared with one stage mode and two stage mode .

边栏推荐

猜你喜欢

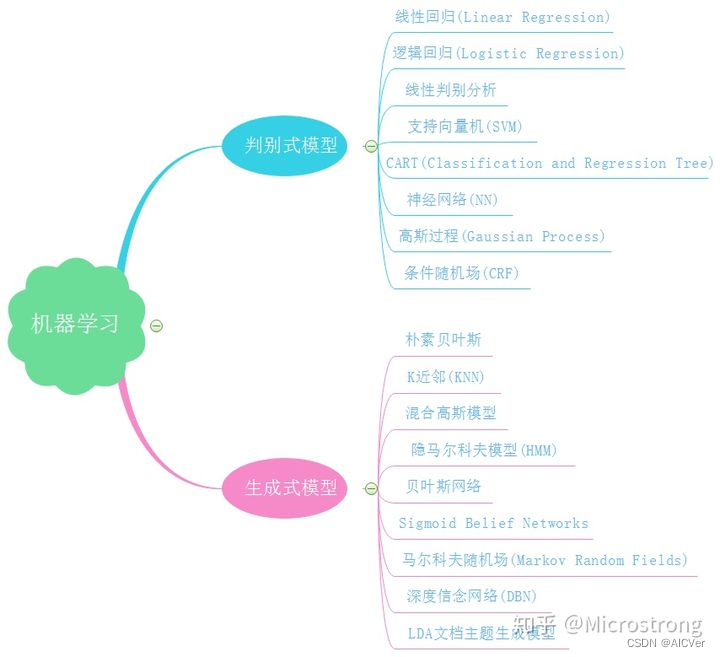

Overview of integrated learning

OpenMLDB Meetup No.4 会议纪要

《实习报告》Skywalking分布式链路追踪?

V2X-Sim数据集(上海交大&纽约大学)

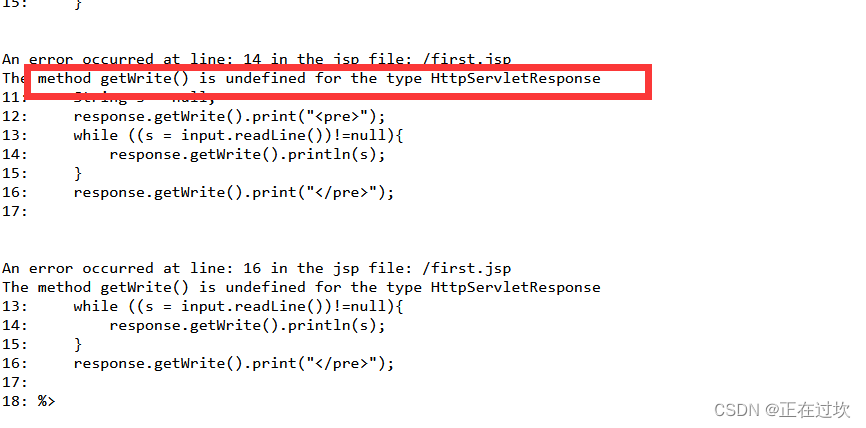

JSP webshell free -- webshell free

JVM之垃圾回收器

【深入浅出玩转FPGA学习2----设计技巧(基本语法)】

Internet News: Tencent conference application market was officially launched; Soul went to Hong Kong to submit the listing application

2022-06-17

How to implement tabbar title bar with list component

随机推荐

MySQL lethal serial question 3 -- are you familiar with MySQL locks?

Pywin32 opens the specified window

K-d tree and octree of PCL

UVM - usage of common TLM port

Operator-1 first acquaintance with operator

UVM factory mechanism

V2X-Sim数据集(上海交大&纽约大学)

二叉树专题--AcWing 1589. 构建二叉搜索树

点云投影图片

全网显示 IP 归属地,是怎么实现的?

JVM garbage collector

JSP webshell免杀——webshell免杀

华为AppLinking中统一链接的创建和使用

Analysis of hot spots in AI technology industry

【深入浅出玩转FPGA学习5-----复位设计】

Internet News: Tencent conference application market was officially launched; Soul went to Hong Kong to submit the listing application

6种单例模式的实现方式

[AGC] build service 3 - authentication service example

Luogu p5536 [xr-3] core city (greed + tree DP looking for the center of the tree)

Set the playback speed during the playback of UOB equipment