当前位置:网站首页>第十一章 开关级建模

第十一章 开关级建模

2022-08-05 00:46:00 【江南小作坊】

基本概念

- 在少数情况下,可能会选择用晶体管作为设计的底层模块,即叶级模块(leaf-level)。Verilog语言具有对MOS晶体管级进行设计的能力。

- 由于电路复杂性的增加,及各种更加先进的CAD工具,开关级为基础的设计慢慢少了。

- Verilog HDL仅提供用逻辑值0,1,x,z和它们相关的驱动强度进行数字设计的能力(MOS管用于开关应用),无法用于模拟设计。

- 学习流程图

建模元件

- 最基本的电路模型元件

MOS开关

- 关键字:

nmos,pmos - nmos与pmos开关符号

- 调用实例

// 调用nmos和pmos开关

nmos n1(out, data, control);

pmos p1(out, data, control);

// 调用nmos和pmos开关,可以无实例名称

nmos (out, data, control);

pmos (out, data, control);

- 上例中,out的值由data和control控制,逻辑值如下

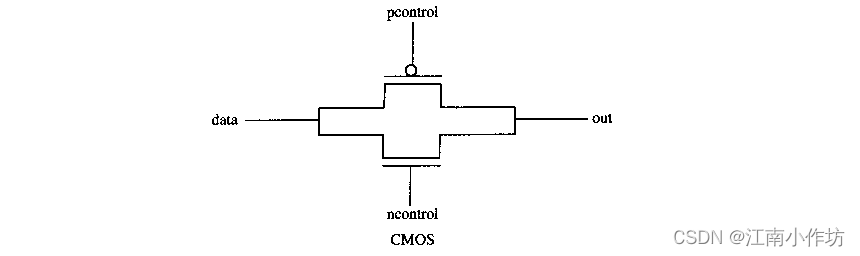

CMOS开关

- 关键字:

cmos - cmos开关符号

- 实例引用

// 有实例名调用和无实例名调用

cmos c1(out, data, ncontrol, pcontrol);

cmos (out, data, ncontrol, pcontrol);

- 可以使用nmos和pmos器件来建立cmos器件的模型

nmos (out, data, ncontrol);

pmos (out, data, pcontrol);

- 逻辑值可以由pmos和nmos的逻辑值推导而来,这里不再赘述。

双向开关

- 关键字:

tran,tranif0,tranif1 - 开关符号

- 引用实例

tran t1(inout1, inout2);

tranf0 (inout1, inout2, control);

tranf1 (inout1, inout2, control);

- 逻辑如下:

- tran开关作为两个信号inout1和inout2之间的缓存。inout1和inout2都可以是驱动信号。

- control为0,tranf0 开关连接inout1和inout2。

- control为1,tranf0没有驱动源的信号取高阻态z,有驱动源信号仍从驱动源取值。

- control为0,tranf1 开关导通。

- 双向开关经常用来在总线或信号之间提供隔离。

电源和地

- 源极(Vdd,逻辑1),漏极(Vss,逻辑0)。关键字:

supply1,supply0 supply1等于电路中Vdd,并将逻辑1放在网表中。supply0等于电路中Vss或地,并将逻辑0放在网表中。- 使用如下

supply1 vdd;

supply0 gnd;

assign a = vdd; //a连接到电源电压vdd

assign b = gnd; // b连接到gnd

阻抗开关

- 阻抗开关具有更高的源极到漏极的阻抗,用以减小信号强度。

- 在一般开关关键字前加带

r前缀,即可声明阻抗开关。

rnmos rpmos //阻抗性nmos和pmos

rcmos // 阻抗性CMOS开关

rtran rtranf0 rtranf1 // 阻抗性双向开关

- 阻抗开关的强度如下

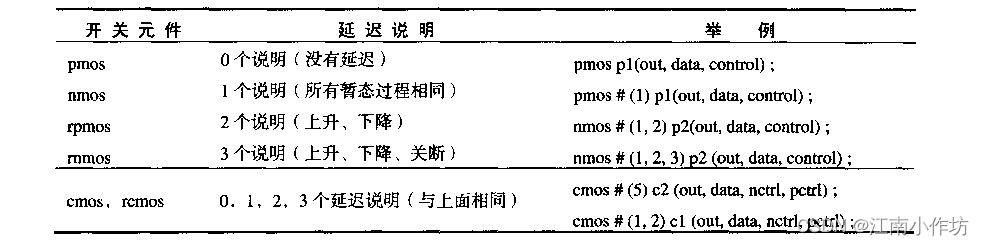

延迟说明

- 可以为通过开关级元件的信号指定延迟,延迟是可选项,紧跟在开关的关键字之后。

- MOS和CMOS开关延迟说明

- 双向传输开关

- specify块的延迟完全可以用于该模型的建模。

举例说明

CMOS或非门(nor)

- 电路图

- Verilog代码

module my_nor(

output out,

input a,b

);

// 定义内部连线

wire c;

// 定义地和电源线

supply0 gnd;

supply1 pwr;

// 引用PMOS

pmos (c, pwr, b);

pmos (out, c, a);

// 引用nmos

nmos (out, gnd, a);

nmos (out, gnd, b);

endmodule

- 可惜我的quartus并不能综合MOS开关门,运行报错如下:

Error (10014): Verilog HDL unsupported feature error at file "my_nor.v" (line 14): cannot synthesize MOS switch gate primitive - 可见这么使用,确实是很少用,做了解即可。

- 仿真代码如图:

二选一多路选择器

用cmos开关来定义二选一多路选择器

电路图

Verilog描述如下

CMOS锁存器

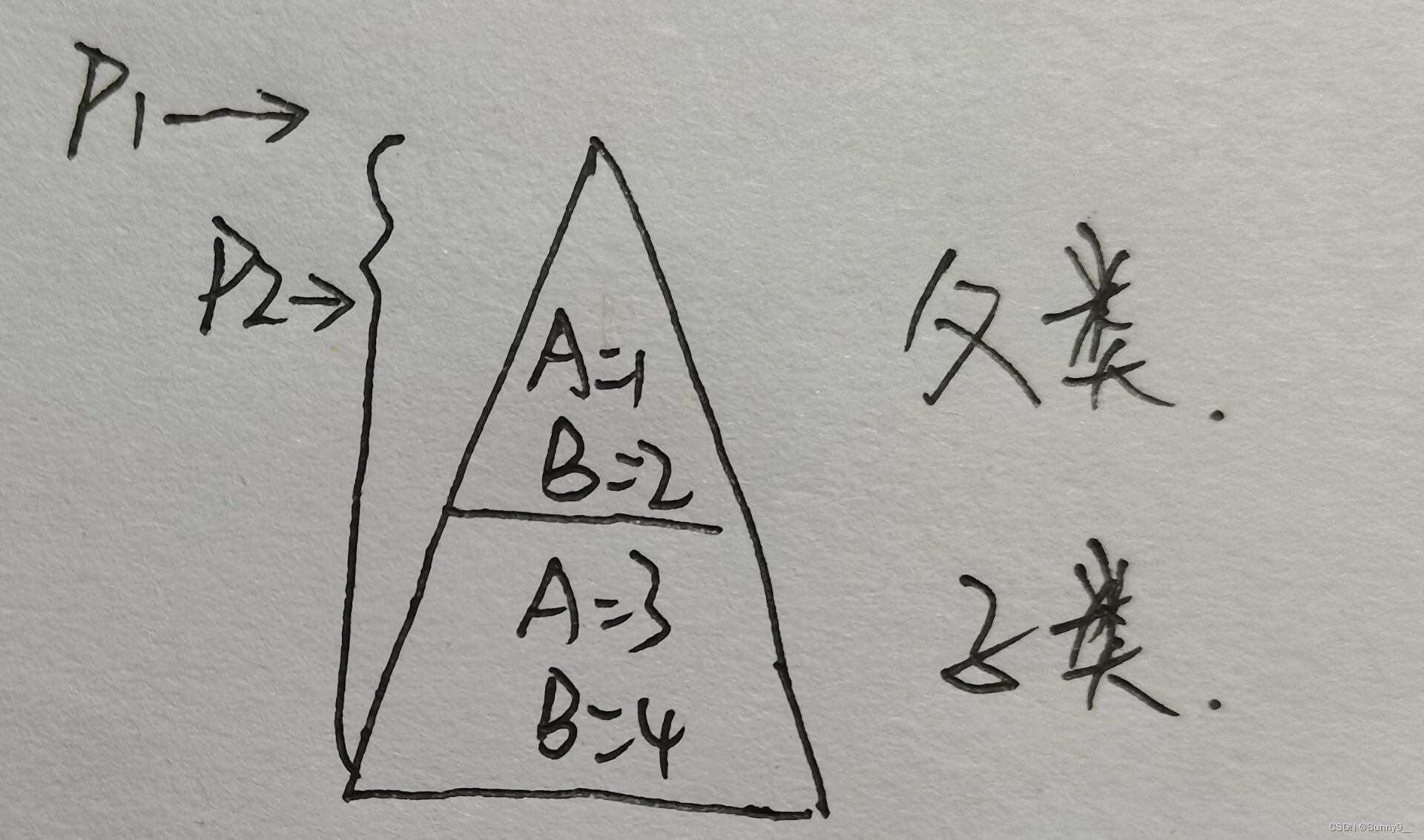

- 定义一个可以存储值的存储元件,电路图如下

- 逻辑:clk=1,则C1开关关闭;clk=0,则C2开关关闭,clk的相反值送给C2的ncontrol输入端。

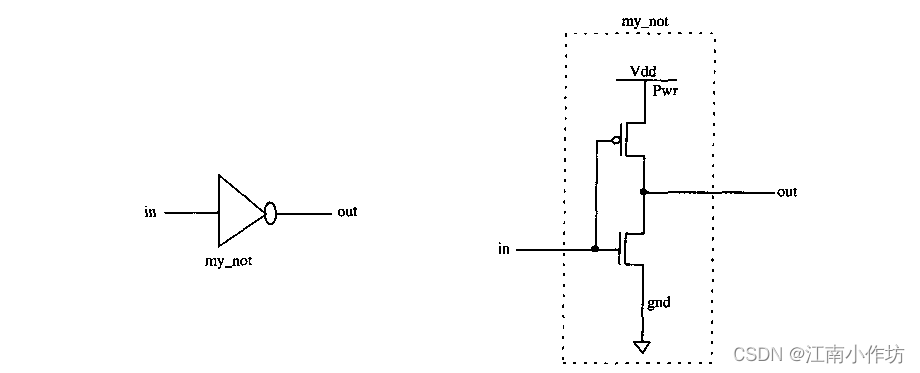

- 用MOS开关定义CMOS反相器

- 反相器Verilog描述

- CMOS锁存器描述

边栏推荐

- Software testing interview questions: the difference and connection between black box testing, white box testing, and unit testing, integration testing, system testing, and acceptance testing?

- 2022牛客多校第三场 A Ancestor

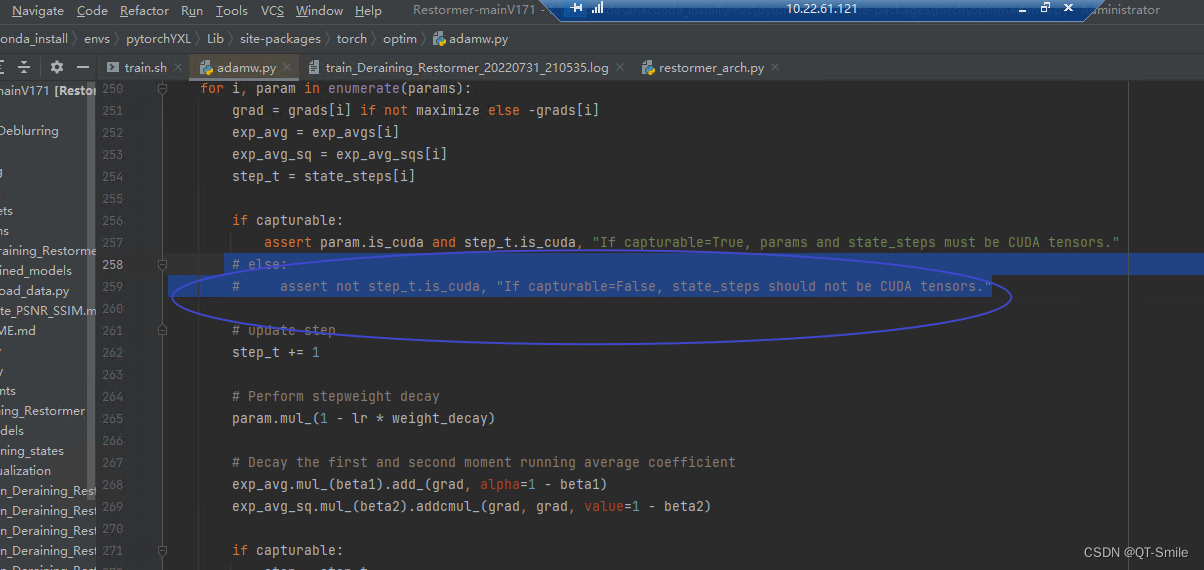

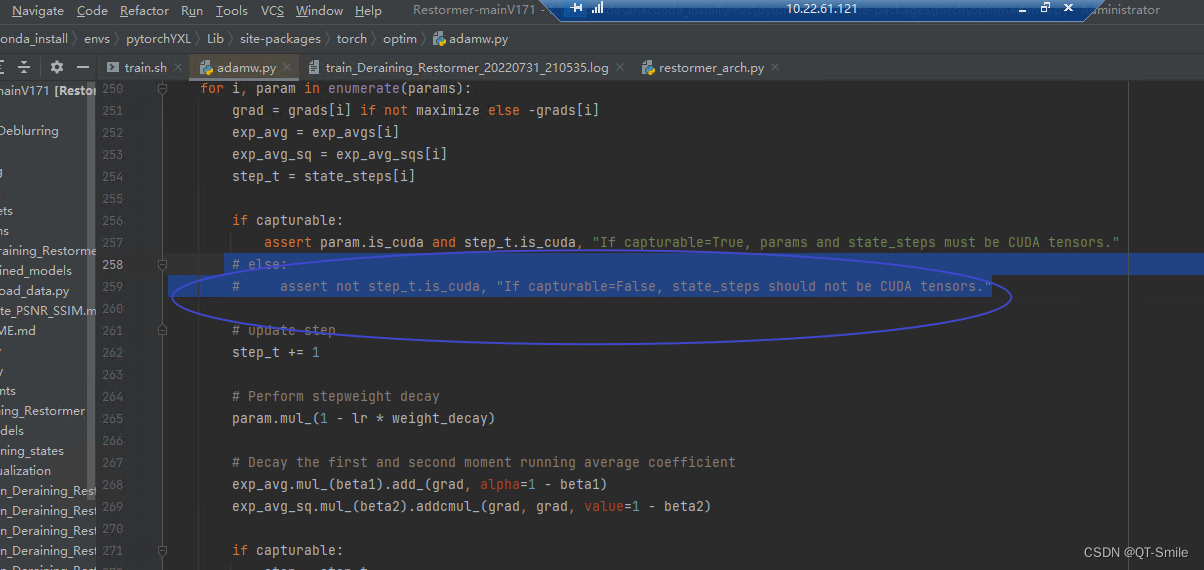

- If capturable=False, state_steps should not be CUDA tensors

- tensor.nozero(),面具,面具

- leetcode: 269. The Martian Dictionary

- 软件测试面试题:LoadRunner 分为哪三个模块?

- [230] Execute command error after connecting to Redis MISCONF Redis is configured to save RDB snapshots

- Software Testing Interview Questions: What's the Difference Between Manual Testing and Automated Testing?

- 如何用 Solidity 创建一个“Hello World”智能合约

- 软件测试面试题:测试用例通常包括那些内容?

猜你喜欢

SV class virtual method of polymorphism

2022杭电多校第三场 K题 Taxi

If capturable=False, state_steps should not be CUDA tensors

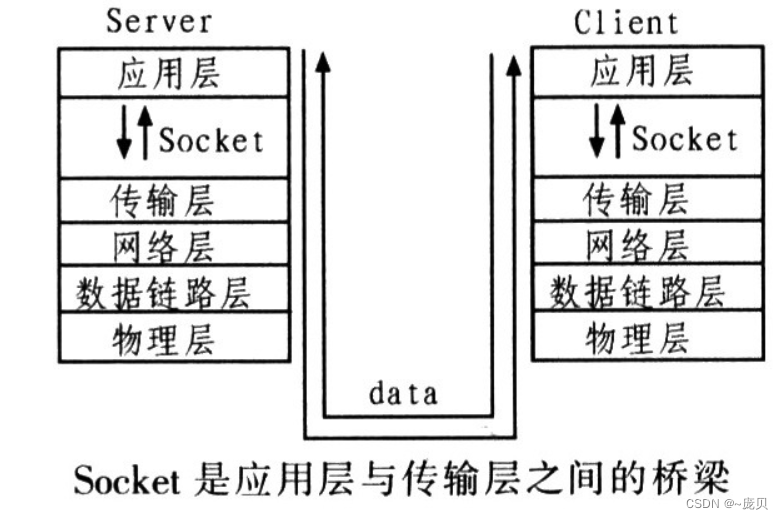

进程间通信和线程间通信

If capturable=False, state_steps should not be CUDA tensors

LiveVideoStackCon 2022 Shanghai Station opens tomorrow!

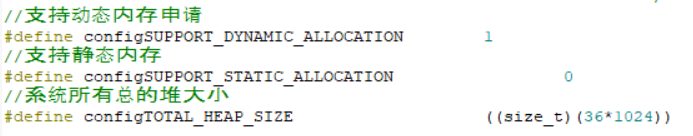

【FreeRTOS】FreeRTOS与stm32内置堆栈的占用情况

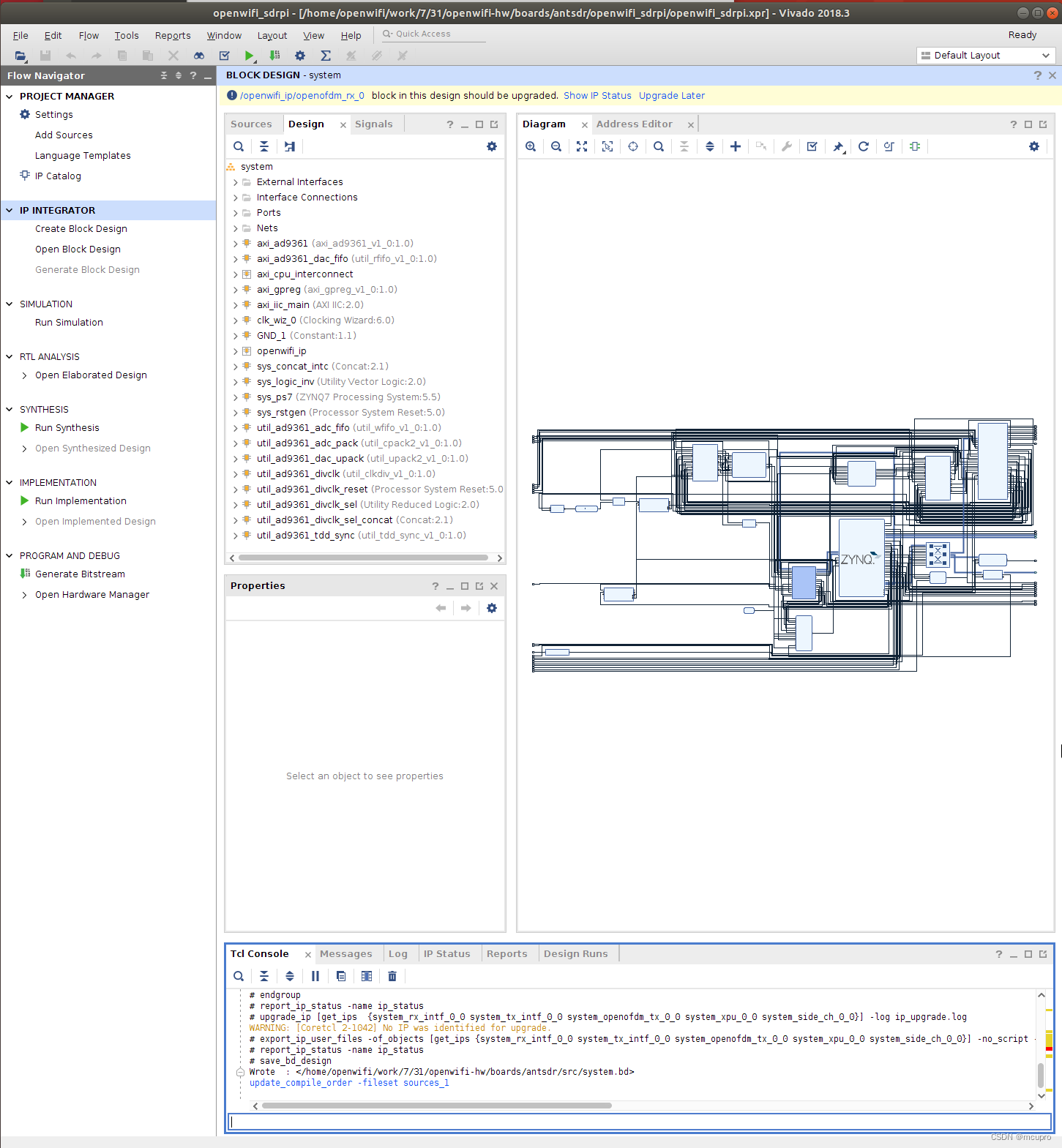

OPENWIFI实践1:下载并编译SDRPi的HDL源码

倒计时1天!8月2日—4日与你聊聊开源与就业那些事!

TinyMCE disable escape

随机推荐

DHCP的工作过程

TinyMCE disable escape

进程间通信和线程间通信

软件测试面试题:关于自动化测试工具?

About I double-checked and reviewed the About staff page, returning an industry question

BC(转)[js]js计算两个时间相差天数

could not build server_names_hash, you should increase server_names_hash_bucket_size: 32

工具类总结

MBps与Mbps区别

Bit rate vs. resolution, which one is more important?

Pytorch usage and tricks

倒计时1天!8月2日—4日与你聊聊开源与就业那些事!

C# const readonly static 关键字区别

2022 Nioke Multi-School Training Session H Question H Take the Elevator

4. PCIe 接口时序

JUC线程池(一): FutureTask使用

软件测试面试题:您如何看待软件过程改进?在您曾经工作过的企业中,是否有一些需要改进的东西呢?您期望的理想的测试人员的工作环境是怎样的?

Software Testing Interview Questions: What is Software Testing?The purpose and principle of software testing?

动态规划/背包问题总结/小结——01背包、完全背包

主库预警日志报错ORA-00270