当前位置:网站首页>verilog学习|《Verilog数字系统设计教程》夏宇闻 第三版思考题答案(第十二章)

verilog学习|《Verilog数字系统设计教程》夏宇闻 第三版思考题答案(第十二章)

2022-08-02 14:02:00 【驚蟄_】

《Verilog数字系统设计教程》夏宇闻 第三版思考题

答案合集 : Verilog学习系列 第三部分

1.举例说明状态分配对状态机电路的复杂度和速度的影响。

例12.2与12.1的状态分配不同,例12.2采用独热编码而例12.1则采用Gray编码,究竟采用哪一种编码好看看1具体情况而定。对于用FBGA实现的有限状态机建议采用独热码,因为虽然独热编码多用了两个触发器,但所用组合电路可省些,因而使用电路的速度和可靠性有显著提高,而总的单元数并无显著增加.采用独热编码后有了多余的状态,就有一些不可到达的状态,为此可以用默认项表示不可达到的状态。

2.分别说明和解释[例12.1]~[例12.4]中两种不同赋值(即非阻塞赋值“≤=”和阻塞赋值“=”)的用法,和逻辑关系等号“==”的含义。

例12.1用“<=”赋值,表示在过程块结束以后才进行赋值是并行结构。例12.4用“=”赋值,表示是立即进行赋值是顺序结构。两个例子中作用是一样的,例12.4用了多个always块,而例12.1只用到了一个 always 块,故两种赋值的方式才会不一样。逻辑关系符号“m”是表示判断的符号,用到判断信号是否为符合条件的信号,如 if(a2’b10)则表示a是否为2’b10。

3.一般情况下状态机中的状态变量是用来干什么的?是否可以把状态变量中的某些位指定为状态机的输出,直接用来控制逻辑开关?这样做有什么好处?有什么缺点?

用来表示状态机的几种状态,可以用来对不同状态进行转换,可以直接把状态变量中的某位指定为状态机的输出,直接用来控制逻辑开关。这样做可以提高输出信号的开关速度并节省电路器件。但这种方法的缺点就是开关的维持时间必须与状态机的时间一致。

4.分析[例12.1]~[例12.4]中用Verilog编写的状态机模块。经综合后产生的电路结构中,哪个属于Mealy状态机?哪个属于Moore状态机?请在认真分析及综合出来的电路结构后,给出正确的答案。

从综合后产生的电路结构,可知例12.1,例12.2都属于 Mealy 状态机而例12.3,例12.4属于Moore状态机

5.如果需要设计带流水线输出的 Mealy状态机﹐其 Verilog模块应该如何编写?请您编写一下,并通过综合器产生电路结构,分析其电路结构和时序。

Verilog 模块:

module fsm(clock, reset, a, k2, k1);

input clock, reset, a;

output k1, k2;

reg k1, k2;

reg[3:0] state;

parameter idle = 4'b1000,

start = 4'b0100,

stop = 4'b0010,

clear = 4'b0001,

[email protected](posedge clock)

if(!reset)

begin

state<=idle;

k2<=0;

k1<=0;

end

else

case(state)

idle:

if(a)

begin

state<=start;

k1<=0;

end

else

begin

state<=idle;

k2<=0;

k1<=0;

end

else

begin

state<=idle;

k2<=0;

k1<=0;

end

start:

if(!a) state<=stop;

else state<=start;

stop:

if(a)

begin

state<=clear;

k2<=1;

end

else

begin

state<=stop;

k2<=0;

k1<=0;

end

clear:

if(a)

begin

state<=idle;

k2<=0;

k1<=1;

end

else

begin

state<=clear;

k2<=0;

k1<=0;

end

default:

state<=idle;

endcase

endmodule

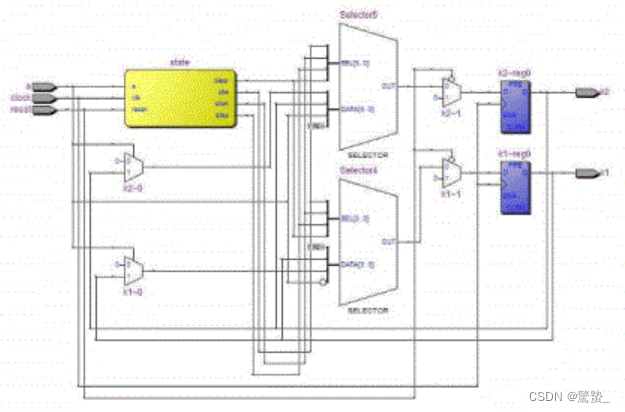

电路结构:

电路结构有数据选择器构成,输出通过寄存器输出,可构成流水线。通过仿真其时序如上图所示,各状态的转换如图,可知符合要求。

6.在状态机的测试模块中,最后面的 initial块语句有什么作用,若测试模块中没有最后的initial语句块能不能进行仿真?如果能,需要注意什么?本测试模块还有什么地方没有测试到?应该如何改进?

和其它模块一起有并行的作用,起到是仿真结束的作用。若测试模块中没有最后的 initial语句能进行仿真。需要注意仿真是各个信号要对应所测试的模块。本测试模块没有测试到当状态不属于四个状态时,将会怎样。在初始化时可以先将reset信号为高阻或xx而后再按照该测试模块进行仿真。

边栏推荐

猜你喜欢

The specific operation process of cloud GPU (Hengyuan cloud) training

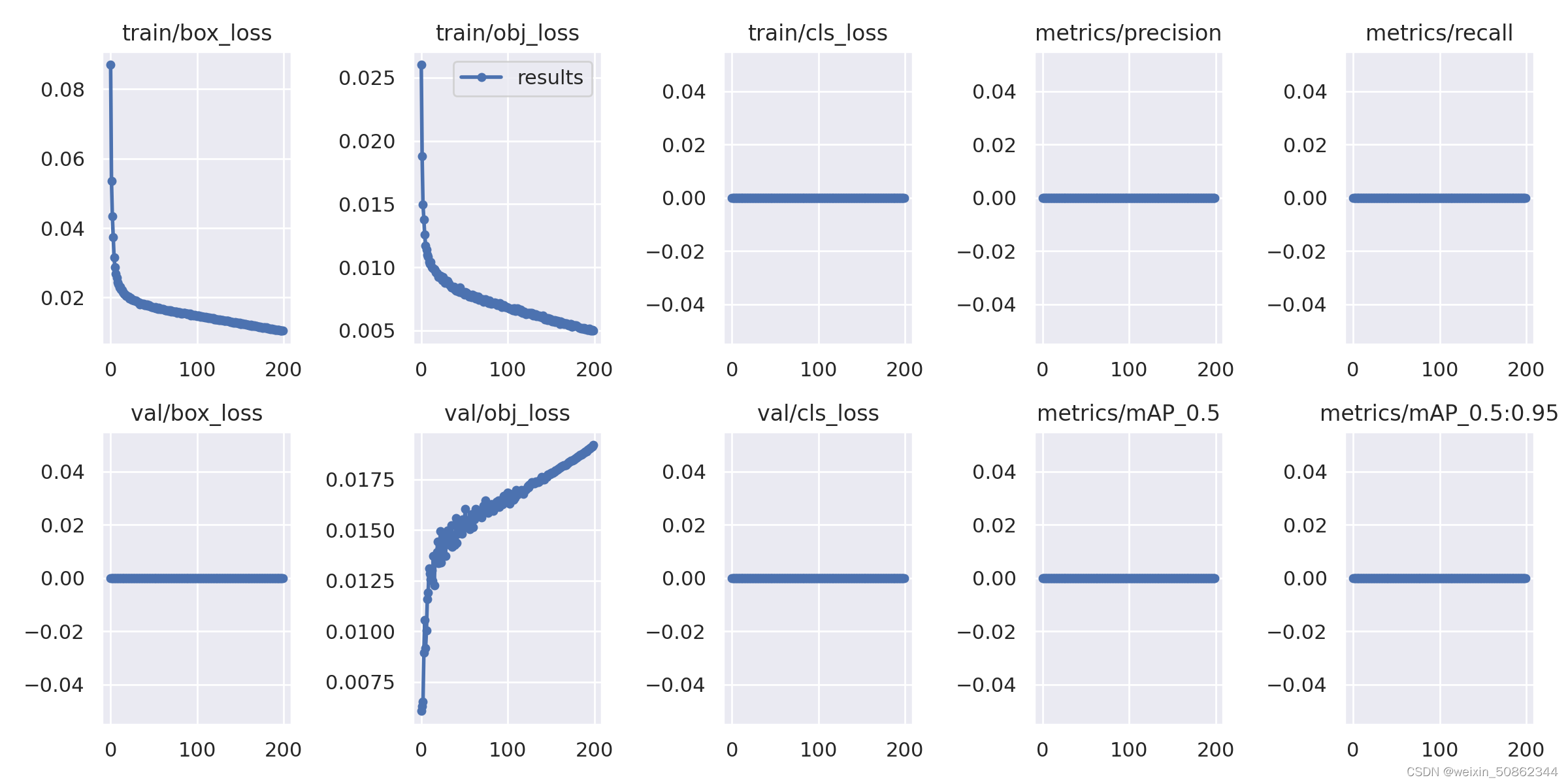

What's wrong with running yolov5 (1) p, r, map are all 0

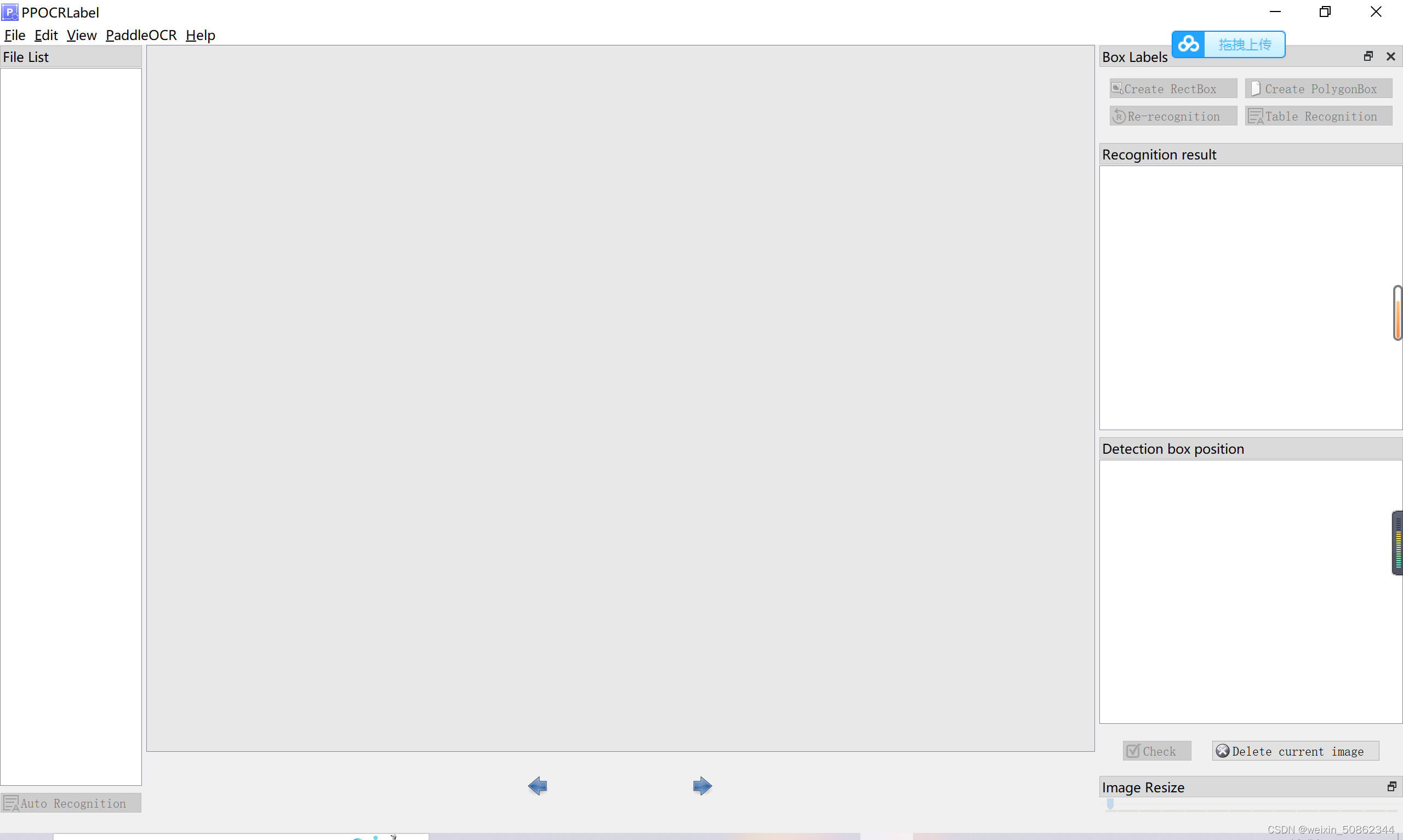

浅浅写一下PPOCRLabel的使用及体验

第十单元 前后连调

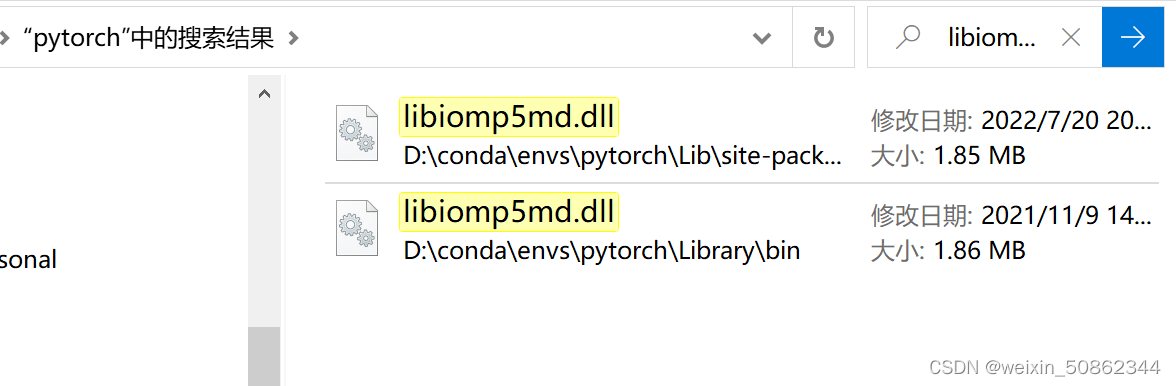

深度学习框架pytorch快速开发与实战chapter3

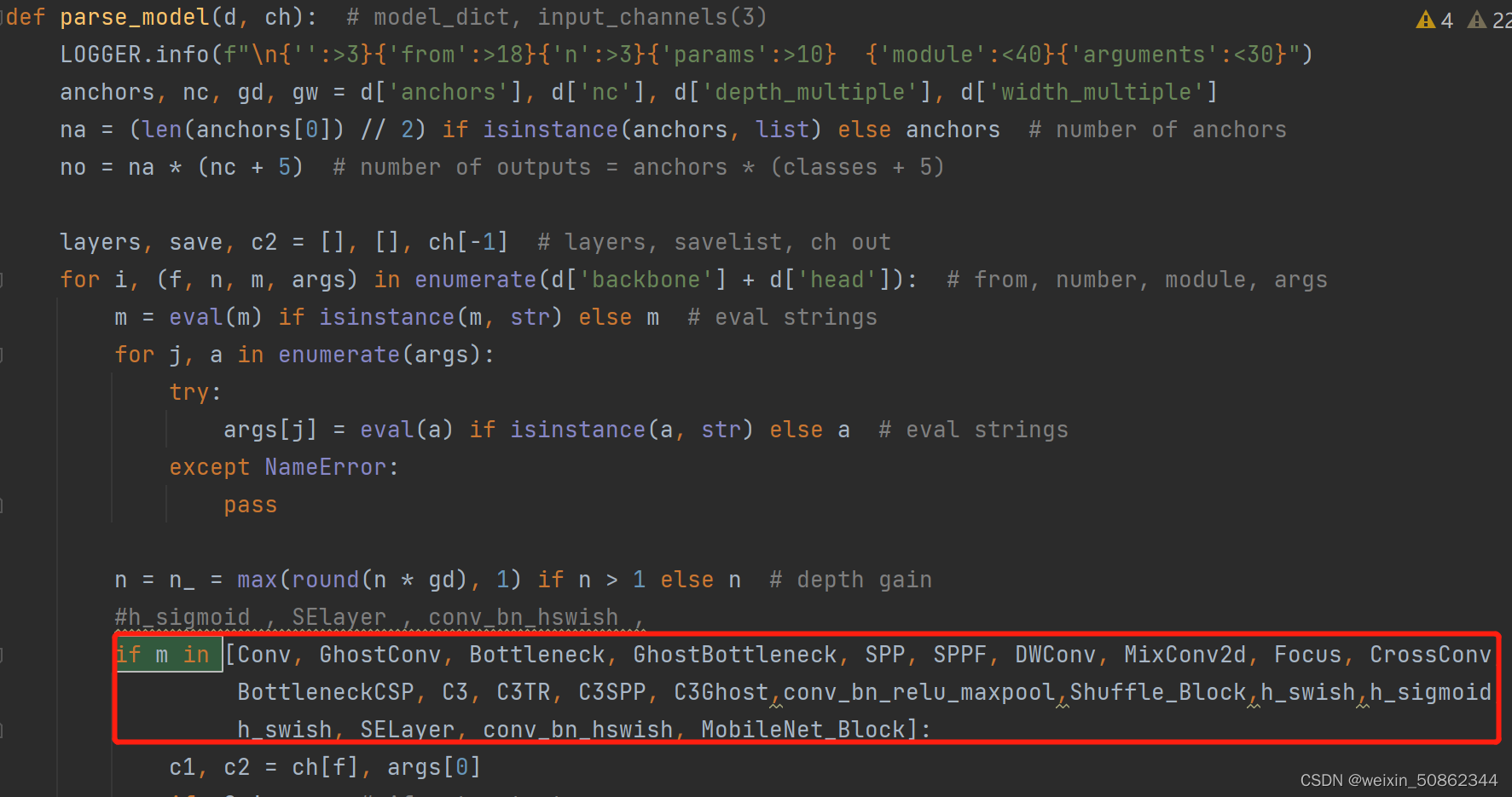

MobileNet ShuffleNet & yolov5 replace backbone

Deep learning framework pytorch rapid development and actual combat chapter4

![[ROS] (01) Create ROS workspace](/img/2a/11e5023ef6d052d98b4090d2eea017.png)

[ROS] (01) Create ROS workspace

海明校验码纠错设计原理

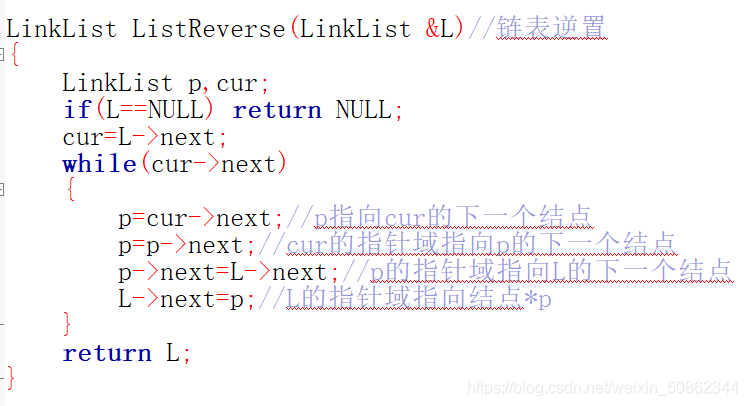

8581 Linear linked list inversion

随机推荐

The world's largest Apache open source foundation is how it works?

logback源码阅读(二)日志打印,自定义appender,encoder,pattern,converter

VMM是什么?_兮是什么意思

drf路由组件Routers

[ROS](05)ROS通信 —— 节点,Nodes & Master

Unit 5 Hold Status

[ROS] (01) Create ROS workspace

[ROS]ROS常用工具介绍(待续)

How to solve mysql service cannot start 1069

线代:已知一个特征向量快速求另外两个与之正交的特征向量

无序数组排序并得到最大间隔

MySQL数据库语法格式

Hands-on OCR (1)

第十三单元 混入视图基类

Linux:CentOS 7 安装MySQL5.7

The future of financial services will never stop, and the bull market will continue 2021-05-28

第十单元 前后连调

redis分布式锁和看门狗的实现

idea社区版下载安装教程_安装天然气管道的流程

Verilog学习 系列