当前位置:网站首页>[quick start of Digital IC Verification] 6. Quick start of questasim (taking the design and verification of full adder as an example)

[quick start of Digital IC Verification] 6. Quick start of questasim (taking the design and verification of full adder as an example)

2022-07-05 20:09:00 【luoganttcc】

Reading guide : The author has the honor to be a pioneer in the field of electronic information in China “ University of electronic technology ” During postgraduate study , Touch the cutting edge Numbers IC Verification knowledge , I heard something like Huawei Hisilicon 、 Tsinghua purple light 、 MediaTek technology And other top IC related enterprises in the industry , Pairs of numbers IC Verify some knowledge accumulation and learning experience . Want to get started for help IC Verified friends , After one or two thoughts , This column is specially opened , In order to spend the shortest time , Take the least detours , Most learned IC Verify technical knowledge .

List of articles

- Preface

- One 、QuestaSim install

- Two 、QuestaSim Use

- Reference resources

Preface

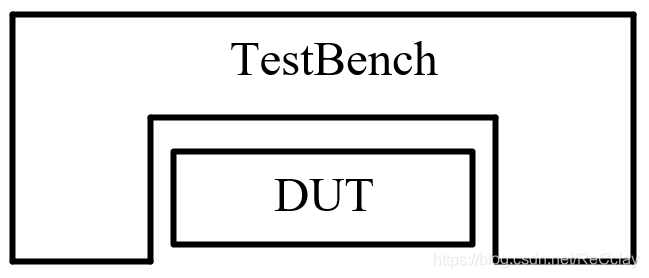

QuestaSim yes Mentor Upgraded version of the company ModelSim, Industry is benchmarked EDA The manufacturer's tools include :Cadence The company's NC-Sim,Synopsys The company's VCS. The most common tool for chip verification in industry is VCS, It has incomparable advantages over the other two tools , Especially in the scene of large-scale integrated circuits . however QuestaSim a VCS Of License It's cheaper , At the same time, it consumes less resources , It is generally used in the development of small-scale integrated circuits ! Such as FPGA Verification in progress , The common one is QuestaSim .FPGA The verification scenario of is relatively simple , It's usually used Verilog Directly built TestBench (flatten, No hierarchy), This verification scenario is often called VTB. and ASIC It is necessary to use SystemVerilog as well as UVM Methodology , To build a hierarchical verification environment , This verification scenario is often called SVTB.

One 、QuestaSim install

1.1、Windows Lower installation

- The installation package and installation guide can be found at < here > obtain …( Extraction code :s7nh)

1.2、Linux Lower installation

- Installation is difficult , You can find bloggers to share the built virtual machine …

Two 、QuestaSim Use

notes : Whether in the Linux Next or windows Next ,QuestaSim The basic operation methods are the same !

This section will begin with a Full adder demo, To achieve Questasim Quick to use .

The overall process can be summarized as :

- Build a library library

- Building engineering project

- ( To write ) Add simulation file

- compile compile

- Simulation simulate

- function run

2.1、QuestaSim start-up

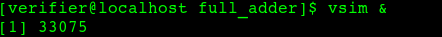

- Linux Next , stay Terminal Input in

vsim &Can be in backstage start-up QuestaSim.

notes :

&Means running in the background vsim command , Does not occupy the currentterminal.

- windows Next , Double click the start icon directly to start !

2.x、 Closure of works

By the way , Every time open Questasim The last project will be retained by default , How to turn it off ?

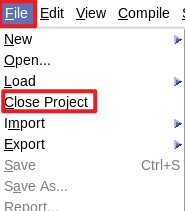

- In turn, click :

File -> Close Project

Select... In the pop-up window

Yes

At the same time

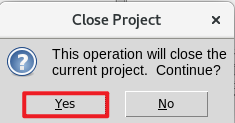

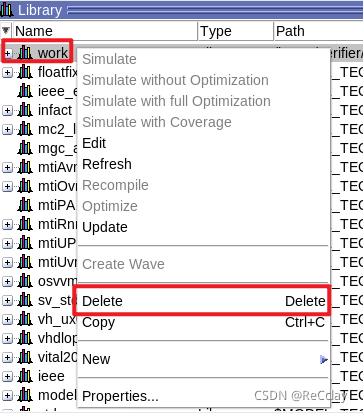

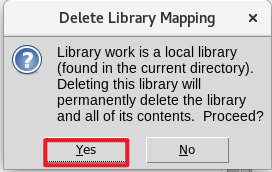

LibraryFind... In the columnwork, Right click selectionDeleteTo delete !

Select in the pop-up dialog box

Yes

2.2、 New project (GUI The way )

2.2.1、 establish Library

Each project has a corresponding library ,Verilog or SystemVerilog Wait for the source file to compile , Will compile The results of are stored in the corresponding library , Then we can get the data from the library during the simulation call The result of compilation .

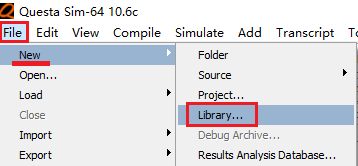

How to build a library :File -> New -> Library

Generally, the name of the library defaults to work that will do

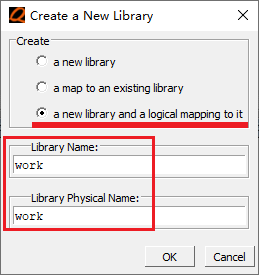

Then on the main interface Library You can see the newly created work library , Some dependent libraries of subsequent running simulation will be placed in this , Other libraries are the default libraries for tool operation , Don't delve into .

2.2.2、 Building engineering

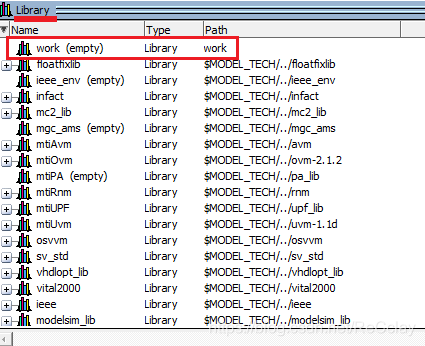

The establishment method of the project :File -> New -> Project

Project NameYou can do whatever you want , Here I set it tofull_adderProjectLocationYou can do whatever you want , Here I set it toC:/Users/CLAY/Desktop, It's my windows desktop .Default Library NameTo be established with the previous sectionLibrarynameworkAgreement , Or we won't find itLibrary!

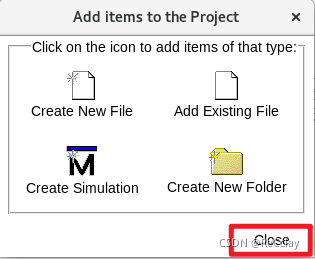

And then it pops up Add items to the project, Let's choose Close, Back DUT and TB Add after the source file is written !

2.2.3、 To write DUT and TestBench

DUT:full_adder.v

module full_adder( input wire a_in, input wire b_in, input wire c_in, output wire sum_out, output wire c_out );// Method 1 : Gate level description <span class="token punctuation">(</span> Truth table and logical expression description <span class="token punctuation">)</span> assign sum_out <span class="token operator">=</span> a_in ^ b_in ^ c_in<span class="token punctuation">;</span> assign c_out <span class="token operator">=</span> <span class="token punctuation">(</span>a_in <span class="token operator">&</span> b_in<span class="token punctuation">)</span> <span class="token operator">|</span> <span class="token punctuation">(</span>b_in <span class="token operator">&</span> c_in<span class="token punctuation">)</span> <span class="token operator">|</span> <span class="token punctuation">(</span>a_in <span class="token operator">&</span> c_in<span class="token punctuation">)</span><span class="token punctuation">;</span> /* // Method 2 :RTL Level description <span class="token punctuation">(</span>assign Continuous assignment statement c_out and sum_out yes wire type <span class="token punctuation">)</span> assign <span class="token punctuation">{<!-- --></span>c_out, sum_out<span class="token punctuation">}</span> <span class="token operator">=</span> a_in + b_in + c_in<span class="token punctuation">;</span>*/ /* // Method 3 :RTL Level description <span class="token punctuation">(</span>always block c_out and sum_out yes reg type <span class="token punctuation">)</span> reg c_o, sum_o<span class="token punctuation">;</span> always @<span class="token punctuation">(</span><span class="token punctuation">)</span> begin <span class="token punctuation">{<!-- --></span>c_o, sum_o<span class="token punctuation">}</span> <span class="token operator">=</span> a_in + b_in + c_in<span class="token punctuation">;</span> end assign <span class="token punctuation">{<!-- --></span>c_out, sum_out<span class="token punctuation">}</span> <span class="token operator">=</span> <span class="token punctuation">{<!-- --></span>c_o, sum_o<span class="token punctuation">}</span><span class="token punctuation">;</span>*/

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

TestBench:full_adder_tb.v

module full_adder_tb; reg ain, bin, cin; wire sumout, cout;//Task1 Example full adder module full_adder u_full_adder<span class="token punctuation">(</span> .a_in <span class="token punctuation">(</span>ain <span class="token punctuation">)</span>, .b_in <span class="token punctuation">(</span>bin <span class="token punctuation">)</span>, .c_in <span class="token punctuation">(</span>cin <span class="token punctuation">)</span>, .sum_out<span class="token punctuation">(</span>sumout<span class="token punctuation">)</span>, .c_out <span class="token punctuation">(</span>cout <span class="token punctuation">)</span> <span class="token punctuation">)</span><span class="token punctuation">;</span> //Task2 produce clock/Reset The signal parameter CLK_PERIOD <span class="token operator">=</span> <span class="token number">20</span><span class="token punctuation">;</span> reg clk, reset_n<span class="token punctuation">;</span> initial begin clk <span class="token operator">=</span> <span class="token number">0</span><span class="token punctuation">;</span> forever begin <span class="token comment">#(CLK_PERIOD/2)clk = ~clk;</span> end end initial begin reset_n <span class="token operator">=</span> <span class="token number">0</span><span class="token punctuation">;</span> <span class="token comment">#100</span> reset_n <span class="token operator">=</span> <span class="token number">1</span><span class="token punctuation">;</span> end //Task3 Drive the simulation to capture the corresponding initial begin <span class="token comment">#110 ain = 0; bin = 0; cin = 0; //00</span> <span class="token comment">#20 ain = 0; bin = 1; cin = 0; //01</span> <span class="token comment">#20 ain = 1; bin = 0; cin = 0; //01</span> <span class="token comment">#20 ain = 1; bin = 1; cin = 0; //10</span> <span class="token comment">#20 ain = 0; bin = 0; cin = 1; //01</span> <span class="token comment">#20 ain = 0; bin = 1; cin = 1; //10</span> <span class="token comment">#20 ain = 1; bin = 0; cin = 1; //10</span> <span class="token comment">#20 ain = 1; bin = 1; cin = 1; //11</span> <span class="token comment">#50 $finish;</span> end //Task4 Examination result [email protected]<span class="token punctuation">(</span>posedge clk<span class="token punctuation">)</span>begin if<span class="token punctuation">(</span><span class="token operator">!</span>reset_n<span class="token punctuation">)</span> begin <span class="token variable">$display</span><span class="token punctuation">(</span><span class="token string">"%t:%m:resetting ..."</span>, <span class="token variable">$time</span><span class="token punctuation">)</span><span class="token punctuation">;</span>//counter <span class="token number">5</span> clock end <span class="token keyword">else</span> begin <span class="token variable">$display</span><span class="token punctuation">(</span><span class="token string">"%t:%m:resetting finish!"</span>, <span class="token variable">$time</span><span class="token punctuation">)</span><span class="token punctuation">;</span>//the 6th clock end end initial begin <span class="token comment">#115 if({cout,sumout} != 2'b00) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> <span class="token comment">#20 if({cout,sumout} != 2'b01) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> <span class="token comment">#20 if({cout,sumout} != 2'b01) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> <span class="token comment">#20 if({cout,sumout} != 2'b10) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> <span class="token comment">#20 if({cout,sumout} != 2'b01) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> <span class="token comment">#20 if({cout,sumout} != 2'b10) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> <span class="token comment">#20 if({cout,sumout} != 2'b10) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> <span class="token comment">#20 if({cout,sumout} != 2'b11) $display("Error:{cout,sumout}=%b,ain=%b,bin=%b,cin=%b",{cout,sumout},ain,bin,cin);</span> end //Task5 //initial begin // <span class="token variable">$vcdpluson</span><span class="token punctuation">;</span> //end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

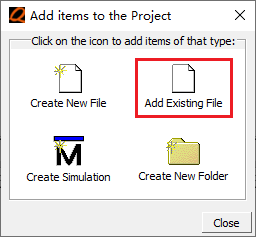

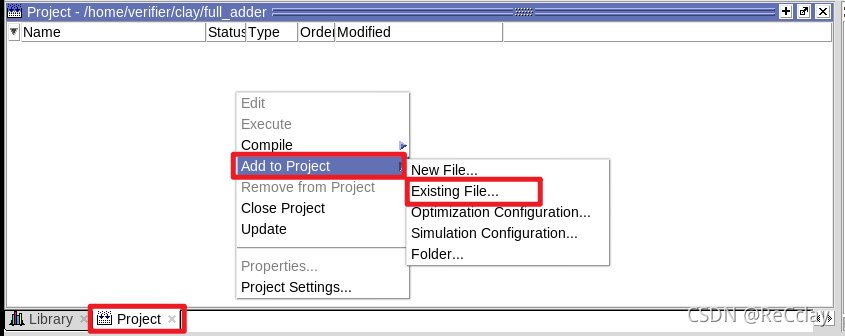

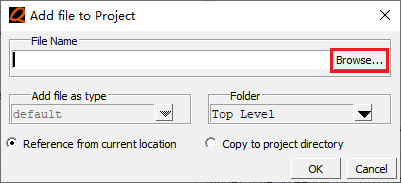

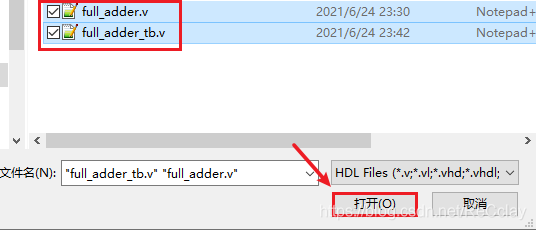

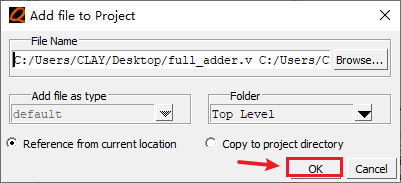

2.2.4、 Add files

Usually our code is in GVIM And other text editing tools , Instead of Questasim Written in , It will be written in Questasim in Add Existing File.

Or in the Project In the bar , Right click the blank space and select Add to Project -> Existing File...

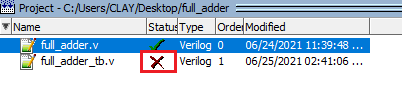

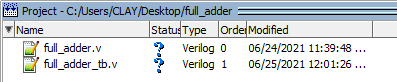

When I'm done , The interface is as follows

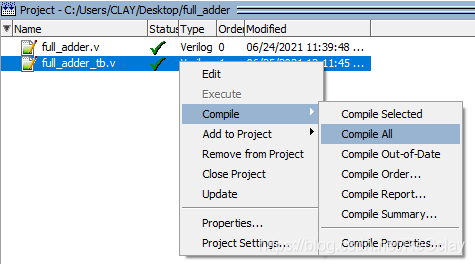

2.2.5、 Compile the file

Select any of the above files , then : Right click -> Compile -> Compile All

If there is no mistake , Above picture Status The column will show √

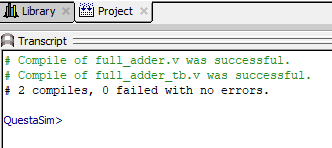

meanwhile , Under the Transcript There will be a prompt message of successful compilation in !

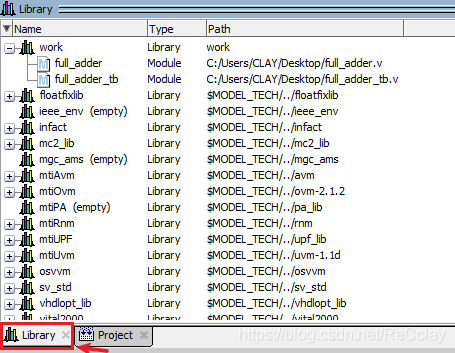

After successful compilation, you can work Corresponding Library See full_adder and full_adder_tb these two items. , As shown in the figure below

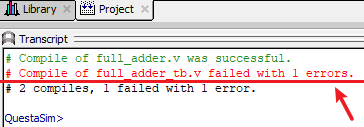

notes : If there is a syntax error in the file , It will prompt the compilation failure , The interface is as follows :

Double click the error message in the above figure , You can view the specific error content , Then locate the location where the error occurred .

You can see from the above picture that , The error occurs whenfull_adder_tb.vOf 12 Near the line , The reason for the mistake is)An extra one is added,, Open the source file and modify it , recompile , You can eliminate the error !

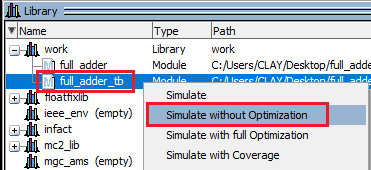

2.2.6、 Simulation

stay Library Tab TestBench file full_adder_tb, Then right-click , choice Simulate without Optimization.

notes :Questasim Logic with relatively small amount of computation , So

Simulate without OptimizationandSimulate with full OptimizationThe difference is not great !in addition , Tested on Linux Click on

Simulate without OptimizationError prompt will appear , But clickSimulateThis error will not occur .

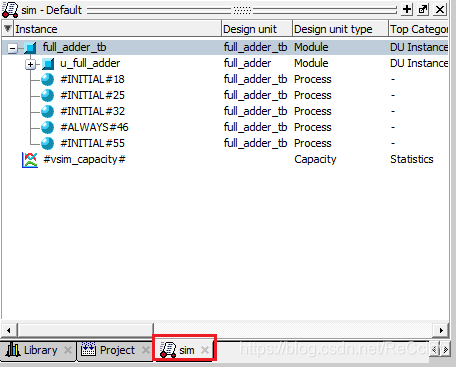

Then you can see sim tab , Run the simulation hierarchy Show it !

2.2.7、 Add the signal :TestBench Driving and sampling

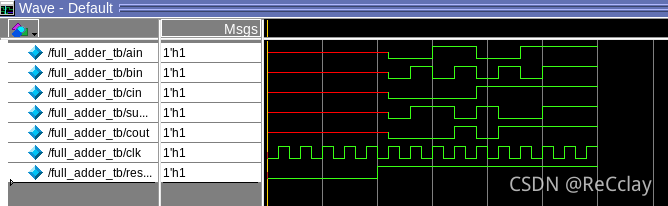

For simple simulation, I will look at the waveform , But the actual normal process is TestBench Write incentives well , And then do automation Comparison of , Not just through the waveform check Corresponding DUT Whether the behavior is right . wave form check Generally, when the automatic comparison fails , Used when debugging , To check is DUT The problem is TestBench problem .

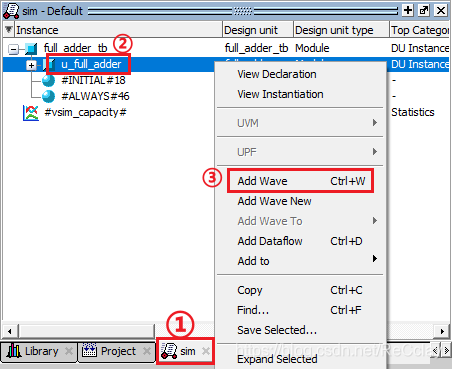

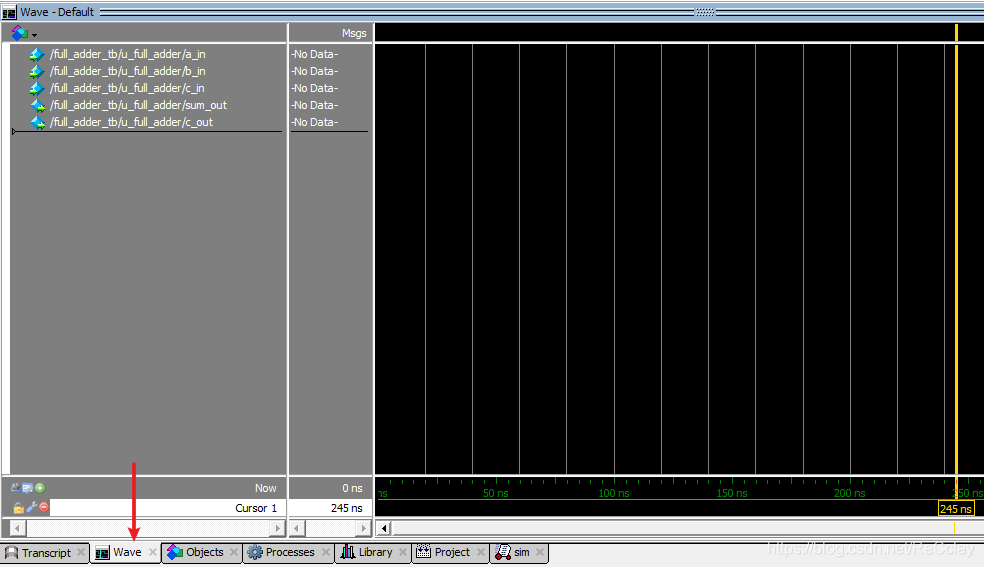

stay sim Tab to find u_full_adder, Then right-click to choose Add wave Or shortcut key ctrl+w Add waveform to wave Interface !

2.2.8、 Set simulation time

There are two ways to set the simulation time :

- The first is in

TestBenchSet in - The second is in the simulation tool

QestasimSet in

Set the simulation time in the simulation tool , There are two ways :①、 From the command line ;②、 Through the graphic interface .

- ①、 adopt Command line How to operate , Just in

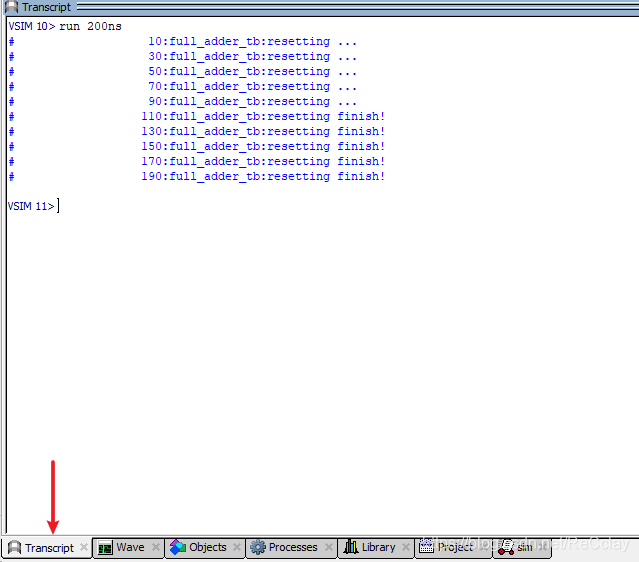

TranscriptEnter the corresponding command in . If you want to run here 200ns, Inputrun 200nsthat will do :

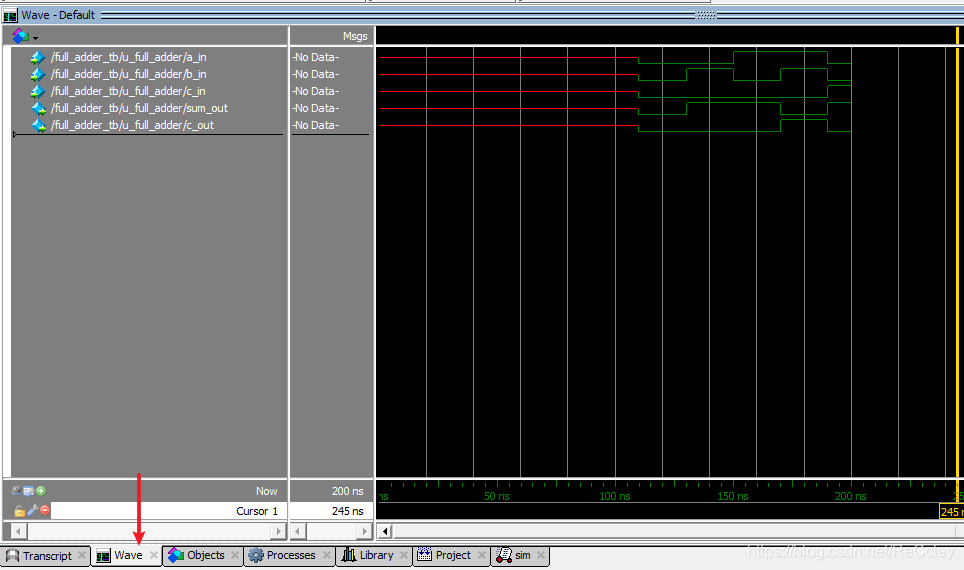

Corresponding wave The interface will also display the corresponding waveform :

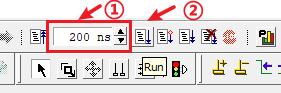

- ②、 If you want to set the simulation time in the simulation tool through the graphical interface , You can set the simulation time in the toolbar

200ns, And then clickrunthat will do !

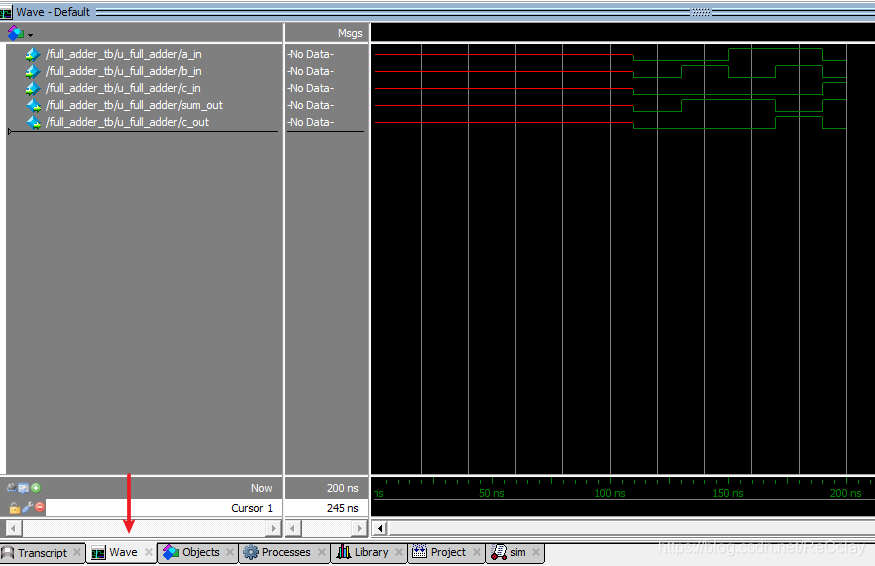

Corresponding wave The interface will also display the corresponding waveform :

2.2.9、 Verify a full adder

- function

- Truth table

- verification

- Functional integrity

- Exhaustive method

- Code coverage

- experiment

- compile

- Simulation

- Look at the waveform

The full adder is relatively simple , Directly verify all Pattern that will do !

| a_in | b_in | c_in | c_out | sum_out |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

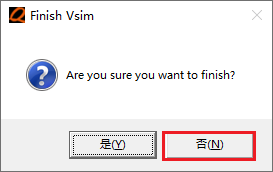

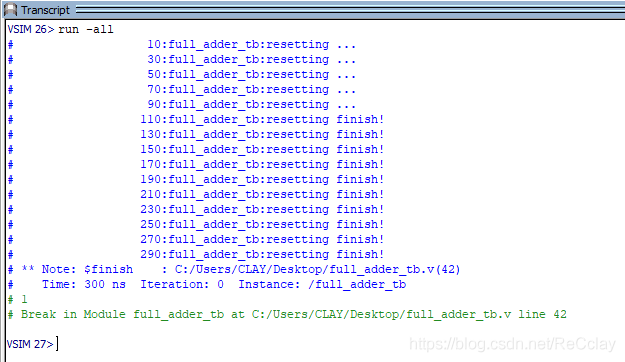

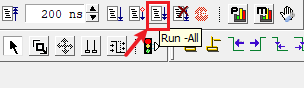

stay Transcprit Input in run -all, Because the command will encounter $finish stop it , The dialog box of whether to exit will pop up , Choose here “ no ”!

stay Transcprit in , Check to see if there is TB Error printing information in , If it is not stated that the verification is completed !

2.3、 New project ( Command line mode )

notes : Command line mode is compared with graphical interface mode , Smaller footprint , Run faster !

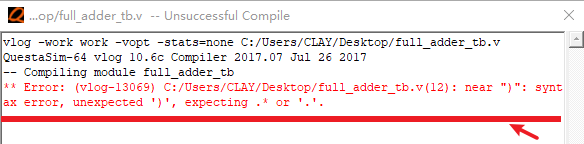

2.3.1、 establish 、 compile 、 Operation engineering

- New filename

Makefile, Add the following :- If Makefile The file name is not

Makefile, Then you need to add-fParameters , And then there was Makefile file name !

- If Makefile The file name is not

all: create_lib compile simulate

create_lib:

vlib work

compile:

vlog -l com.log full_adder.v full_adder_tb.v

simulate:

vsim -l sim.log -c -voptargs=+acc work.full_adder_tb -do “log -r *;run -all;quit -f”

clean:

rm -rf work mti_lib transcript modelsim.ini *.log vsim.wlf

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- contrast GUI To create a project ,Transcript The command of the window is as follows :

vlib work

vlog -work work -vopt -stats=none full_adder.v full_adder_tb.v

vsim -voptargs=+acc work.full_adder_tb -c -do "run -all;quit -f"

- 1

- 2

- 3

- 4

You can see our new Makefile Content and Transcript Window commands are almost the same . In fact, it must be so , We just put these commands together to run !

Questasim The meaning of some command parameters :

-c:command Pattern , Don't start the GUI-l: Store the log in the following file-do "xxx"perform xxx commandlog -r *: Generate waveform file-work work: Appoint work Directory name is work-vopt:simulate full optimization-novopt:simulate without optimization-voptargs=+acc:simulate

In development , It's usually log Problems arise , To see the waveform ! meanwhile , In order to speed up work efficiency , Usually a terminal changes its code , A terminal running simulation , It is very convenient !

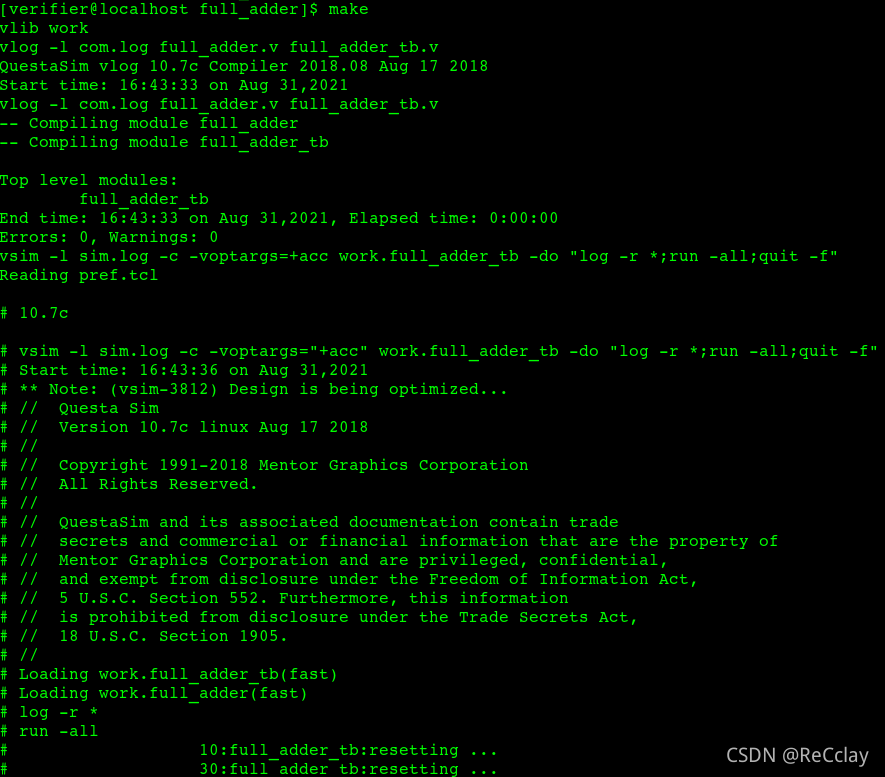

Input... At the terminal make command , You can run the Makefile Script files :

notes : If Makefile Your name is not

Makefile, If soMakefile_text, Then run the Makefile You should entermake -f Makefile_text

All log information is as follows :

[[email protected] full_adder]$ make

vlib work

vlog -l com.log full_adder.v full_adder_tb.v

QuestaSim vlog 10.7c Compiler 2018.08 Aug 17 2018

Start time: 16:43:33 on Aug 31,2021

vlog -l com.log full_adder.v full_adder_tb.v

-- Compiling module full_adder

-- Compiling module full_adder_tb

Top level modules:

full_adder_tb

End time: 16:43:33 on Aug 31,2021, Elapsed time: 0:00:00

Errors: 0, Warnings: 0

vsim -l sim.log -c -voptargs=+acc work.full_adder_tb -do “log -r *;run -all;quit -f”

Reading pref.tcl

# 10.7c

# vsim -l sim.log -c -voptargs=“+acc” work.full_adder_tb -do “log -r *;run -all;quit -f”

# Start time: 16:43:36 on Aug 31,2021

# ** Note: (vsim-3812) Design is being optimized…

# // Questa Sim

# // Version 10.7c linux Aug 17 2018

# //

# // Copyright 1991-2018 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading work.full_adder_tb(fast)

# Loading work.full_adder(fast)

# log -r *

# run -all

# 10:full_adder_tb:resetting …

# 30:full_adder_tb:resetting …

# 50:full_adder_tb:resetting …

# 70:full_adder_tb:resetting …

# 90:full_adder_tb:resetting …

# 110:full_adder_tb:resetting finish!

# 130:full_adder_tb:resetting finish!

# 150:full_adder_tb:resetting finish!

# 170:full_adder_tb:resetting finish!

# 190:full_adder_tb:resetting finish!

# 210:full_adder_tb:resetting finish!

# 230:full_adder_tb:resetting finish!

# 250:full_adder_tb:resetting finish!

# 270:full_adder_tb:resetting finish!

# 290:full_adder_tb:resetting finish!

# ** Note: KaTeX parse error: Expected 'EOF', got '#' at position 68: …token comment">#̲ Time: 300 n…ls

com.log full_adder_tb.v full_adder.v Makefile sim.log vsim.wlf work

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

notes : About Makefile Review some small knowledge points , Refer to the figure below :

It can be seen that , adopt Makefile Script can create a project 、 Load the file 、 Compiler Engineering , Running the project and other steps Together with , The operation is more efficient and convenient !

2.3.2、 Check the waveform

notes : The waveform file is just terminal Print log Only when there is something wrong will I go to see !

2.3.2.1、 Method 1 : adopt vsim.wlf The file to view

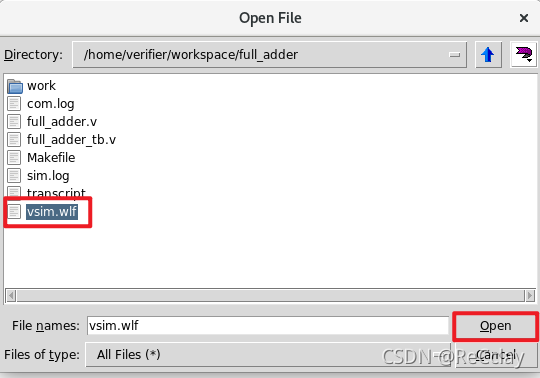

terminal Medium log When something goes wrong , Input... At the terminal vsim & start-up Questasim, As shown in the figure below :

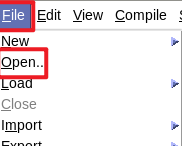

Then click File -> Open, As shown in the figure below :

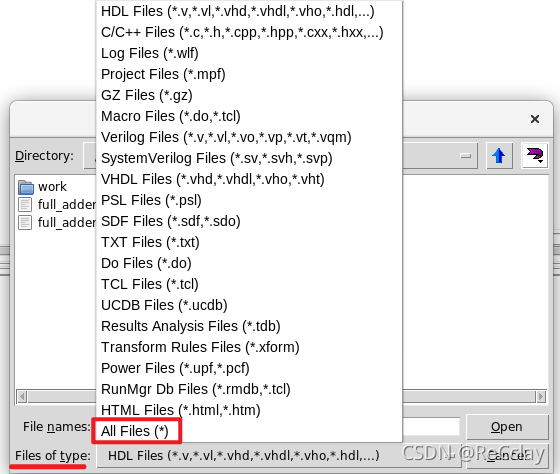

And then again Files of type Choose from All Files(*), Then choose vsim.wlf Open the can !

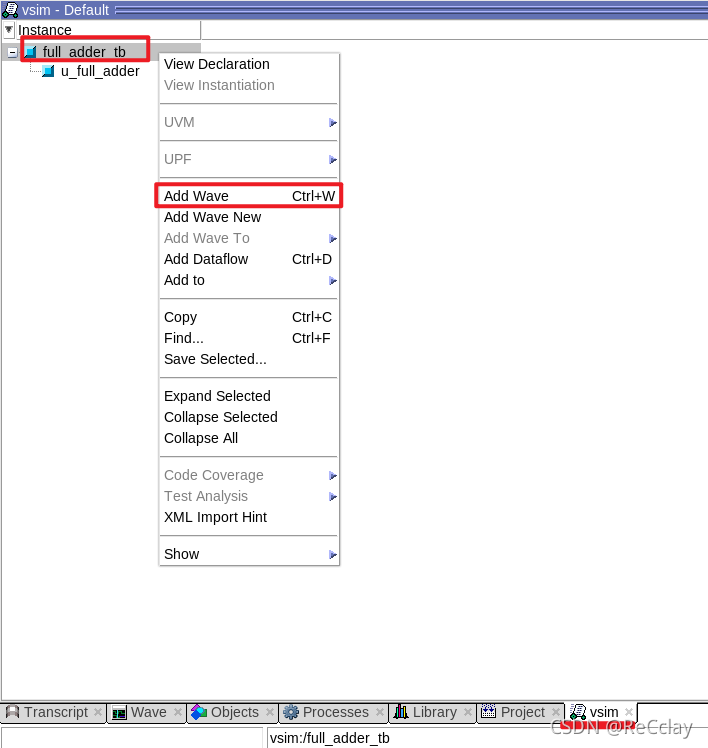

And then vsim Right click in the column full_adder_tb, choice Add Wave,( You can also click full_adder_tb Then press the shortcut key ctrl+w) You can add waveforms to Wave In the bar .

2.3.2.2、 Method 2 : modify Makefile

all: create_lib compile simulate

create_lib:

vlib work

compile:

vlog -l com.log full_adder.v full_adder_tb.v

simulate:

#vsim -l sim.log -c -voptargs=+acc work.full_adder_tb -do “log -r ;run -all;quit -f"

vsim -l sim.log -voptargs=+acc work.full_adder_tb -do "add wave -position insertpoint sim:/full_adder_tb/;log -r *;run -all”

clean:

rm -rf work mti_lib transcript modelsim.ini *.log vsim.wlf

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- Mainly

simulateOur dependence has changed : Cancel-cThat is, do not use command line mode , Cancelquit -fThat is, no forced exit , increaseadd wave -position insertpoint sim:/full_adder_tb/*Add tb Waveform signal .

After modification , Run at terminal make command , Can be in Questasim Medium Wave Column to view the waveform !

2.3.3、 Help document

There are two ways to view help documents , One is to view help documents through the installation directory , The other is through the command line help Command to view help documentation !

But whatever it is , Here's the thing to remember :EDA Reference books are for reference , Not for reading from beginning to end !

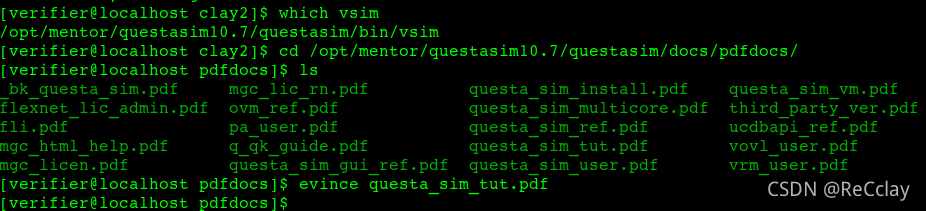

2.3.3.1、 Method 1 : View help documents through the installation directory

- have access to

which vsimOrder to find Questasim Installation position of , Let's say mine is/opt/mentor/questasim10.7/questasim/bin/vsim - And then into

/opt/mentor/questasim10.7/questasim/docs/pdfdocs/You can view all the help documents - Use

evince xxxYou can quickly open a document

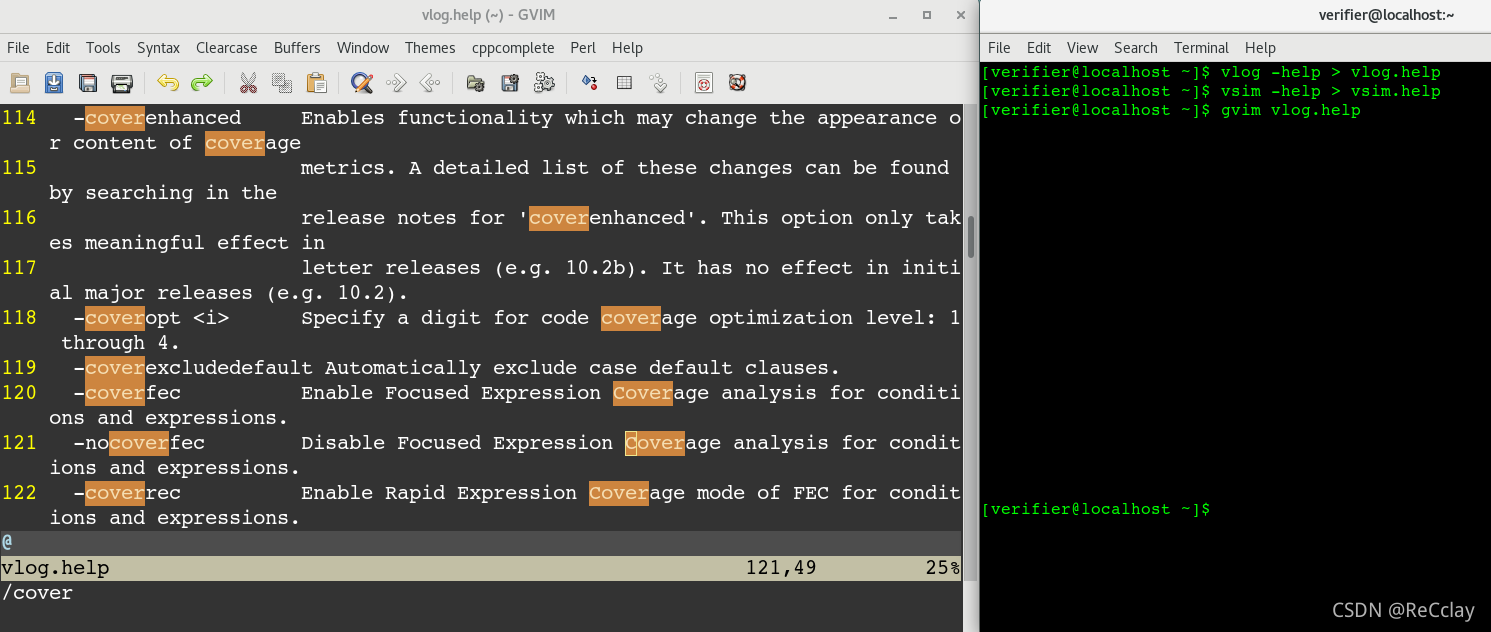

2.3.3.2、 Method 2 : From the command line help Command to view help documentation

The command line type the following command , Redirect help Help document :

vlog -help > vlog.helpvsim -help > vsim.help

If you want to see the meaning of compilation or simulation options , Enter the following command :

gvim vlog.helpopen help Help document/coverSearch keywords cover

attach :QuestaSim Common operations

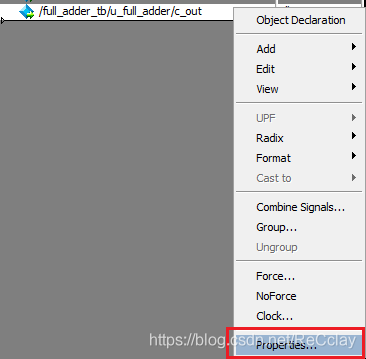

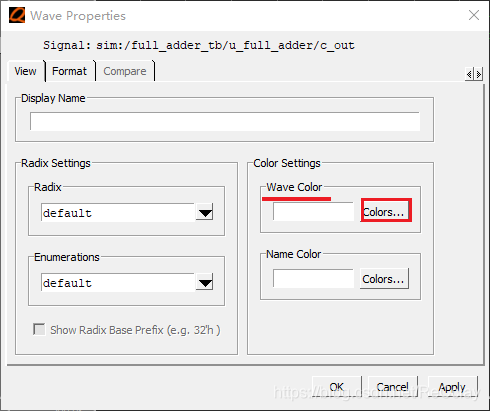

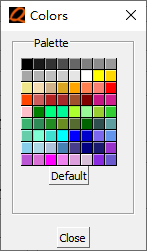

Set the waveform color

Right click the signal you want to set , And then choose Properties

choice Wave Color Under the Colors...

Set the desired waveform color in the pop-up window

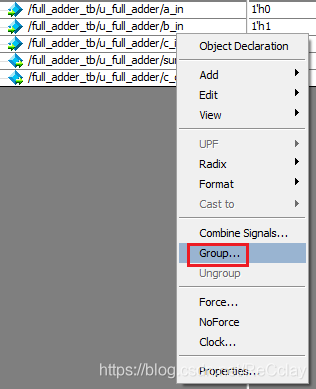

Waveform grouping Group

Method 1 : Manual grouping

Hold down ctrl+ Left mouse button , Select the waveform signals you want to divide into a group ( Or by ctrl+A Select all waveforms ), Then right-click to choose Group

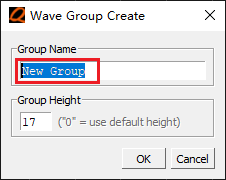

Then set the desired group name !

Method 2 : Shortcut key grouping

Hold down ctrl+ Left mouse button , Select the waveform signals you want to divide into a group ( Or by ctrl+a Select all waveforms ), Then press the shortcut key ctrl+g Realize quick grouping !

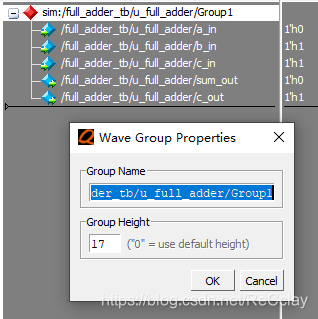

After grouping , Want to change the group name again , Double click the group name to pop up the following dialog box , Can be changed .

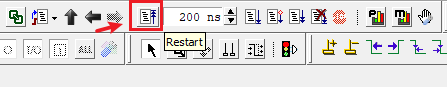

Clear the waveform Restart

Clear all waveforms that have been displayed in the waveform window

Run all Run -All

Run -All Automatically run into the code $finish Stop after statement .

notes :

run xx nsafter , At this timeRun -AllIf the simulator finds that it is not finished , Will continue to run , If it is found that the operation has been completed , At this time, the simulator will not continue to run !

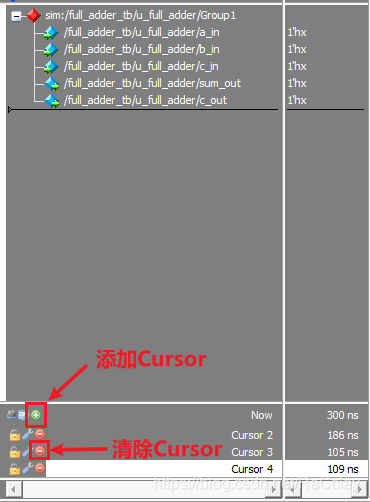

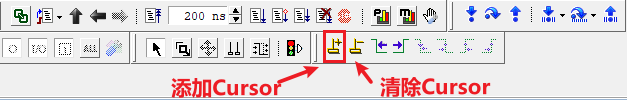

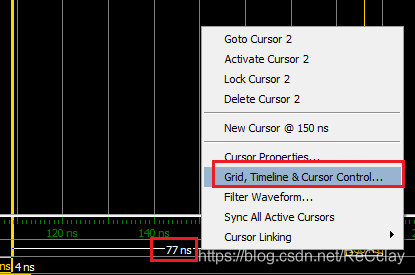

add to / eliminate Cursor

Method 1 :

Method 2 :

One caveat , eliminate Cursor Before , You need to select the one you want to delete first Cursor!

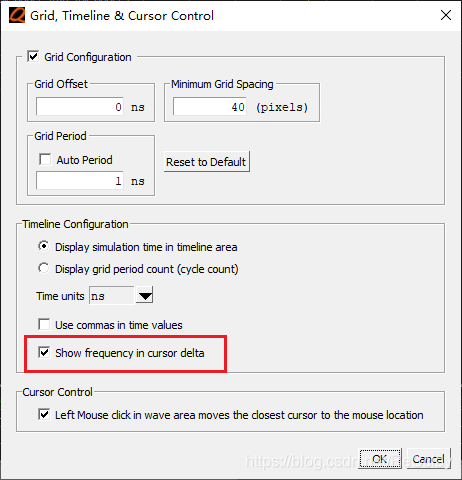

Set up Cursor The unit displayed between is frequency

stay Cursor Between the display , Right click selection Grid,Timeline & Cursor Control...

Check Show freqency in Cursor delta

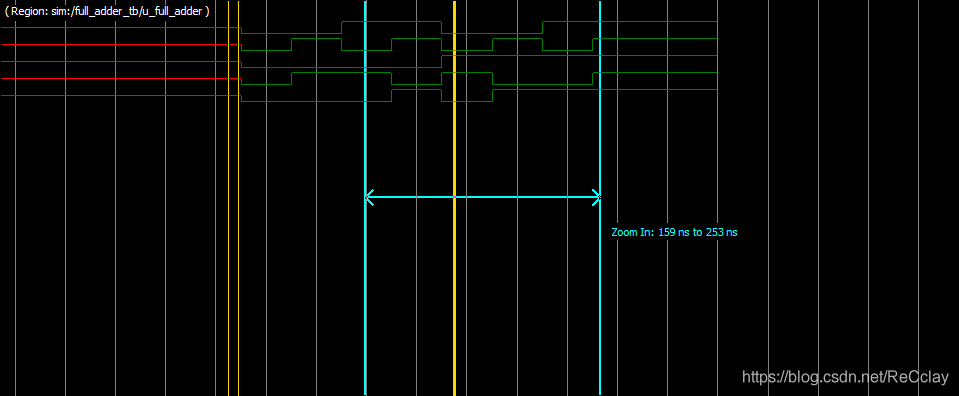

Waveform local method

Method 1 :

Hold down ctrl key , Then hold down the left mouse button , Drag to the right .

Method 2 :

ctrl+ Mouse wheel

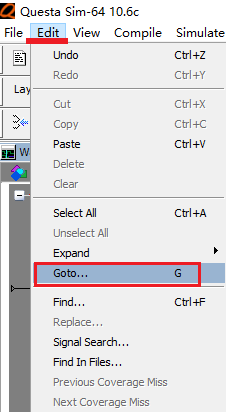

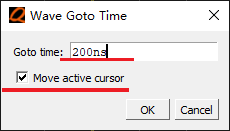

Position the cursor to the specified time point

First select the cursor you want to locate , then Edit -> Goto

If you want to locate 200ns, Input to Goto time Enter... In the column 200ns that will do , Pay attention to check Move active cursor

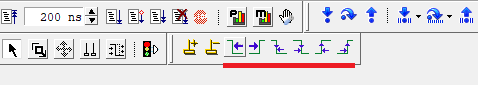

Quickly locate on the signal / Lower edge

Select the signal to be located , Select the cursor to be positioned , Then click the following icon , Hover the mouse over an icon , You can see the English interpretation of the icon :

Reference resources

边栏推荐

- Debezium series: PostgreSQL loads the correct last submission LSN from the offset

- BZOJ 3747 POI2015 Kinoman 段树

- IC科普文:ECO的那些事儿

- 银河证券在网上开户安全吗?

- c语言oj得pe,ACM入门之OJ~

- 计算lnx的一种方式

- Fundamentals of deep learning convolutional neural network (CNN)

- 【数字IC验证快速入门】8、数字IC中的典型电路及其对应的Verilog描述方法

- 2023年深圳市绿色低碳产业扶持计划申报指南

- 字节跳动Dev Better技术沙龙成功举办,携手华泰分享Web研发效能提升经验

猜你喜欢

How to safely and quickly migrate from CentOS to openeuler

深度学习 卷积神经网络(CNN)基础

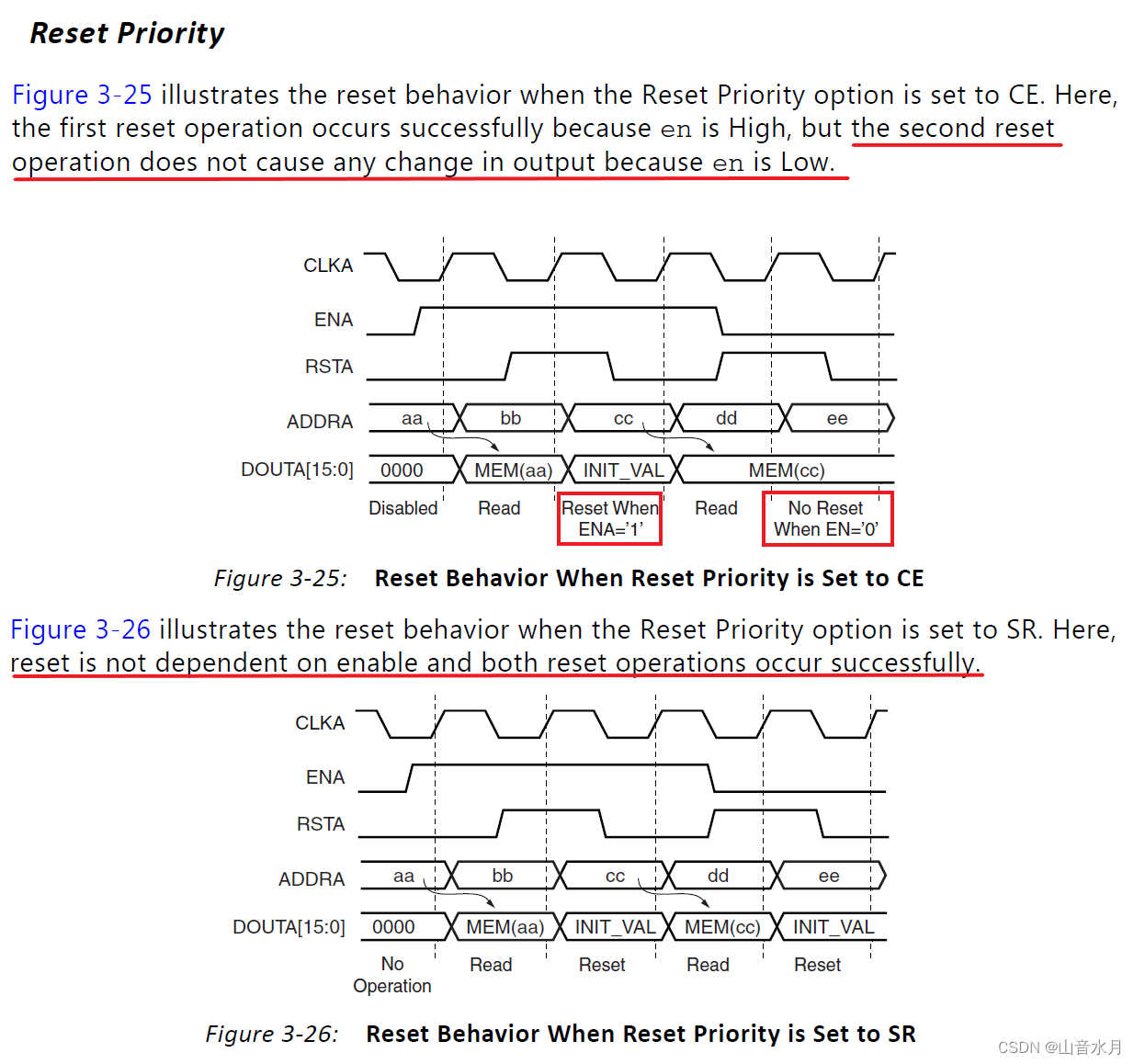

关于BRAM IP复位的优先级

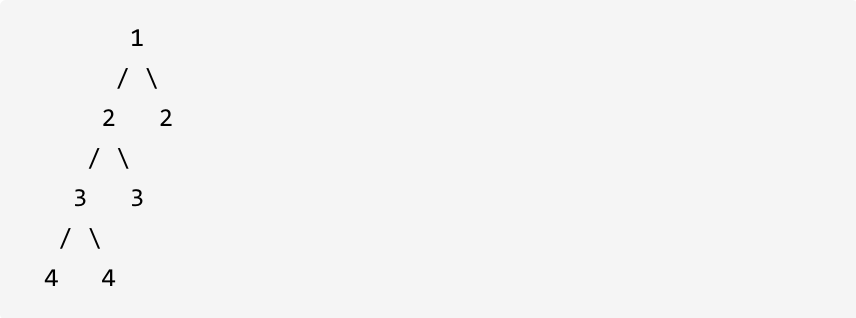

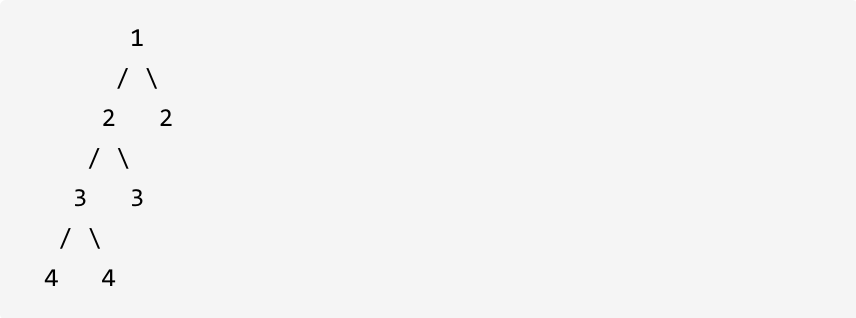

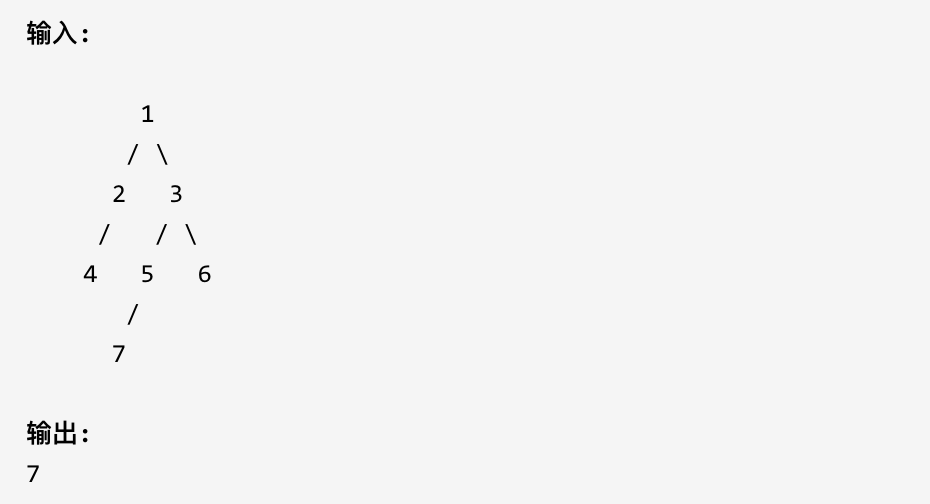

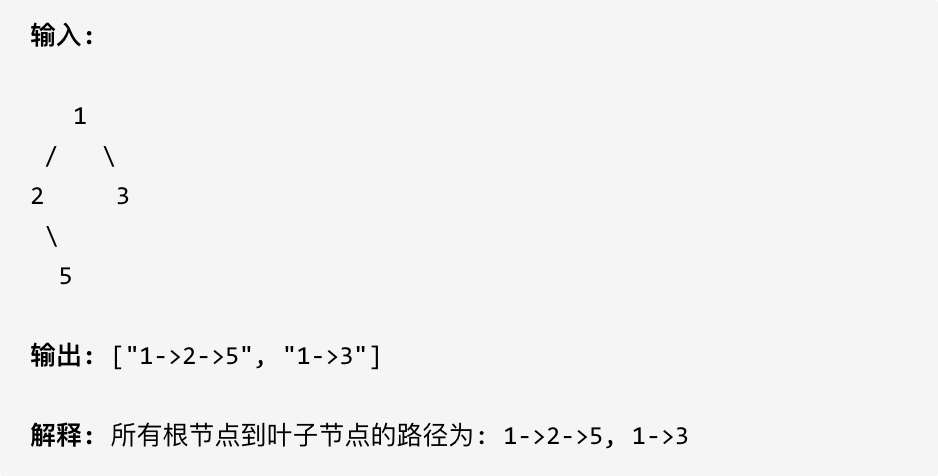

Leetcode brush questions: binary tree 11 (balanced binary tree)

Leetcode skimming: binary tree 16 (path sum)

leetcode刷题:二叉树11(平衡二叉树)

Leetcode brush question: binary tree 13 (the same tree)

leetcode刷题:二叉树18(最大二叉树)

Leetcode: binary tree 15 (find the value in the lower left corner of the tree)

leetcode刷题:二叉树12(二叉树的所有路径)

随机推荐

浅浅的谈一下ThreadLocalInsecureRandom

Leetcode: binary tree 15 (find the value in the lower left corner of the tree)

Debezium series: PostgreSQL loads the correct last submission LSN from the offset

深度学习 卷积神经网络(CNN)基础

How to retrieve the root password of MySQL if you forget it

Is it safe for Anxin securities to open an account online?

Redis cluster simulated message queue

Interviewer: what is the internal implementation of set data types in redis?

Let's talk about threadlocalinsecurerandom

【数字IC验证快速入门】9、Verilog RTL设计必会的有限状态机(FSM)

leetcode刷题:二叉树18(最大二叉树)

Leetcode skimming: binary tree 16 (path sum)

Wechat applet regular expression extraction link

Leetcode brush questions: binary tree 11 (balanced binary tree)

Oracle-表空间管理

字节跳动Dev Better技术沙龙成功举办,携手华泰分享Web研发效能提升经验

js实现禁止网页缩放(Ctrl+鼠标、+、-缩放有效亲测)

零道云新UI设计中

淺淺的談一下ThreadLocalInsecureRandom

Fundamentals of deep learning convolutional neural network (CNN)