当前位置:网站首页>Zynq learning notes (3) - partial reconfiguration

Zynq learning notes (3) - partial reconfiguration

2022-07-06 04:44:00 【Yaojiawan】

Dynamic local reconstruction Dynamic Partial Reconfiguration(DPR), seeing the name of a thing one thinks of its function , Partial refactoring is when you download all bit After configuration , You can download local partitions bit File to dynamically modify the logical function of the corresponding partition , At the same time, the logical functions of other partitions continue to operate without interruption .

Typical applications

Local refactoring optimizes the traditional FPGA application , Through this technology, the size is reduced , weight , Power consumption and cost .

A typical example is the network switch . Each network switch has multiple ports , Each port can support multiple interfaces , such as 10GigE ,OC48 And optical fiber and so on . However, in FPGA Before configuration , It is impossible to predict which network interface users will use , Therefore, all the interface control logic of each port can only be in FPGA To realize . As shown in the figure below :

Obviously, this way is wasted FPGA Internal resources , Added FPGA Area and power consumption of . Local refactoring can achieve more effective design methods , As shown in the figure below :

In designing , We pre design and compile the control logic of various types of network interfaces into bitstream file , Stored in the memory space of the processor or SD card On , When a user configures a certain type of network interface , Corresponding bitstream Download to the relevant local refactoring block .

Local reconfiguration technology is also needed in industrial controller design . For example, in modularity PLC in , There are many kinds of IO Module exists , Use backplane FPGA High speed IO Logic , For example, high speed PWM The signal , Pulse count , Decoder interface , And analog quantity acquisition , Every IO There are more than ten slots in the module IO Control line . But each slot corresponds to FPGA Control logic and inserted IO Modules correspond , stay PLC It is impossible to determine when leaving the factory . therefore , have access to FPGA Of The function of dynamic local logic configuration . When the processor passes IO Internal to the module EEPROM The data of IO The type of module . Then the corresponding logical bit Download to some areas of the Bureau .

Dynamic local configuration and matlab /simulink Algorithm

matlab It is a famous scientific computing software . and simulink Is in matlab Modeling based on . Simulation and analysis software . More Than This ,matlab/simulink Be able to generate product level C、C++、CUDA、PLC、Verilog and VHDL Code , And deploy it directly to your embedded system . Now? ,matlab、simulink It has been widely used , Including wireless communication , Power electronics , Control system , robot , Advanced driving AIDS , Number twin , Artificial intelligence and other fields . matlab/simulink The model-based design method is adopted , Directly generate various product level codes , Realized from “ Model to code ” Design Automation . This is one of the most popular features . It saves a lot of coding and FPGA The design is tedious , The efficiency of prototype design is greatly improved .

The idea of model-based design is welcomed by engineers in various industries , however , Realizing this ideal is a complex process , at present matlab Supported by Xilinx and Intel Of FPGA series . Realization matlab to fpga The process is as follows

- 1 Use matlab/simulink Modeling and simulation

- 2 Export Algorithm verilog Language .

- 3 Use FPGA Design software will verilog Add algorithm to vivado In the project . Produce a IP nucleus .

- 4 Simulink Through Ethernet and ZYNQ Processor communication ,ZYNQ Processor passes AXI Interface access IP nucleus .

- 5 Processor passes FPGA Of PCAP(Processor Configuration Access Port ) and ICAP(Internal Configuration Access Port) Realization FPGA Configuration of .

- 6 combination FPGA Dynamic local reconstruction technology implementation Matlab to FPGA The function of .

according to IP Specific requirements for nuclear , You can choose different AXI Interface , For example, using AXI_DMA Realization IP High speed data transmission between core and processor , adopt AXI_Lite Realize register access and configuration .

The above figure is a high-level architecture diagram , Shows Zynq Processors on the platform and FPGA Streaming data transmission between architectures . Usually ,AXI4-Stream Interface and DMA The controller is used together , Transfer a large amount of data from the processor to FPGA. Data is usually represented as vector data on the software side .DMA The controller reads vector data from memory , And pass AXI4-Stream The interface will “ Streaming ” To FPGA IP.“ flow ” Each sample of the process sends a data element , It means FPGA IP The data path of midstream algorithm uses scalar data type .

Dynamic local configuration and IEC61499 Function block

IEC61499 It is oriented to distributed industrial control , Standards for functional blocks of measurement and monitoring systems . majority IEC61499 Function blocks are implemented by software . In order to improve the IEC61499 Real time performance of function block , Part of the IEC61499 Function block , Composite function blocks and sub applications can be used FPGA To achieve . for example PWM Generator , Analog data acquisition ,PID Closed loop control algorithm , Digital signal processing of analog signals (DSP), wave filtering ,FFT And other algorithms can be used FPGA To achieve . It's popular in recent years AI The algorithm can also pass HDL To achieve . And download to FPGA Running in some areas of the dynamic Bureau .

ZYNQ Dynamic local configuration mechanism

The dynamic local refactoring mechanism will IP Nuclear bitstream Stored in the processor (PS) In the end memory , Through software and interface bit Download the file to the local reconstruction block . stay ZYNQ in , There are two kinds for PR The plan , They are :

PCAP(Processor Configuration Access Port)

ICAP( Internal Configuration Access Port)

PCAP

ZYNQ The startup process of is roughly as follows :

Reference resources 《Zynq UltraScale\+ Device Technical Reference Manual》,FSBL In the writing BitStream Before , initialization PCAP Interface . adopt PCAP write in Bitstream.

ICAP Interface

ICAP yes Xilinx One provided by the company AXI4 IP nucleus . It is used to access FPGA Internal configuration memory . It's based on AXI Lite Interface .

PCAP And ICAP The difference between

adopt XDcfgtransferBitFile Function will RP Of Bitstream from DRAM Transferred to the PCAP, The main advantage of this scheme is that no PL resources . The throughput of transmission is 128MB. Its main disadvantage is that it suspends the processor during refactoring .

Xilinx It also provides a IP nucleus (AXI_HWICAP) And Library XHwIcapdeviceWrite. Allow to use ICAP To achieve PR.AXI_Lite Interface by GP Port connects it to PS. Because this method does not use DMA So the transfer rate is 19MB. You can also use DMA The way .

vivado Design process

There are some on the Internet vivado software development PR The article , But it's messy . Let's follow

xilinx fpga Partial dynamic reconfiguration (Partial Reconfiguration) Design implementation The process of the method of one article .

Also refer to XILINX The company's ug909-vivado-partial-reconfiguration.pdf

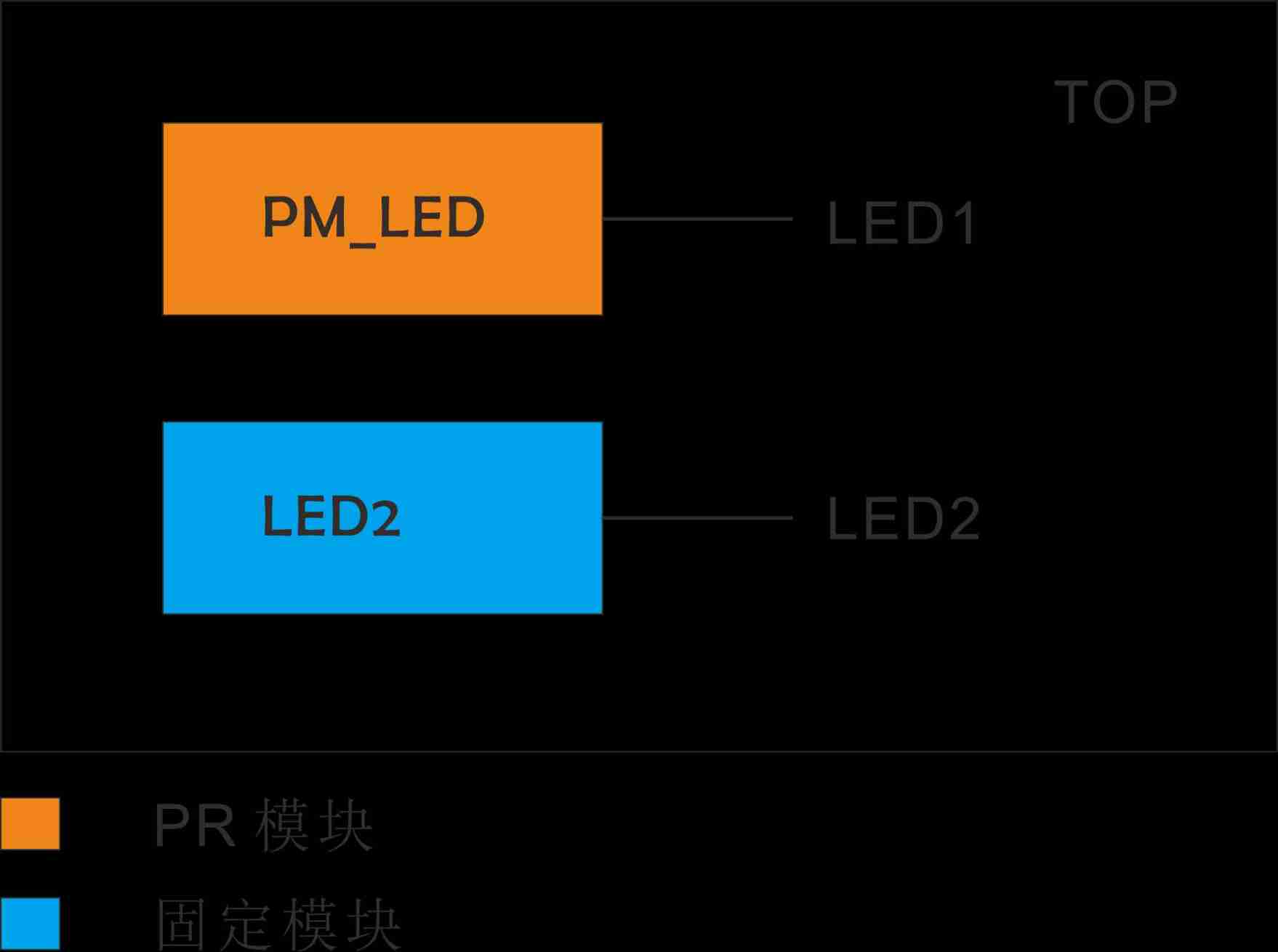

In this case , We designed two RP modular , A fixed module

among :

PM_LED It is a local reconstruction module , Can be configured as 1 Seconds or 4 Second blink .LED2 It is a fixed module 2 Second blink .

They correspond to verilog file :

led.v 1 second

led_4s 4 second

led2_2s 2 second

design process

1 Build a project , take top.v ,led.v and led.v Import source file .

Be careful : When building a project , Just import one RM The source code of the module (led.v) That's all right. .

2 Once the project is completed , Turn the project into a partial refactoring project , choice Tools > Enable Partial Reconfiguration.

This operation is irreversible . therefore , if necessary , Keep it in advance .

3 Once the project turns into PR project , To define the refactoring partition (Reconfigurable Partitions). stay led Right click the name of the module . choice Create Partition Definition

Enter the corresponding pd and pm name , Enter led and led_1s.

4 Configure all the details of the project , Include partitioning for each refactoring (Reconfigurable Partitions) Add additional reconfigurable modules (Reconfigurable Modules). All this work passed (Dynamic Function eXchange wziard) complete .

ad locum , We set up partion Definition name by led,Reconfiguration module Name by led_4s

And add led_4s.v file ., If more RM modular , Presumably, it is also added in this way .

5 Start FPGA The synthesis of (Run Synithesis), It's a long process .

6 When the synthesis is completed , To be in FPGA Draw an area as PM The physical location of .

7. Implementation and generation bit

Conclusion

Only this and nothing more , Things are not finished yet . Many questions :

- How to join PCAP or ICAP Interface module

- How to write the upper software

- From the above design process , In the design PR Project time , Every RM The source code of has been completed , If image Matlab/Simulink

- Produced verilog Code , The code was not determined during the design of the project , How to define reconfigurable partitions ? Can I reserve it ?

Take your time !

边栏推荐

- Introduction to hashtable

- 满足多元需求:捷码打造3大一站式开发套餐,助力高效开发

- 最高法院,离婚案件判决标准

- Meet diverse needs: jetmade creates three one-stop development packages to help efficient development

- ORM aggregate query and native database operation

- ue5 小知识点 开启lumen的设置

- SQL注入漏洞(MSSQL注入)

- Flink kakfa data read and write to Hudi

- win10电脑系统里的视频不显示缩略图

- Guitar Pro 8.0最详细全面的更新内容及全部功能介绍

猜你喜欢

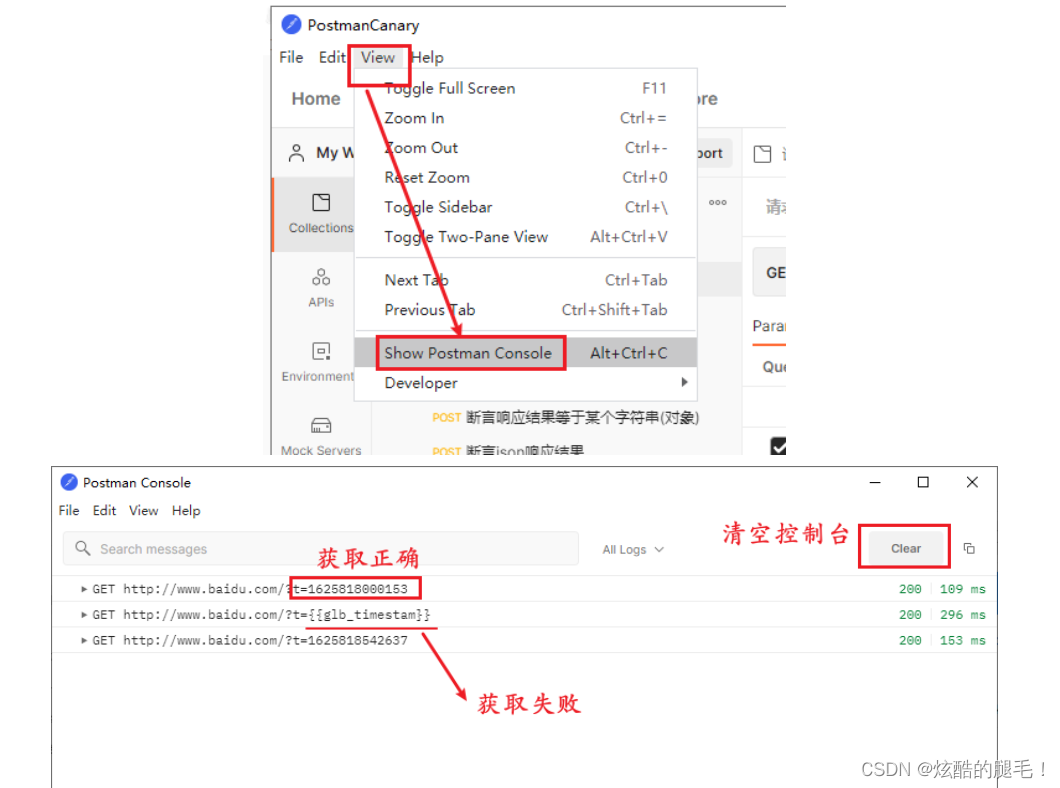

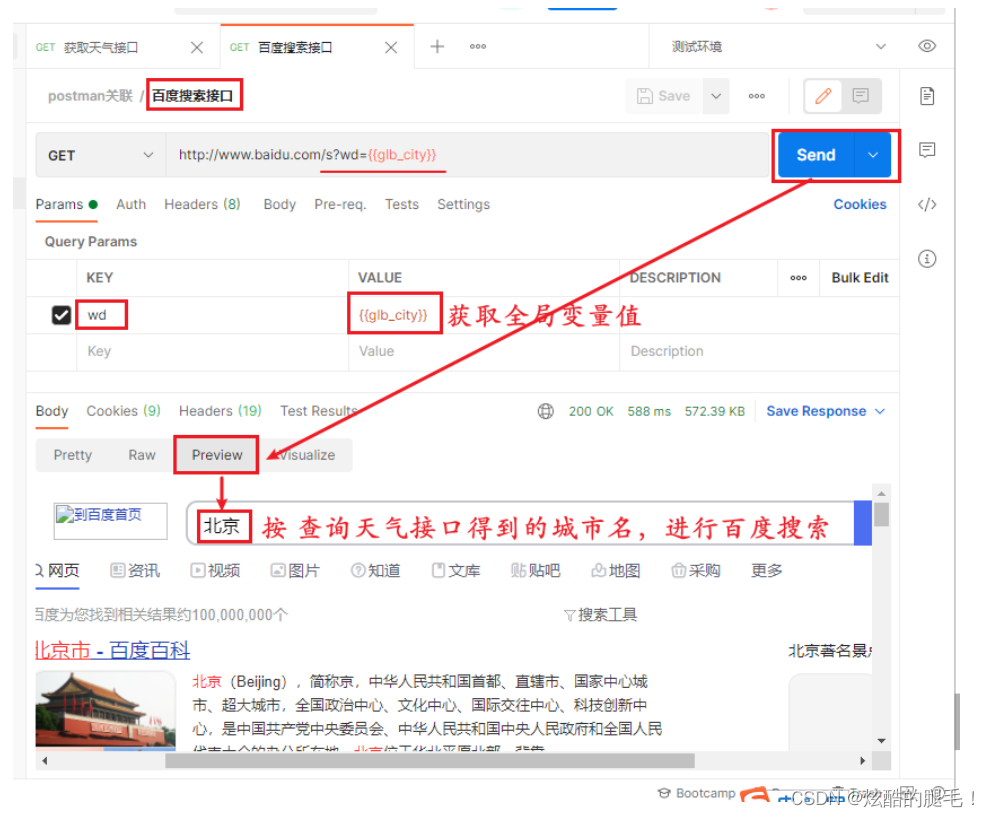

Postman前置脚本-全局变量和环境变量

Is the mode of education together - on campus + off campus reliable

Selection of slow motion function

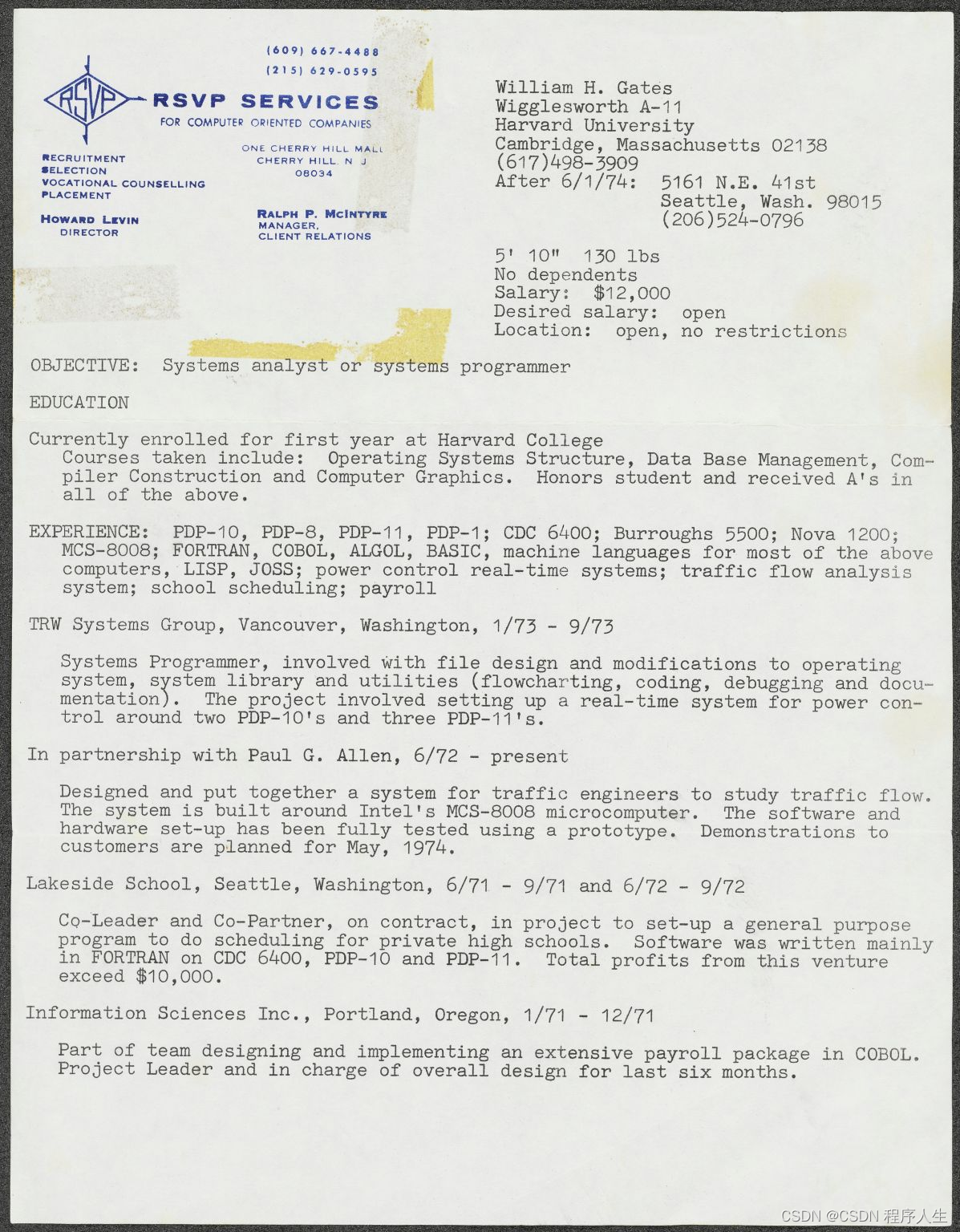

Bill Gates posted his 18-year-old resume and expected an annual salary of $12000 48 years ago

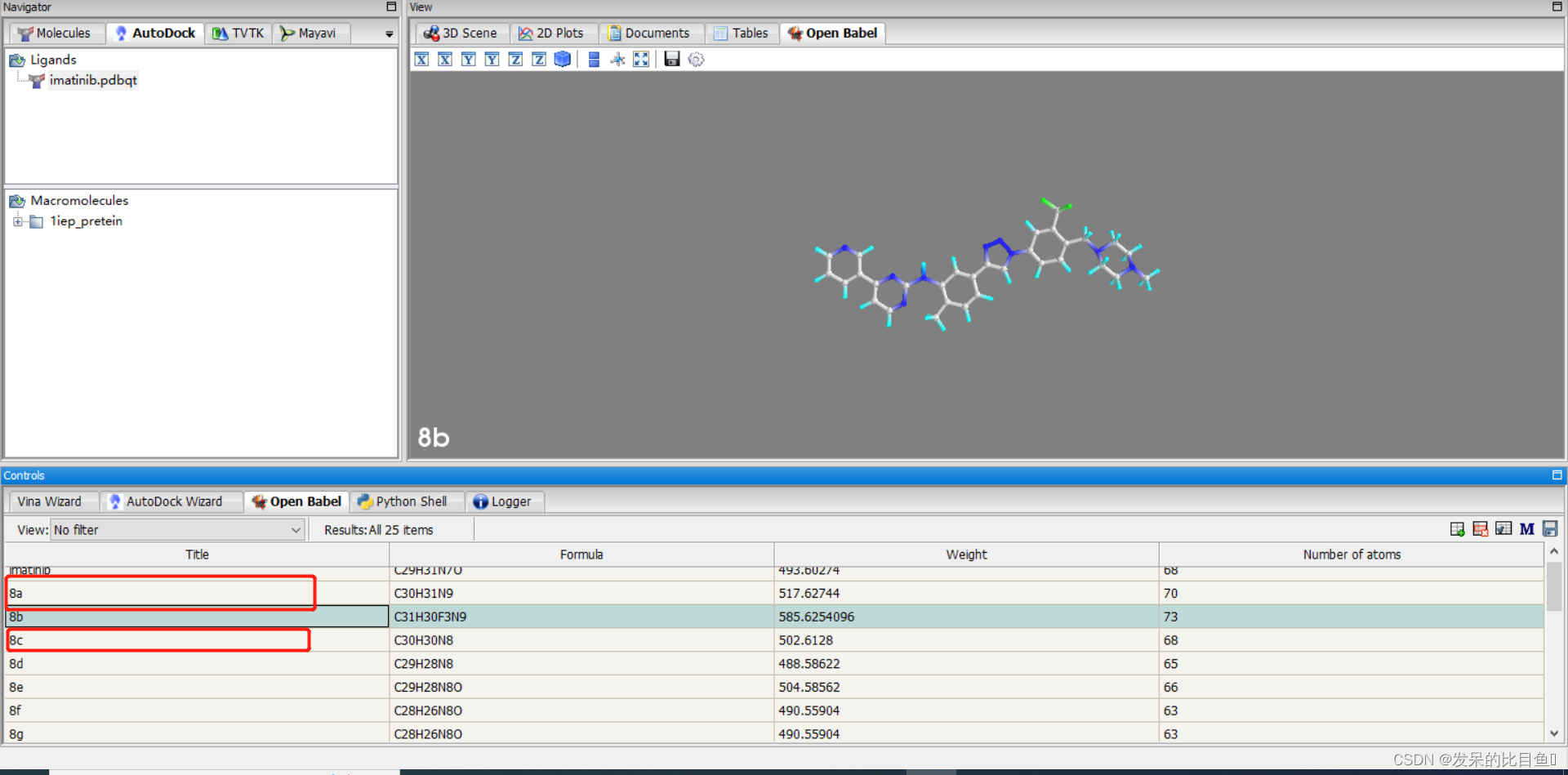

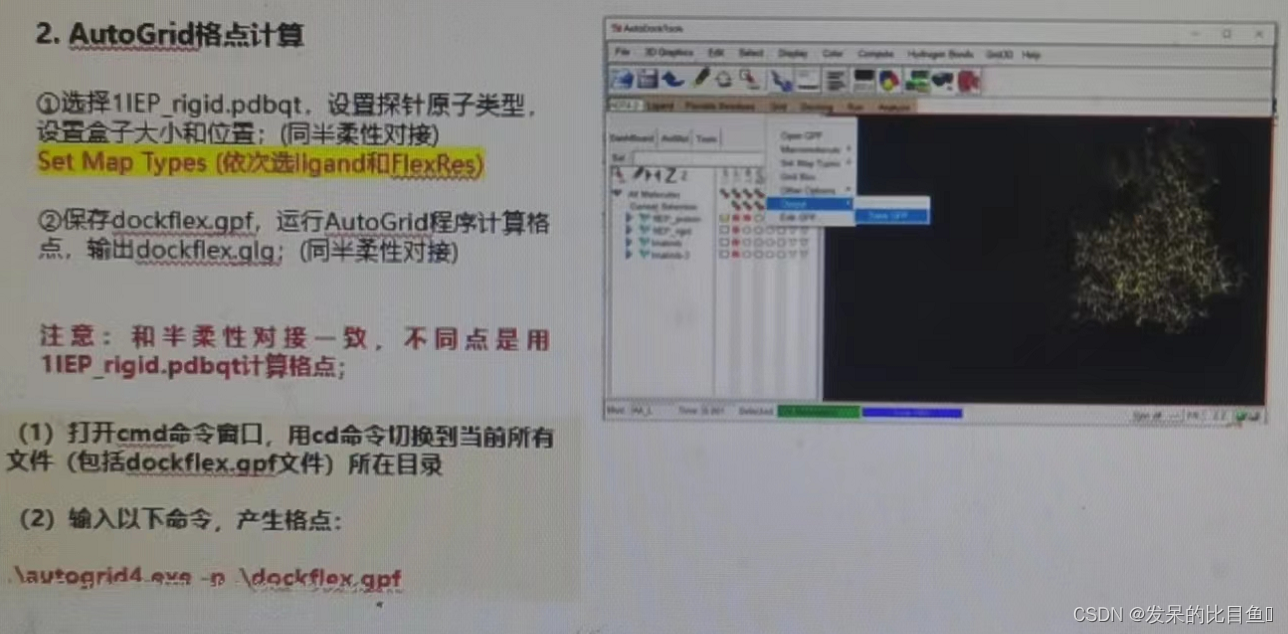

CADD course learning (8) -- virtual screening of Compound Library

SQL injection vulnerability (MSSQL injection)

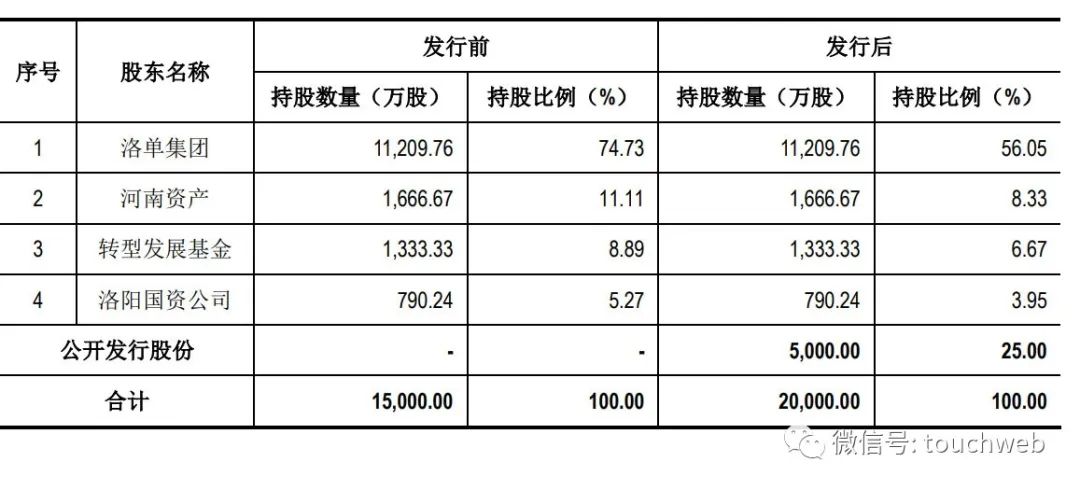

L'introduction en bourse de MSK Electronics a pris fin: 800 millions de RMB d'actifs de Henan étaient des actionnaires

Postman关联

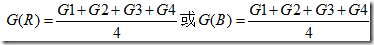

ISP学习(2)

CADD课程学习(7)-- 模拟靶点和小分子相互作用 (柔性对接 AutoDock)

随机推荐

内核判断i2c地址上是否挂载外设

最高法院,离婚案件判决标准

Redis has four methods for checking big keys, which are necessary for optimization

Visio draw fan

729. My schedule I (set or dynamic open point segment tree)

The ECU of 21 Audi q5l 45tfsi brushes is upgraded to master special adjustment, and the horsepower is safely and stably increased to 305 horsepower

Platformio create libopencm3 + FreeRTOS project

Dynamic programming (tree DP)

2328. Number of incremental paths in the grid graph (memory search)

SharedPreferences 源码分析

[Chongqing Guangdong education] engineering fluid mechanics reference materials of southwestjiaotonguniversity

The kernel determines whether peripherals are attached to the I2C address

SharedPreferences source code analysis

Canal synchronizes MySQL data changes to Kafka (CentOS deployment)

Recommendation | recommendation of 9 psychotherapy books

C. The third problem

关于imx8mp的es8316的芯片调试

Platformio create libopencm3 + FreeRTOS project

The IPO of mesk Electronics was terminated: Henan assets, which was once intended to raise 800 million yuan, was a shareholder

Orm-f & Q object