当前位置:网站首页>【无标题】

【无标题】

2022-06-29 07:53:00 【1615549892】

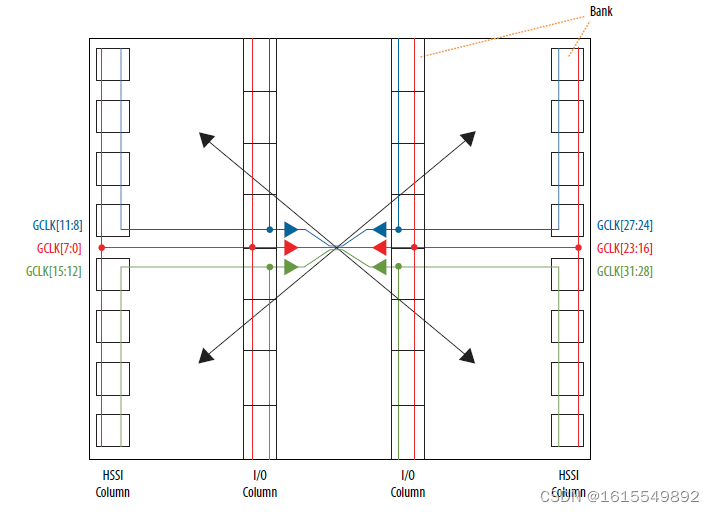

Arria 10 器件包括具有下面层次结构的时钟网络:

• 全局时钟(GCLK)网络

• 局域时钟(RCLK)网络

• 外围时钟(PCLK)网络

— 小型外围时钟(SPCLK)网络

— 大型外围时钟(LPCLK)网络

- Global clock (GCLK) networks

- Regional clock (RCLK) networks

- Periphery clock (PCLK) networks

- Small periphery clock (SPCLK) networks

- Large periphery clock (LPCLK) networks

时钟管脚:

HSSI: 12 个差分对REFCLK_GXB[L,R][1:4][C,D,E,F,G,H,I,J]CH[B,T][p,n]管脚

I/O :48 个单端或24个差分对,I/O:CLK[2,3][A…L]_[0,1][p,n]管脚

| GCLK | RCLK | SPCLK/LPCLK–HSSI | SPCLK/LPCLK–I/O | |

|---|---|---|---|---|

| 每个通道的物理介质附加子层(PMA)和 物理编码子层(PCS)TX 和RX 时钟 | Y | Y | Y | N |

| 每个通道的PMA 和PCS TX 和RX 分频时钟 | Y | Y | Y | N |

| Hard IP 内核时钟输出信号 | Y | Y | Y | N |

| DLL 时钟输出 | Y | Y | Y | N |

| 小数分频PLL (fPLL)C 计数器输出 | Y | Y | Y | N |

| I/O PLL C 计数器输出 | Y | Y | N | Y |

| 用于反馈的I/O PLL M 计数器输出 | Y | Y | Y | Y(add C计数器输出) |

| REFCLK | Y | Y | Y | N |

| 时钟输入引脚 | Y | Y | Y | Y |

| 内核信号 | Y | Y | Y | Y |

| 相位对齐计数器输出 | Y | Y | N | Y(DPA 输出(LVDS I/O only)) |

时钟有3个层次:

- GCLK, RCLK, PCLK, and GCLK and RCLK feedback clocks

- Section clock (SCLK)

- Row clocks

GCLK,RCLK 和PCLK 时钟网络走线到HSSI 和I/O 之前,先走线到SCLK。

顶部和底部的RCLK只能驱动垂直2行,中间的RCLK可以驱动垂直6行。

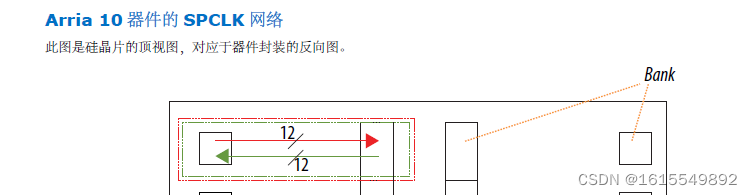

每个HSSI和I/Obank有12个SPCLK。

12个SPCLK覆盖在HSSI bank的1个SCLK spine region和邻近IObank的1个SCLK spine

专用时钟输入管脚的来源如下:

• fPLL—

来自HSSI 列的REFCLK_GXB[L,R][1:4][C,D,E,F,G,H,I,J]CH[B,T][p,n]

• I/O PLL—来自I/O 列的CLK[2,3][A…L]_[0,1][p,n]

可以将复位连接到专用时钟管脚上,进一步简洁到GCLK上 、 RCLK

当一个时钟网络断电时,由时钟网络提供的所有逻辑均处于关闭状态,从而降低了器件的总功耗。

通过Quartus Prime 生成的配置文件(.sof 或.pof)中的配置位设置,未使用的GCLK,RCLK

和PCLK 网络会自动断电。

动态时钟使能或者禁用功能使内部逻辑能够对GCLK 和RCLK 网络进行同步上电或者断电。此功能

独立于PLL,并直接应用于时钟网络。

注意: 您不能动态使能或禁用驱动PLL 的GCLK 或RCLK 网络。当内核频率很高时,动态门控大型时钟可

能会影响芯片性能。

每个HSSI和I/Obank有12个SPCLK。

12个SPCLK覆盖范围是:HSSI bank的SCLK spine region和邻近IObank的SCLK spine region

I/O PLL:差分时钟或者单端时钟。CLK_[2,3][A…L]_[0,1][p,n]管脚具有到PLL 的专用连接.

fPLL : HSSI 列,仅支持差分时钟输入。

通过全局或局域时钟驱动PLL 能导致PLL 输入上的更高抖动,并且PLL 将无法对全局或局域时钟进

行完全补偿。Intel 建议使用专用时钟输入管脚来实现驱动PLL 的最佳性能。

内部逻辑:您可以使用内核布线驱动每个GCLK 和RCLK 网络,以使内部逻辑能够驱动高扇出、低偏斜信号。

DPA 输出:每个DPA 都能够驱动PCLK 网络。

时钟输出:HSSI 时钟输出能够驱动GCLK,RCLK 和PCLK 网络。

PLL 时钟输出:fPLL 和I/O PLL 时钟输出能够驱动所有时钟网络。

每个GCLK,RCLK 和PCLK 网络都有各自的时钟控制模块。时钟控制模块具有以下特性:

时钟源选择(动态选择仅用于GCLK)

时钟断电(静态或动态时钟使能或禁用仅用于GCLK 和RCLK)

Arria 10 器件系列包含以下PLL:

fPLL—可用作小数PLL 或整数PLL

I/O PLL—仅用作整数PLL

fPLL 位于HSSI Bank 中,与收发器模块相邻。每个HSSI bank 包含两个fPLL。

I/O PLL 位于I/O bank 中硬核存储控制器和LVDS 串行器/解串器(SERDES)模块旁边。

每个I/O bank 包含一个I/O PLL。

PLL 级联

Arria 10 器件支持PLL 到PLL(PLL-to-PLL)级联,最多可级联2 个PLL。级联的PLL 必须是毗邻

的PLL。与单一PLL 相比,PLL 级联综合更多的输出时钟频率。

如果设计中存在级联PLL,那么源(上游)PLL 必须采用低带宽设置,而目标(下游)PLL 必须采用高带

宽设置。级联期间,源PLL 的输出充当目标PLL 的参考时钟(输入)。具有级联关系的不同PLL 的带

宽设置必须不同。如果具有级联关系的不同PLL 的带宽设置相等,那么这些级联 PLL 可能会在某些

频率放大相位噪声。

Arria 10 器件仅支持内核应用的I/O-PLL-to-I/O-PLL 级联。在此模式下,上游I/O PLL 和下游

I/O PLL 必须位于同一 I/O 列中。

Arria 10 fPLL 不支持内核应用的PLL 级联模式。

边栏推荐

- Notice on organizing the second round of the Northwest Division (Shaanxi) of the 2021-2022 National Youth electronic information intelligent innovation competition

- 【微服务|OpenFeign】openfeign的超时时间

- À propos de Hook

- 《乔布斯传》英文原著重点词汇笔记(七)【 chapter five】

- Wallpaper applet source code double ended wechat Tiktok applet

- 练习-选择排序

- Sed replace value with variable

- Open an account to buy funds. Is it safe to open an account through online funds-

- Mosaic notes

- 想炒股开户,在网上进行股票开户安全吗?-

猜你喜欢

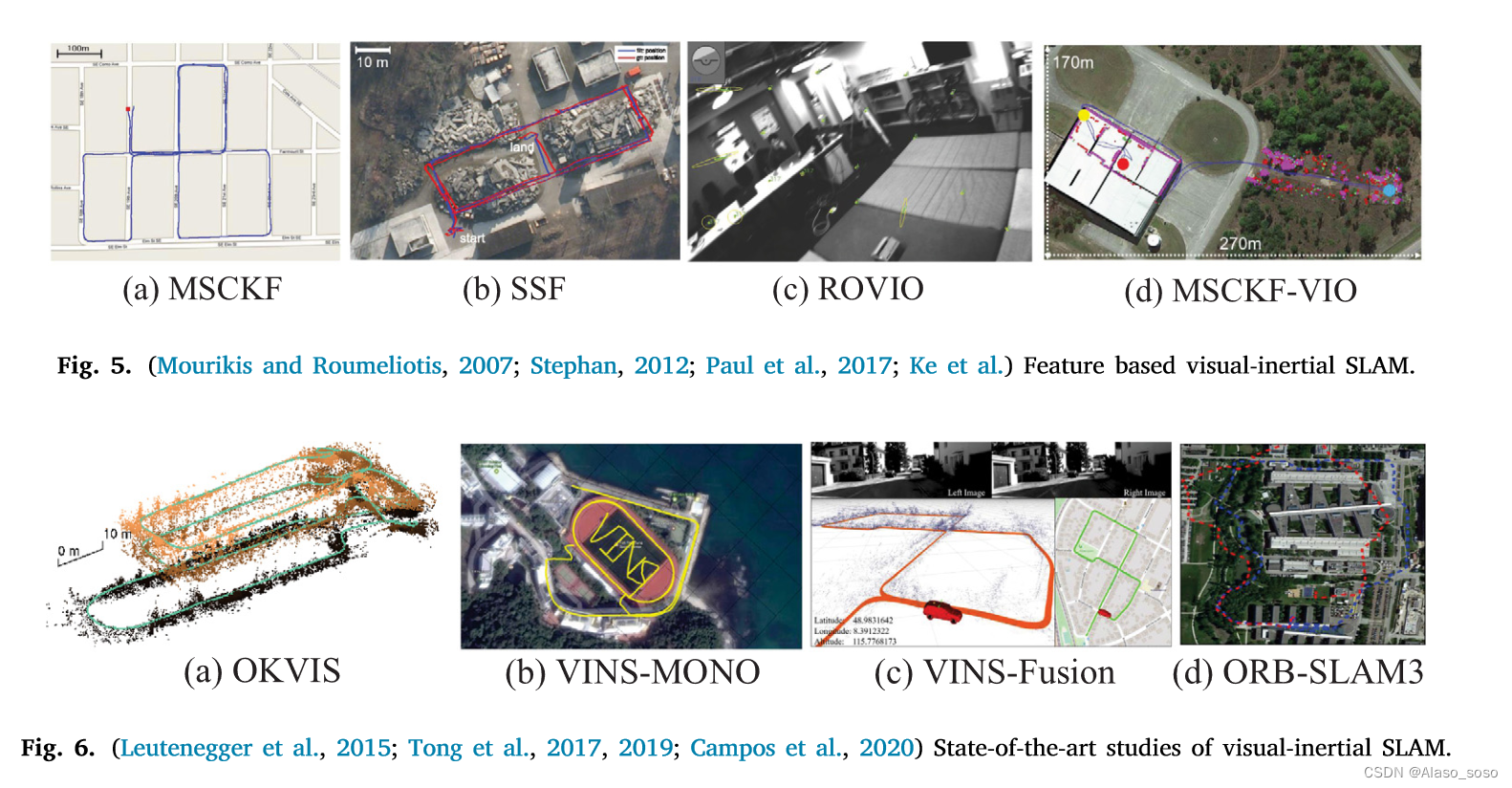

A review of visual SLAM methods for autonomous driving vehicles

华为设备配置小型网络WLAN基本业务

目标跟踪【单目标跟踪(VOT/SOT)、目标检测(detection)、行人重识别(Re-ID)】

Memoirs of actual combat: breaking the border from webshell

《动手学深度学习》(一)-- 线性神经网络

新版付费塔罗牌测算源码 (附带搭建教程)

互斥量互斥锁

【微服务|OpenFeign】openfeign的超时时间

笔记本电脑快速连接手机热点的方法

802.11--802.11n协议 PHY

随机推荐

Flutter file read / write -path_ provider

Verilog first experience

马赛克笔记

Write time replication of hugetlbfs

笔记本电脑快速连接手机热点的方法

Why are two SQL statements that execute very fast, especially after the Union

Message Oriented Middleware: pulsar

自动化运维管理平台——spug的搭建和日常使用

Memoirs of actual combat: breaking the border from webshell

[quantitative investment system]django realizes screening and paging from the database

x86和x64的区别

Set up Jenkins environment and automatically associate packaged project jars for automatic release

Solidity deploy and validate agent contracts

Blueprint basis

Hook 简介

批量处理实验接触角数据-MATLAB分析

Notice on organizing the second round of the Northwest Division (Shaanxi) of the 2021-2022 National Youth electronic information intelligent innovation competition

搭建开源物联网平台教程

互斥量互斥锁

NLP标注工具:Label Studio实现多用户协作打标