当前位置:网站首页>I2C summary (single host and multi host)

I2C summary (single host and multi host)

2022-07-06 09:40:00 【Running little race rabbit】

I2C In the process of use, a single host is hardware I2C Or hardware I2C It's not too hard , Understanding the timing is easy to achieve . Also, many people think that hardware I2C There are many disadvantages , In fact, this is a fallacy , Hardware I2C Better than software in stability I2C, And it doesn't take up MCU Time , Can achieve I2C interrupt . If the system has hardware I2C, Then you must choose hardware I2C. Multiple hosts I2C It's a little complicated. , It should be noted that clock synchronization and bus arbitration .

One 、I2C summary

When the master sends data to the slave : Host control SCL Signal line and SDA The signal line , The slave is just SCL Read passively when the line is high SDA Line .

When the master reads the data from the slave : The host sends a clock signal , The slave is only guaranteed when the clock signal is high SDA It's just a state of .

SDA and SCL Has been pulled up by the pull-up resistor ,master Can be controlled ( Pull down or release ) These two lines , and slaver Control only SDA Line . When master When sending data ,master Will be timely SDA and SCL Pull down or release ( pull up ). The exact timing should be like this :

When mater To send a start when ,mater Will SDA Pull it down , That's it , Because the SCL It must be High. Okay , One start It was sent out like this . and slaver You will also find this start Signal generation ,slaver Will be ready to receive the next data . Then ,master To send a Byte The data of the , Send this one by one 8 individual bits. At this time master Will be will be SCL Pull it down , And then in SCL In the low state, a bit Ready to put SDA On ( Like sending a 0,master By pulling down SDA Come and put this 0), then master Will be able to SCL pull up ( Release ), here slaver Will immediately detect SCL The change of , So smart slaver I know master The one that has been sent bit Be on it ,slaver Will be here SCL As soon as possible during the high level (maser I won't wait for you for long ) Read it SDA, Well, I read one 0,slaver Put the 0 Put it into your shift register for subsequent processing .master After a set time SCL Pull down again , And then in SCL Put the next... For the low-level period bit Put it in SDA On , Then take it. SCL pull up , then slaver stay SCL Read again during the high level of SDA..... So again and again 8 Time , One Byte The transmission of is over . When this 8 individual bit After sending ,SCL It is at low level ( By master Pulled down ),SDA It is out of high level (master Has been released SDA).

When a byte is sent ,master Will release SDA( pull up ) And pull down SCL, here slaver If you plan to send a ACK Words , It must be here SCL By master Take the initiative to lower for a short time SDA Pull down and hold ( We said before ,SDA It has been master Release , therefore slaver Only then has the opportunity to pull down this SDA).master After a certain time, it will SCL pull up , And read during the pulling up SDA The state of the line , If you read low , It is considered that it received from slaver Response (ACK), Otherwise, I think slaver No response (NACK) The one just sent Byte. This process is what we call i2c The number in the communication 9 Clock cycles . When master Finish reading this ACK / NACK after , Will again SCL Pull it down , To inform slaver: The first 9 Clock cycles have ended , You can now release SDA 了 . And then master Also you can ask the SDA Get ready for the next Byte One of the first bit. Then repeat the above process ..... perhaps ,master Maybe I want to send one next stop In the past , that master It will be here SCL For a low time will SDA Pull it down , And then SCL pull up , stay SCL The period of high will be SDA Release ( pull up ) . such , One STOP Bits are produced . You will find later SDA and SCL All high , This is the so-called bus idle !

In a word :SCL Is one-way , from master control . and SDA It's two-way ,master Can be controlled ,slaver You can also control .

When reading the above process , Always remember :SDA The data on must be in SCL It is stable during high level ,SDA The data on can only be in SCL During the low level change .( Exceptions to start and end signals )!

in addition , It should be noted that , Not every transmission 8 After bit data , There will be ACK The signal , There are the following 3 Species exception :

(1) When the slave cannot respond to the slave address ( For example, it is busy with other things and cannot respond I2C Bus operation , Or this address has no corresponding slave ), In the 9 individual SCL In cycle SDA The line is not pulled down , That is, no ACK The signal . At this time , A host sends a message P The signal terminates transmission or resends a S The signal starts a new transmission .

(2) If the slave receiver cannot receive more data during transmission , It doesn't emit ACK The signal . such , The host can realize this , So as to send a P The signal terminates transmission or sends a S The signal starts a new transmission .

(3) The host receiver receives the last byte , It won't send out ACK The signal . therefore , Release from the transmitter SDA Line , To allow the host to issue P The signal ends transmission .

Two 、I2C Bus clock synchronization and bus arbitration

I2C Bus SCL The synchronous clock pulse is generally a shift pulse sent by the master controller as serial data . whenever SDA After a stable data appears on , stay SCL Send a high-level shift pulse .

1. SCL Signal synchronization

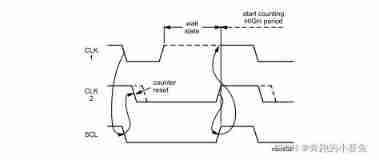

Clock synchronization is through I2C Interface SCL Line and Implementation . What do you mean ?

If the controlled device wants the master controller to reduce the transmission speed, it can be achieved by SCL The method of actively pulling down and extending its low-level time informs the master controller , When the master controller is preparing for the next transmission discovery SCL Wait when the level of is pulled down , Until the controlled device completes the operation and releases SCL Control of the line . Since then , The master controller is actually controlled by the clock synchronization of the controlled device . so SCL The low level on the line is controlled by the clock

The device with the longest low level determines ; The high-level time is determined by the device with the shortest high-level time . This is clock synchronization , It solves I2C Speed synchronization of the bus .

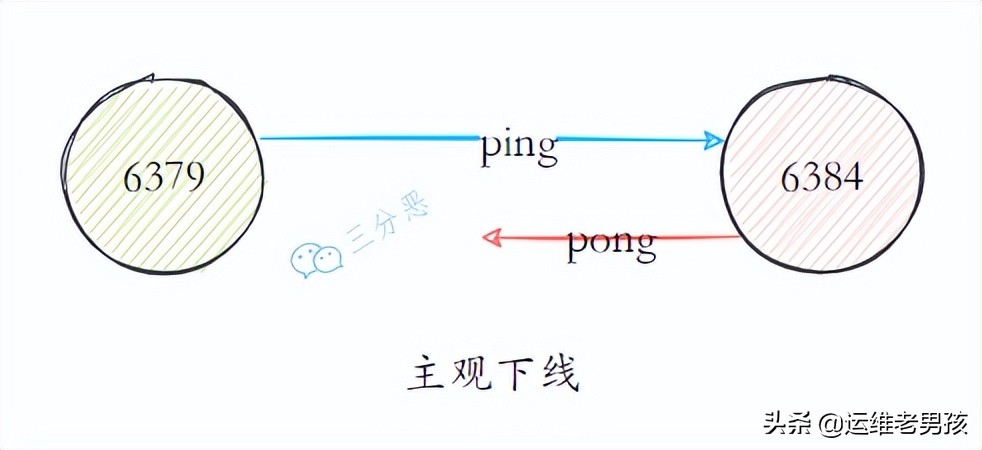

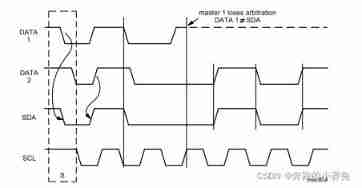

2. I2C Bus arbitration on the bus

If you are in the same I2C There are two main controllers in the bus system , The clock signals are SCK1、 SCK2, They all have the ability to control the bus . Suppose both begin to control the bus for communication , because “ Line and ” The role of , Before the bus arbitrates , Both of the main controllers will use “ Line and ” In the form of joint participation SCL Use of wires , Fast main controller 1 Wait for the lagging master 2 .

about SDA Use of online signals , The two main controllers also follow “ Line and ” To influence SDA Level change on the . Suppose the main controller 1 Data to send DATA1 by “101 ……”; Main controller 2 Data to send DATA2 by “1001 ……”. After the bus is started, the two main controllers should detect their output level every time they send a data bit , As long as the detected level is consistent with the level sent by yourself , They will continue to occupy the bus . In this case, the bus is still not arbitrated . When the main controller 1 Send the first 3 Bit data “1” when ( Main controller 2 send out “0”) , because “ Line and ” Result SDA The level on the is “0”, So when the main controller 1 Check your output level

when , You'll detect something that doesn't match yourself “0” level . At this time, the main controller 1 Had to give up control of the overall ; So the main controller 2 Become the only master of the bus .

① For the whole arbitration process, the master controller 1 And main controller 2 No loss of data ;

② Each master controller has no priority to control the bus ;

③ The bus control is then determined , They follow “ Low level first ” Principles , That is, the one who sends the low level first will control the bus .

According to the description above , “ Clock synchronization ” And “ Bus arbitration ” It can be summarized as follows :

① The master controller passes the detection SCL On the level to adjust the speed synchronization problem with the slave device —— Clock synchronization ;

② The master controller passes the detection SDA Determine whether the bus occurs based on the level transmitted by itself “ Conflict ”—— Bus arbitration .

therefore , I2C Bus “ Clock synchronization ” And “ Bus arbitration ” It is realized by the special structure of the device interface .

The amount of data accessed continuously is controlled by the master , Specifically, it is sent to the peripheral device “ No response signal ” To end the operation of this data . For data block “ read 、 Write operations ” Pay attention to two points :

( 1) In the read operation, the command word should be sent twice : The first one is with peripheral device address “ Write ” command (R/W=0) , The function is to write the subsequent internal address into the peripheral device “ Address counter ” in , The second is to send with peripheral devices “ read ” command ( R/W=1),

Start really “ Read operations ”. Between the two command words is a “ Start signal S” To segment the ;

( 2) In write operation , Some peripheral devices ( Such as EEPROM) Its continuous writing data is limited , Such as 24C02 The data written continuously each time cannot exceed 8 Bytes ( This is related to the number of internal input buffers ).

边栏推荐

- Le modèle sentinelle de redis

- IDS' deletion policy

- Kratos战神微服务框架(三)

- Global and Chinese markets for hardware based encryption 2022-2028: Research Report on technology, participants, trends, market size and share

- Mapreduce实例(六):倒排索引

- Leetcode:608 树节点

- Minio distributed file storage cluster for full stack development

- Full stack development of quartz distributed timed task scheduling cluster

- 工作流—activiti7环境搭建

- Redis之持久化实操(Linux版)

猜你喜欢

随机推荐

发生OOM了,你知道是什么原因吗,又该怎么解决呢?

May brush question 27 - figure

硬件工程师的真实前途我说出来可能你们不信

Kratos ares microservice framework (III)

Global and Chinese market of electric pruners 2022-2028: Research Report on technology, participants, trends, market size and share

Redis connection redis service command

Redis之发布订阅

Full stack development of quartz distributed timed task scheduling cluster

Webrtc blog reference:

Global and Chinese market of cup masks 2022-2028: Research Report on technology, participants, trends, market size and share

五月刷题26——并查集

Libuv thread

Activiti7工作流的使用

IDS' deletion policy

Processes of libuv

Mapreduce实例(八):Map端join

Global and Chinese markets of SERS substrates 2022-2028: Research Report on technology, participants, trends, market size and share

Detailed explanation of cookies and sessions

Reids之缓存预热、雪崩、穿透

Mysql database recovery (using mysqlbinlog command)