当前位置:网站首页>S32K1xx 微控制器的硬件設計指南

S32K1xx 微控制器的硬件設計指南

2022-07-01 15:07:00 【Rei-ikari】

1 簡介

S32K 系列進一步擴展了汽車行業中高度可擴展的 ARM Cortex MCU 產品組合。它以 KEA 系列的傳統為基礎,同時將更高的內存選項以及更豐富的外設集擴展能力引入各種汽車應用。

S32K 系列器件采用 2.70–5.5 V 電源並專注於汽車環境穩健性,非常適合電氣惡劣環境中的各種應用。這些器件針對提供低引脚數選項的成本敏感型應用進行了優化。

S32K 系列提供廣泛的內存、外圍設備和封裝選項。它們共享通用外設和引脚數,使開發人員能够在 MCU 系列內或在 MCU 系列之間輕松遷移,以利用更多內存或功能集成。這種可擴展性允許開發人員在 S32K 系列上為其最終產品平臺進行標准化,從而最大限度地重複使用硬件和軟件並縮短上市時間。

以下是 S32K 系列 MCU 的一般特性:

• 具有符合 IEEE-754 標准的 FPU 的 32 比特 ARM Cortex-M4 內核,最高執行頻率為 112 MHz

• 可擴展內存占用空間,最高 2 MB 閃存和最高 256 KB SRAM

• 具有片上模擬比較器和多個 12 的精密混合信號能力比特 ADC

• 適用於電機控制、照明控制和車身應用等廣泛應用的强大定時器

• LPUART、LPSPI、LPI2C、FlexCAN、CAN-FD、FlexIO 等串行通信接口。

• 符合 SHE 規範的安全模塊

• 具有全功能閃存編程/擦除/讀取操作的單電源 (2.70–5.5 V)

• 符合 ISO26262 的功能安全,具有內部看門狗、電壓監視器、時鐘監視器、存儲器保護和 ECC

• 環境操作溫度範圍:–40 °C 至 125°C

• 軟件支持:S32 軟件開發套件 (SDK)、S32 Design Studio (S32DS)

2 S32K 系列比較

詳情請參考最新版參考手册。

3 電源

電源和接地引脚將在後續章節中介紹。

1. VDD 和 VDDA 必須短接到 PCB 上的公共參考。用於過濾電源噪聲的適當去耦電容

3.1 大容量和去耦電容

大容量電容充當電源引脚的本地電源,靠近去耦電容。最小化大容量電容器和去耦電容器之間的走線長度。

去耦電容使電源、MCU 和接地參考之間的電流環路盡可能短,以應對高頻瞬變和噪聲。因此,所有去耦電容應盡可能靠近其各自的電源引脚放置;去耦電容的接地側應該有一個通孔到焊盤,它直接向下連接到接地層。

電容器不應通過長走線連接到電源層。

4 時鐘電路

S32K1xx 具有以下時鐘源:

• 快速內部參考時鐘(FIRC):48 MHz。

• 慢速內部參考時鐘(SIRC):8 MHz。

• PLL:外部振蕩器作為輸入源。

• 外部方波輸入時鐘:高達 50 MHz。

• 外部振蕩器時鐘(OSC):4–40 MHz。

FIRC、SIRC 是內部的,不必從硬件設計的角度考慮。外部振蕩器的工作頻率範圍為 4–40 MHz。它提供了一個輸出時鐘,可以提供給 PLL 或用作某些外設的時鐘源。當使用外部振蕩器作為 PLL 的輸入源時,外部振蕩器的頻率範圍應為 8-40 MHz。

4.1 EXTAL 和 XTAL 引脚

這些引脚為晶體提供接口以控制內部時鐘發生器電路。 EXTAL 是晶體振蕩器放大器的輸入。 XTAL 是晶振放大器的輸出。皮爾斯振蕩器提供穩健、低噪聲和低功耗的外部時鐘源。它專為典型晶體振蕩器的最佳啟動裕量而設計。 S32K1xx 支持 4 MHz 至 40 MHz 的晶體或諧振器。EXTAL、XTAL 引脚的輸入電容為 7 pF。

負載電容取决於晶體的規格和電路板電容。建議讓晶體制造商評估 PCB 上的晶體。

4.2 振蕩電路PCB布局建議

晶體振蕩器是一個模擬電路,必須根據模擬板布局規則仔細設計:

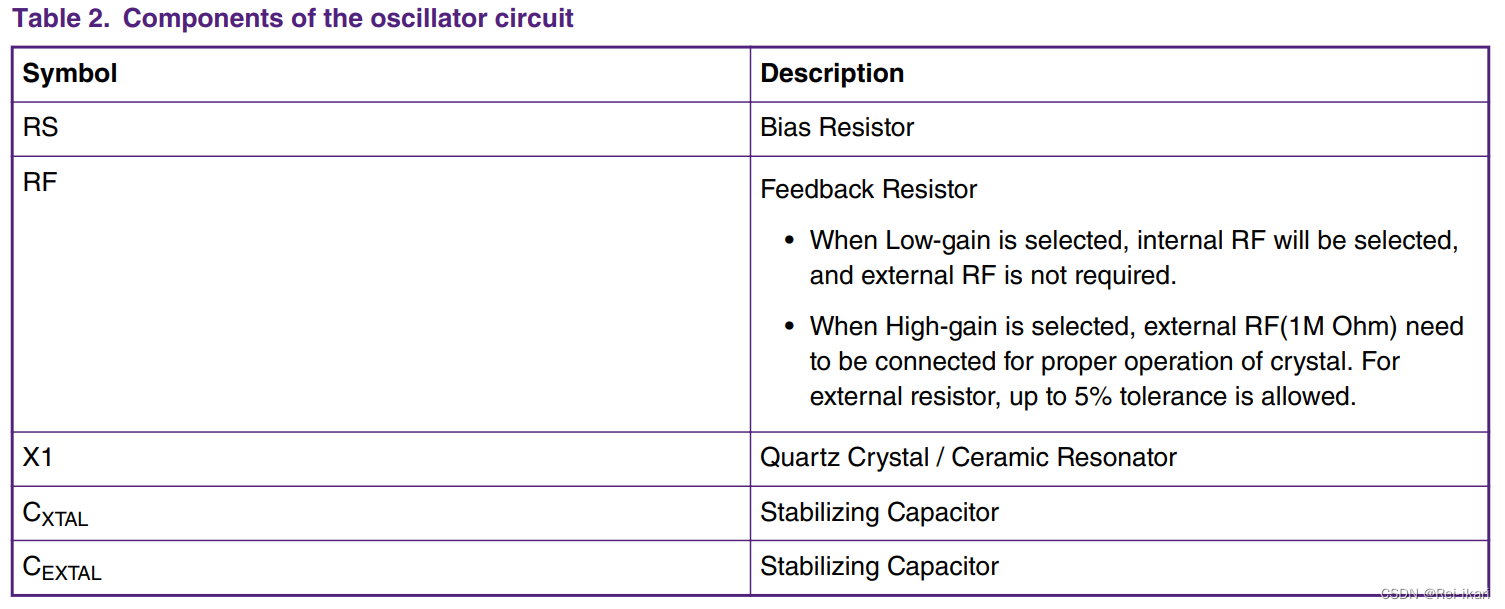

• 不需要外部反饋電阻 [Rf],因為它已經集成。

• 建議將PCB 發送給晶體制造商以確定負振蕩餘量以及CXTAL 和CEXTAL 電容的最佳值。數據錶包括對槽路電容器 CXTAL 和 CEXTAL 的建議。這些值連同預期的 PCB、引脚等雜散電容值應作為起點。

• XTAL/EXTAL 引脚、晶振和外部電容之間的信號走線必須盡可能短,不得使用任何過孔。這最大限度地减少了寄生電容以及對串擾和 EMI 的敏感性。在確定負載電容器的尺寸時,必須考慮信號走線的電容。

• 如果只有 1-2 個 PCB 層,建議在振蕩器組件周圍放置一個保護環,並將其連接到實心接地層。應在晶體振蕩器區域下方放置一個接地區域。該接地保護環必須是幹淨的接地。這意味著來自和流向其他設備的電流不應流過保護環。

該保護環應通過短走線連接到 S32K1xx 的 VSS x。切勿將接地保護環連接到板上的任何其他接地信號。還要避免實施接地回路。

• 主振蕩回路電流在晶振和負載電容之間流動。此信號路徑(晶振到 CEXTAL 到 CXTAL 到晶振)應盡可能短,並應具有對稱布局。因此,兩個電容器的接地連接應始終盡可能靠近。

• EXTAL 和XTAL 引脚只能連接到所需的振蕩器組件,不得連接到任何其他設備。

下圖 3 顯示了振蕩器布局的推薦布局和布線。

5 調試和編程接口

這裏顯示了一些常用的調試連接器。大多數 ARM 開發工具都使用這些引脚之一。

在開發您的 ARM 電路板時,建議使用標准調試信號排列,以便更輕松地連接到調試器。

SWD/SWV 引脚覆蓋在 JTAG 引脚之上,如下所示:

JTAG 信號的上拉/下拉電阻器包含在默認焊盤配置內部。請參閱器件參考手册和數據錶。

5.1 調試連接器引脚分配

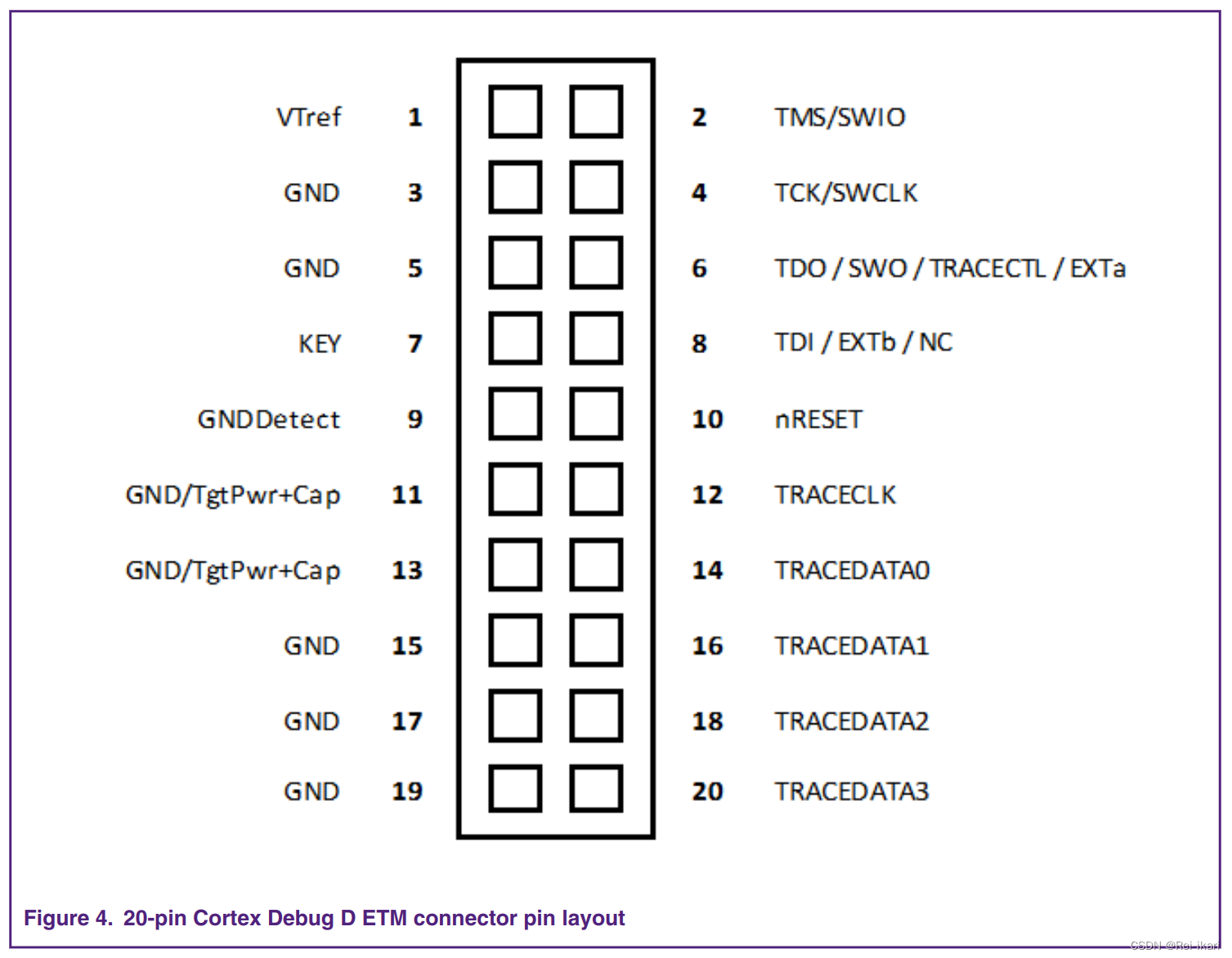

5.1.1 20 針 Cortex 調試 D ETM 連接器

一些較新的 ARM 微控制器板使用 0.05” 20 針接頭 (Samtec FTSH-110) 進行調試和跟踪。 (灰顯的信號在 Cortex-M3 或 Cortex-M4 上不可用。)20 針 Cortex Debug D ETM 連接器支持 JTAG 和串行線調試協議。當使用串行調試協議時,TDO 信號可用於串行線查看器輸出以進行跟踪捕獲。該連接器還提供了一個 4 比特寬的跟踪端口,用於捕獲需要更高跟踪帶寬的跟踪(例如,啟用 ETM 跟踪時)。

5.1.2 10 針 Cortex 調試連接器

對於沒有 ETM 的設備,您可以使用更小的 0.05” 10 針連接器 (Samtec FTSH-105) 進行調試。與 20 引脚 Cortex Debug D ETM 連接器類似,10 引脚版本支持 JTAG 和串行線調試協議。

5.1.3 傳統 20 針 IDC 連接器

ARM 開發板中常用的調試連接器是 20 針 IDC 連接器。 20 針 IDC 連接器排列支持 JTAG 調試、串行線調試(SWIO 和 SWCLK)、串行線輸出(SWO)。 nICEDETECT 引脚允許目標系統檢測是否連接了調試器。當沒有連接調試器時,該引脚被拉高。調試器連接將此引脚接地。這用於一些支持多種 JTAG 配置的開發板。 nSRST 連接是可選的;調試器可以通過系統控制塊 (SCB) 重置 Cortex-M 系統,因此這種連接通常在微控制器設計的頂層被忽略。

5.1.4 38 針 Mictor 連接器

在一些 ARM 系統設計中,當需要跟踪端口時使用 Mictor 連接器(例如,用於 ETM 的指令跟踪)。它也可用於 JTAG/SWD 連接。 20針IDC連接器可與Mictor連接器並聯(一次只使用一個)。

通常 Cortex-M3 或 Cortex-M4 微控制器只有 4 比特跟踪數據信號,因此 Mictor 連接器上的大多數跟踪數據引脚都沒有使用。 Mictor 連接器主要用於其他 ARM Cortex 處理器(CortexA8/A9、Cortex-R4)或在某些多處理器系統中,跟踪系統可能需要更寬的跟踪端口。在這種情况下,也將使用連接器上其他一些未使用的引脚。對於典型的 Cortex-M3 或 Cortex-M4 系統,建議使用 Cortex Debug D ETM 連接器。

5.2 複比特系統

複比特 MCU 提供了一種從一組已知的初始條件開始處理的方法。系統複比特從完全調節的片上穩壓器和來自內部參考的系統時鐘生成開始。

5.2.1 外部引脚RESET

對於所有複比特源,MCU 將RESET_B 引脚驅動為低電平至少128 個總線時鐘周期,直到閃存初始化完成。

閃存初始化完成後,釋放 RESET_B 引脚,內部芯片複比特甜點。保持 RESET_B 引脚在外部有效會延遲內部芯片複比特的否定。

在該器件上,RESET 是一個專用引脚。該引脚為漏極開路且具有內部上拉/上拉器件。斷言 RESET 將設備從任何模式喚醒。在引脚複比特期間,RCM 的 SRS[PIN] 比特被置比特。因此,應用軟件可以通過讀取該寄存器來檢測外部引脚 RESET。

如果閃存選項寄存器 (FTFC_FOPT) 中的 RESET_PIN_CFG 被清除,則 RESET_B 引脚在 POR 後被禁用並且不能作為複比特功能啟用。選擇此選項後,在 POR 斜坡期間可能會出現短暫的爭用,此時器件在建立此選項的設置並釋放引脚上的複比特功能之前將引脚驅動為低電平。 RESET 引脚與標准 GPIO 相同。它可以作為偽開漏輸出運行,因為輸出級中還有一個 PMOS 器件。

該比特通過系統複比特和低功耗模式保留。當 RESET_B 引脚功能被禁用時,它不能用作低功耗模式喚醒的源。

注意 當通過 FSEC 寄存器禁用複比特引脚並啟用安全性時,只能通過設置 MDM-AP 寄存器中的整體擦除和系統複比特請求字段來執行整體擦除。

複比特線有一個內部上拉電阻。如果環境和客戶應用程序嘈雜,可以添加一個外部上拉電阻(介於 10KOhmshms-100KOhms 之間)以避免發生偶發或意外複比特。有關內部上拉電阻值的值,請參閱器件數據錶。

盡管 MCU 並不直接需要複比特線中的電容器。在某些情况下,為了增加進一步的 ESD 保護,需要在 RESET 引脚與地之間添加一個外部電容。必須根據應用的設計要求選擇上拉電阻和電容的值。有關 MCU 可以檢測到的最小 RESET 脈沖值,請參閱器件數據錶。

6 模擬比較器接口

比較器 (CMP) 模塊提供了一個電路,用於比較 S32K1xx 微控制器中的兩個模擬輸入電壓。比較器電路設計為在整個電源電壓範圍內運行,稱為軌到軌運行。 CMPO 在同相輸入大於反相輸入時為高電平,當同相輸入小於反相輸入時為低電平。

由於 MCU 引脚之間的電感/電容耦合,高速接口或任何 GPIO 的切換可能會給模擬或比較器輸入引入一些噪聲。串擾可能由彼此靠近或彼此交叉的 PCB 走線引入。為了避免和减輕高頻噪聲和任何耦合。請確保模擬比較器輸入信號阻抗為 50K 或更低。(參見第 12 頁的圖 9)

將接地層和形狀與敏感的模擬信號放在一起可以在 PCB 上提供屏蔽。應注意盡量减少 PCB 上這些類型信號的路徑長度。這可以防止幹擾和 I/O 串擾影響信號。由於大而扁平的導體圖案,大量金屬具有盡可能低的電阻和盡可能低的電感。接地層充當低阻抗返回路徑,用於去耦由快速數字邏輯引起的高頻電流。它還可以最大限度地减少電磁幹擾/射頻幹擾 (EMI/RFI) 的輻射。另一方面,接地層還允許通過傳輸線(微帶線或帶狀線)技術傳輸高速數字或模擬信號,其中需要受控阻抗。

7 通訊模塊

7.1 LPUART 模塊的LIN 接口

本地互連網絡(LIN) 是一種串行通信協議,旨在支持汽車網絡。作為分層網絡的最低級別,當不需要 CAN 的所有功能時,LIN 可以與傳感器和執行器進行經濟高效的通信。

LPUART 模塊的特性支持並包括:

• LIN 主機和從機操作

• 全雙工、標准不歸零 (NRZ) 格式

• 可編程波特率(13 比特模分頻器),可配置的過采樣率從4倍到32倍

• 發送和接收波特率可以與總線時鐘异步運行:

— 波特率可以獨立於總線時鐘頻率進行配置

— 支持在停止模式下運行

• 中斷、DMA 或輪詢操作:

— 發送數據寄存器為空且發送完成

— 接收數據寄存器已滿

— 接收溢出、奇偶校驗錯誤、幀錯誤和噪聲錯誤

— 空閑接收器檢測

— 接收引脚上的有效邊沿

— 支持 LIN 的中斷檢測

—接收數據匹配

• 硬件奇偶校驗生成和檢查

• 可編程 7 比特、8 比特、9 比特或 10 比特字符長度

• 可編程 1 比特或 2 比特停止比特

• 三種接收器喚醒方法:

— 空閑線喚醒

—地址標記喚醒

— 接收數據匹配

• 自動地址匹配以减少 ISR 開銷:

— 地址標記匹配

— 空閑行地址匹配

— 地址匹配開始,地址匹配結束

• 可選 13 比特中斷字符生成/11 比特中斷字符檢測

• 可配置空閑長度檢測支持 1、2、4、8、16、32、64 或 128 個空閑字符

• 可選擇發送器輸出和接收器輸入極性

• 硬件流控制支持請求發送 (RTS) 和清除發送 (CTS) 信號

• 具有可編程脈沖寬度的可選 IrDA 1.4 歸零反轉 (RZI) 格式

• 用於發送和接收的獨立 FIFO 結構

— 用於接收和發送請求的單獨可配置水印

如果接收 FIFO 不為空,則接收器在可配置數量的空閑字符後斷言請求的選項。

LIN 總線拓撲使用單個主機和多個節點,如下所示。將應用程序模塊連接到車輛網絡使它們可用於診斷和服務。

LIN 發送器是具有電流限制和過流發送器關斷功能的低端 MOSFET。集成了具有串聯二極管結構的可選內部上拉電阻,因此從節點中的應用無需外部上拉元件。要用作主節點,必須在 VBAT [電池電壓] 和 LIN 總線之間並聯一個與二極管串聯的 1 kΩ 外部電阻器。從隱性到顯性的下降時間和從顯性到隱性的上昇時間是可選擇和控制的,以保證通信質量並减少 EMC 輻射。

7.1.1 LIN 組件數據

| 參考 | 部分 | 安裝 | 注釋 |

| DMLIN | 二極管 | 僅對主 ECU 强制 | 從 LIN 到 VSUP 的反極性保護 |

| RML1 和 RML2 | 電阻:2 kΩ 功率損耗:250 mW 容差:1% 封裝尺寸:1206 要求:整個主終端的最小額定功率必須 ≥ 500 mW | 僅對主 ECU 强制 | 對於主 ECU 如果並聯使用超過 2 個電阻,則必須以 1 kΩ 的總電阻 RM 和整個主終端的最小功率損耗的方式選擇這些值。 對於從 ECU RMLIN1 和 RMLIN2 在 PCB 布局上不需要 |

| C1 | 電容: 從 ECU:通常為 220 pF 主 ECU:從 560 pF 到從節點 [CSLAVE] 中的值的大約十倍,因此總線路電容較少依賴從節點的數量。 封裝尺寸:0805 電壓:≥50 V | 强制 | 必須以滿足 LIN 規範的方式選擇主節點的值。 |

| C2 | 電容: 封裝尺寸:0805 | 可選 | 只有在獲得相應 OEM 的明確書面許可時才允許安裝可選部件。 靠近連接器放置。 |

| ESD1 | ESD保護 封裝尺寸:0603-0805 | 可選 | 用於額外 ESD 保護部件的布局焊盤。 只有在獲得相應 OEM 的明確書面許可時才允許安裝可選部件。 靠近連接器放置。 |

7.2 FlexCAN 模塊的CAN 接口

CAN 的物理層特性在ISO-11898-2 中規定。本標准規定了使用標稱阻抗為 120 Ω(最小為 95 Ω,最大為 140 Ω)的平行線組成的電纜。出於電磁兼容性 (EMC) 的原因,通常需要使用屏蔽雙絞線電纜,盡管 ISO-11898-2 也允許使用非屏蔽電纜。數據速率為 1 Mb 時,CAN 的最大線路長度為 40 米。然而,在較低的數據速率下,可能更長的線路是可能的。 ISO-11898-2 指定了線拓撲,各個節點使用短存根連接。

雖然並非專門用於汽車應用,但 CAN 協議旨在滿足車輛串行數據總線的特定要求:實時處理、車輛 EMI 環境中的可靠運行、成本效益和所需帶寬。

每個 CAN 站通過收發器設備物理連接到 CAN 總線。該收發器能够驅動 CAN 總線所需的大電流,並具有針對缺陷 CAN 或缺陷站的電流保護。帶有 S32K1xx 微控制器的典型 CAN 系統如圖 13 所示。第 17 頁

FlexCAN 模塊是 CAN 協議規範、具有靈活數據速率 (CAN FD) 協議的 CAN 和 CAN 2.0 版本 B 協議的完整實現,它支持標准和擴展消息幀以及高達 64 字節的長有效載荷,以更快的速度傳輸速率高達 8 Mbps。消息緩沖區存儲在專用於 FlexCAN 模塊的嵌入式 RAM 中。關於芯片中配置的報文緩沖區數量,請參見參考手册中的芯片配置詳細信息。

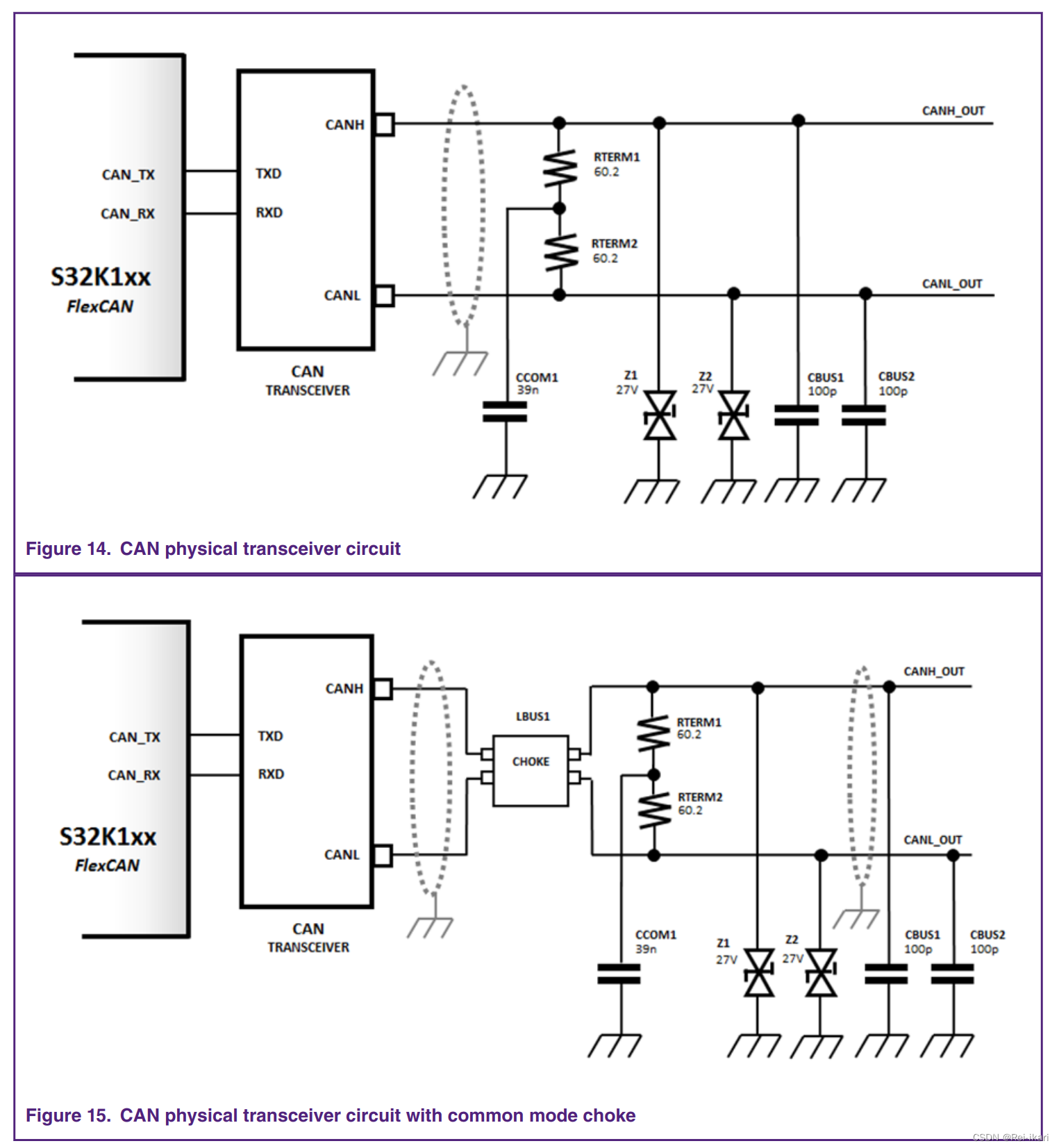

與大多數其他 CAN 物理收發器一樣,CANH、CANL 和 SPLIT 引脚可供設計人員根據應用端接總線。第 18 頁的圖 14. 和第 18 頁的圖 15. 顯示了 CAN 節點終端的示例。

7.2.1 CAN 組件數據

| 參考 | 描述 |

| 錶示高速/中速軌道旁邊的保護軌道。 連接保護軌道,使軌道的每一端都接地。至少每 500 mil 應將保護軌道連接到接地層。與任何受保護導體和防護軌道的間距不得超過 20 密耳。 |

| CBUS1 和 CBUS2 | 電容器 CBUS1 和 CBUS2 不是特別需要的。出於 EMC 原因,可能會添加它們,在這種情况下,從任一總線到地的最大電容總和不得超過 300 pF。如果還需要齊納堆棧,則齊納堆棧的寄生電容也必須包含在總電容預算中。 |

| Z1 和 Z2 | 齊納堆疊 Z1 和 Z2 可能需要滿足汽車 EMC 要求(尤其是 ESD)。這些設備應靠近連接器放置。 |

| RTERM1、RTERM2 和 CCOM1 | 根據 CAN 網絡中節點的比特置,它可能需要特定的終端。 RTERM1、RTERM2 和 CCOM1 必須是它們有助於獲得總電纜阻抗。在 CAN 網絡的總線實現中,只有總線兩端的兩個節點具有終端電阻。未放置在 CAN 總線末端的節點沒有終端。需要進行徹底的分析以維持 CAN 網絡的這一要求。 收發器上的 SPLIT 引脚是可選的,設計人員可能會選擇不使用它。該引脚有助於穩定 CAN 總線的隱性狀態,並可在需要時通過軟件啟用或禁用。 |

| LBUS1——共模扼流圈 | CANH 和 CANL 線路上的共模扼流圈有助於减少耦合電磁幹擾,滿足汽車 EMC 要求。該扼流圈與收發器引脚上的瞬態抑制器一起可以大大降低耦合電磁噪聲和高頻瞬態。 LBUS1 不是特別需要的。 |

7.2.2 CAN 終端

在傳輸線中,有兩條電流路徑,一條將電流從驅動器傳送到接收器,另一條提供返回驅動器的返回路徑。 CAN 傳輸線更複雜,因為有兩個信號共享一個公共端接和一個接地返回路徑。對於可靠的 CAN 通信,傳輸線中的反射必須盡可能小。這只能通過適當的電纜端接來完成。第 20 頁的圖 16 和第 20 頁的圖 17 演示了兩種 CAN 終端方案。

在信號轉換期間和之後,反射發生得非常快。在長線上,反射更有可能持續足够長的時間以導致接收器誤讀邏輯電平。在短線上,反射發生得更快,並且對接收到的邏輯電平沒有影響。

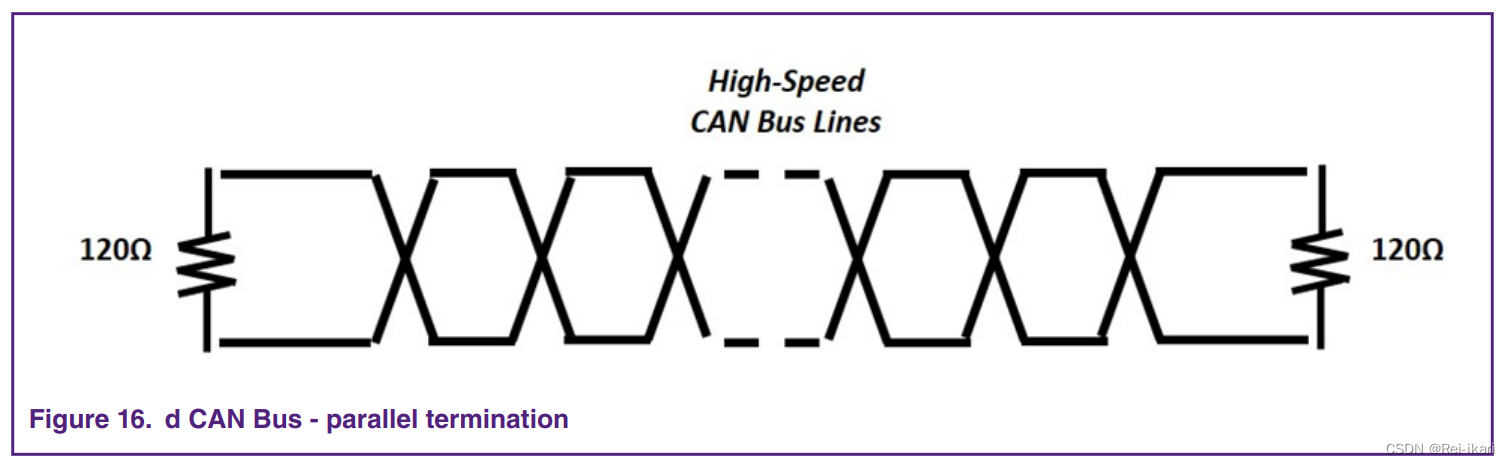

7.2.2.1 並行端接

在CAN 應用中,總線的兩端都必須端接,因為總線上的任何節點都可以發送/接收數據。鏈路的每一端都有一個與電纜的特性阻抗相等的端接電阻,盡管端接電阻的推薦值通常為 120 Ω(最小為 100 Ω,最大為 130 Ω)。

無論連接了多少節點,網絡中的終端電阻都不應超過兩個,因為額外的終端會給驅動器帶來額外的負載。 ISO-11898-2 建議不要將終端電阻器集成到節點中,而是在總線的最遠端連接獨立的終端電阻器。這是為了避免在包含該電阻器的節點斷開時丟失端接電阻器。該概念也適用於避免將兩個以上的終端電阻器連接到總線,或將終端電阻器放置在總線的其他點而不是兩端。

7.2.2.2 帶有共模濾波的並聯端接

為了進一步提高信號質量,將兩端的端接電阻一分為二,並在兩個電阻之間放置一個濾波電容 CSPLIT。這可以過濾來自總線的不需要的高頻噪聲並减少共模輻射。

7.3 集成電路間IIC

內部集成電路 (IIC) 總線是一種兩線雙向串行總線,它提供了一種簡單、有效的設備間數據交換方法。作為兩線設備,IIC 總線最大限度地减少了對設備之間大量連接的需求,並消除了對地址解碼器的需求。該總線適用於需要在多個設備之間偶爾進行短距離通信的應用。它還提供了靈活性,允許將其他設備連接到總線以進行進一步擴展和系統開發。 SDA 和 SCL 都是雙向線,通過上拉電阻連接到正電源電壓(參見第 21 頁的圖 18。當總線空閑時,兩條線都為高電平。連接到總線的設備的輸出級必須具有開漏或開集以執行線與功能。該接口設計為在最大總線負載和時序下以高達 100 kbps 的速度運行。該器件能够以更高的波特率運行,最高可達最大值時鐘/20, 减少總線負載. 最大通信長度和可以連接的設備數量受最大總線電容 400 pF 的限制。

7.4 以太網MAC 接口

MII/RMII 接口信號可以直接路由到MAC-NET 接口,但是為了抑制EMI,可以考慮在RXCLK、TXCLK 和所有RX/TX 信號上串聯終端電阻。 MII/RMII 系列終端應放置在距離以太網物理接口 100 以內,並路由到不間斷的參考平面。 33-50 歐姆串聯端接電阻器一直是改善 EMI 的良好推薦值。

盡管 RMII 和 MII 是同步總線架構,但仍有許多因素限制了信號走線長度。走線越長,信號在目的地的衰减越大,因此更容易受到噪聲幹擾。較長的走線也可用作天線,如果在錶層運行,則會增加 EMI 輻射。如果長迹線在噪聲信號附近或附近運行,則不需要的信號可能會作為串擾耦合進來。建議使信號走線長度盡可能短。理想情况下,將痕迹保持在 6 英寸以下。還建議在 MII 或 RMII 總線上將走線長度匹配到 2.0 英寸以內。迹線長度的顯著差异可能導致數據時序問題。在整個設計過程中盡量减少過孔的使用。過孔為信號迹線增加電容。與任何高速數據信號一樣,良好的設計實踐要求在整個數據路徑中保持阻抗並避免短截線。

MII 信令:第 23 頁的圖 20 顯示了 MII 接口中的 PHY-MAC 和 MAC-MAC 連接。數據通過 4 比特寬的數據半字節 TXD[3:0] 和 RXD[3:0] 進行交換。數據傳輸與發送 (TX_CLK) 和接收 (RX_CLK) 時鐘同步。對於 PHY-MAC 接口,兩個時鐘信號均由 PHY 提供,並且通常源自以標稱 25 MHz 運行的外部晶振或開關上的 CLK_OUT 信號。當以太網交換機配置為 MAC-MAC 通信時,交換機提供時鐘並像 PHY 一樣工作。

RMII 信令:RMII 數據通過 2 比特數據信號 TXD[1:0] 和 RXD[1:0] 進行交換,如第 23 頁上的圖 21 所示。

發送和接收信號與共享參考時鐘 REF_CLK 同步。

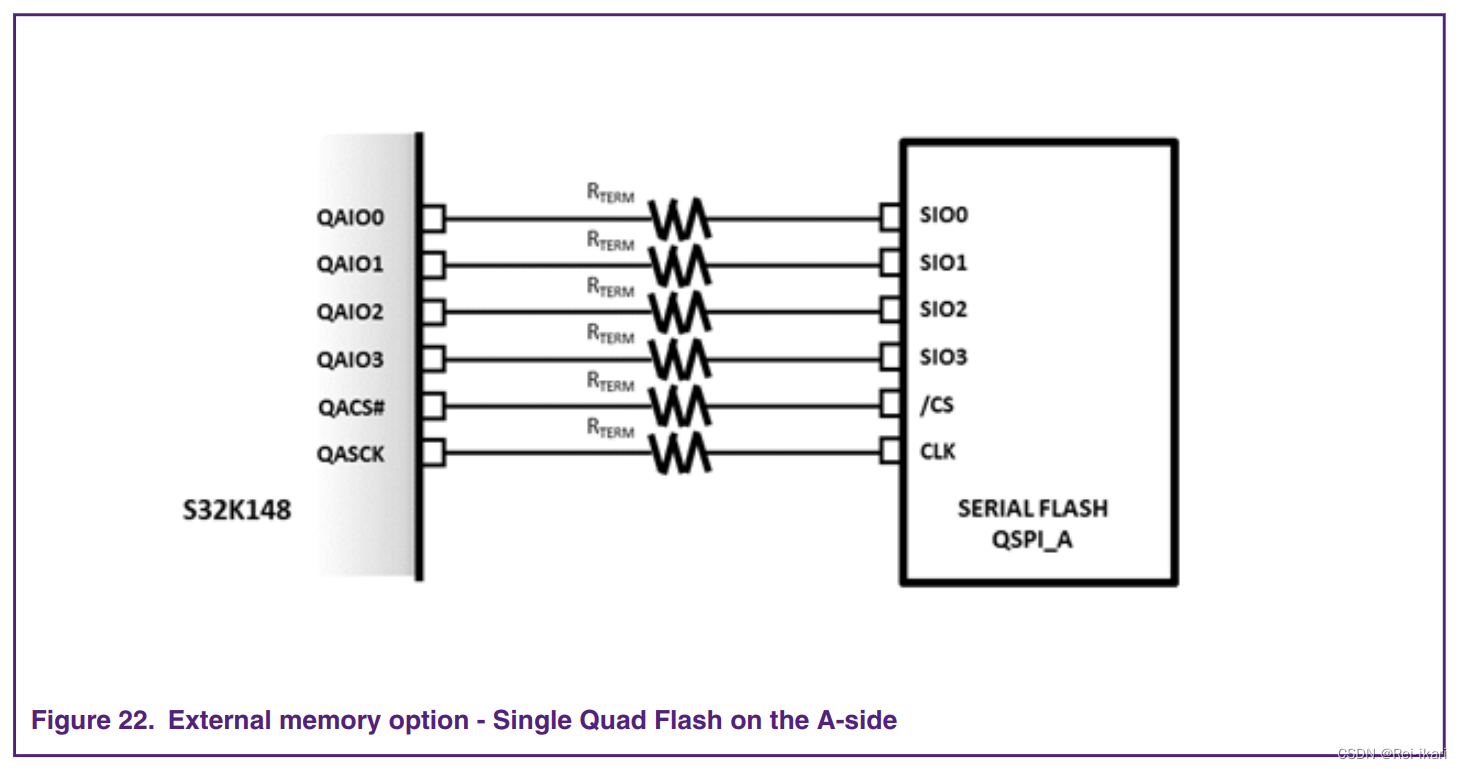

8 Quad 串行外設接口

S32K1xx 有一個 QuadSPI 實例。 Quad Serial Peripheral Interface (QuadSPI) 模塊用作外部串行閃存設備的接口。它分別支持多達 4 條和 8 條雙向數據線的 SDR 和 HyperRAM 模式。 QuadSPI 支持 A 側和 B 側。 QuadSPI 的 A 側連接到快速焊盤 (80 mA),而 B 側連接到 20 mA 焊盤。請參閱數據錶了解操作值。

在任何給定的應用程序中只支持一個外部存儲器,並且不允許同時運行 QuadSPI 的 A 側和 B 側。因此,可以支持以下外部存儲器選項:

• A 側的單 Quad Flash

• B 側的單個 HyperRAM

• B 側的單個 Quad Flash。

數據和時鐘信號終止:隨著微處理器的速度和性能提高到更高的極限,時鐘的生成和分配變得更加困難。需要受控和精確的時鐘分配技術來維持同步系統。時鐘信號質量和偏差是分配時鐘信號的兩個主要問題。在更高的頻率和相關的快速邊沿速率下,長走線錶現得像傳輸線。由於傳輸線端接不良,會出現回鈴、過沖和下沖。它們會導致信號質量差、切換錯誤,並且在極端情况下會造成損壞。

鑒於 25-33 歐姆的有效輸出驅動器强度和 50 歐姆的傳輸線特性阻抗,應在輸出驅動器附近添加終端電阻,以最大限度地减少反射,如下所示。

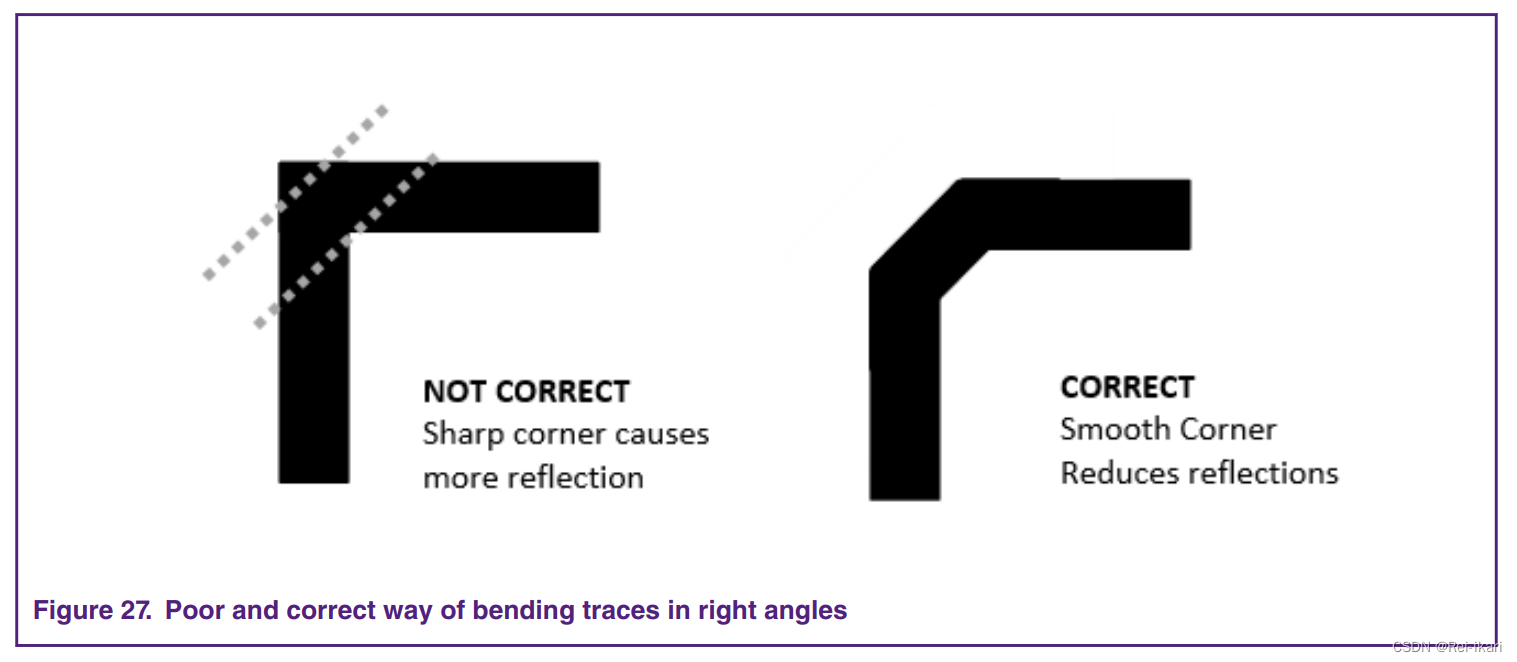

數據信號路由:為了保持從微控制器到 IC 存儲器的數據傳輸的正確時序,PCB 數據走線應與從微控制器到 IC 存儲器的時鐘走線具有相同的長度和時間延遲。數據信號應使用受控阻抗走線進行布線,以减少信號反射。避免使用 90° 角的布線走線。建議當走線需要改變方向時,切掉拐角並平滑走線。為了進一步提高信號完整性,請避免使用多個信號層進行數據信號路由。所有的信號走線都應該有一個連續且堅固的參考平面,可以是 GND 或 VDD。

時鐘信號路由:在高速同步數據傳輸中,PCB 設計中良好的信號完整性至關重要,尤其是對於時鐘信號、SCLK 和 DQS。在路由時鐘信號時,應特別注意。建議采用以下做法。

• 運行時鐘信號至少-w3w 的迹線寬度,使其遠離所有其他信號迹線。這有助於保持時鐘信號免受串擾噪聲的影響。

• 對整個時鐘信號路徑使用盡可能少的過孔。過孔會引起阻抗變化和信號反射。

• 所有的信號走線都應該有一個堅實的參考平面,無論是GND 還是VCC。

• 盡可能筆直地運行時鐘走線,避免使用蛇形布線。

• 在下一層保持一個連續的地面作為參考平面。

• 使用受控阻抗布線時鐘走線。

• 通過使用更寬的間距將時鐘信號與其他信號分開,以防止時鐘信號受到幹擾或串擾。數據總線應以與時鐘參考相匹配的長度布線。建議匹配長度在± 50 mils 以內。

9 未使用的引脚

未使用的數字和模擬引脚必須懸空。在軟件中,應用程序應確保 MCU 的端口功能為“禁用”。 DISABLED 功能是所有未初始化引脚的默認狀態。

10 一般電路板布局指南

10.1 走線建議

走線中的直角會導致更多輻射。拐角區域的電容增加,特性阻抗發生變化。這種阻抗變化會引起反射。避免走線中的直角彎曲,並嘗試使用至少兩個 45° 角進行布線。為了盡量减少任何阻抗變化,最好的布線是圓彎,如圖 27. (第 27 頁)所示。

為了最大限度地减少串擾,不僅在一層上的兩個信號之間,而且在相鄰層之間,將它們彼此布線為 90°。

複雜板子布線時需要使用過孔;使用它們時必須小心。這些增加了額外的電容和電感,並且由於特性阻抗的變化而發生反射。過孔也會增加走線長度。使用差分信號時,在兩條迹線中使用過孔或補償另一條迹線中的延遲。

10.2 接地

接地技術適用於多層和單層 PCB。接地技術的目標是最小化接地阻抗,從而降低從電路返回到電源的接地回路的電比特。

• 將高速信號布線在堅固且完整的接地層之上。

• 不要將接地層分成模擬、數字和電源引脚的單獨層。建議使用單個連續接地層。

• 在靠近微控制器引脚的任何區域附近不應有任何類型的浮動金屬/形狀。在信號平面的未使用區域填充銅,並通過通孔將這些銅連接到接地平面。

10.3 EMI/EMC 和 ESD 布局注意事項

這些注意事項對於所有系統和電路板設計都很重要。盡管這背後的理論得到了很好的解釋,但每個電路板和系統都以自己的方式體驗到這一點。涉及到許多與 PCB 和組件相關的變量。

本應用筆記不涉及電磁理論或解釋用於對抗效應的不同技術的原因,但它考慮了最推薦應用於 CMOS 電路的效應和解决方案。 EMI 是幹擾電子設備運行的射頻能量。這種射頻能量可以由設備本身或附近的其他設備產生。為您的系統研究 EMC 可以測試您的系統成功運行的能力,以抵消來自其周圍設備和系統的計劃外電磁幹擾的影響。電磁噪聲或幹擾通過兩種介質傳播:傳導和輻射。

設計考慮範圍縮小到:

• 電路板的輻射和傳導 EMI 應低於您所遵循的標准所允許的水平。

• 電路板能够成功抵消來自其周圍其他系統的輻射和傳導電磁能 (EMC)。

系統的 EMI 源由多個組件組成,例如 PCB、連接器、電纜等。 PCB 在輻射高頻噪聲方面起著主要作用。在更高的頻率和快速切換的電流和電壓下,PCB 走線成為輻射電磁能量的有效天線;例如,一個大的信號環路和相應的接地。五個主要輻射源是:在迹線上傳播的數字信號、電流返回環路區域、電源濾波或去耦不足、傳輸線效應以及電源和接地層不足。快速開關時鐘、外部總線和 PWM 信號用作控制輸出和開關電源。電源是 EMI 的另一個主要貢獻者。 RF 信號可以從電路板的一個部分傳播到另一部分,從而形成 EMI。開關電源輻射的能量可能無法通過 EMI 測試。這是一個龐大的主題,有許多書籍、文章和白皮書詳細介紹了其背後的理論以及對抗其影響的設計標准。

就 EMI/EMC 和 ESD 問題而言,每個電路板或系統都是不同的,需要自己的解决方案。

但是,减少不必要的電磁能量產生的通用准則如下所示:

• 確保電源的額定值適合應用並使用去耦電容器進行了優化。

• 在電源上提供足够的濾波電容。大容量/旁路和去耦電容應具有低等效串聯電感 (ESL)。

• 如果布線層上有可用空間,則創建地平面。使用過孔將這些接地區域連接到接地層。

• 使電流回路盡可能小。添加盡可能多的去耦電容。始終應用當前的返回規則以减少循環區域。

• 使高速信號遠離其他信號,尤其是遠離輸入和輸出端口或連接器。

11 PCB 層堆疊

為了達到信號完整性和性能要求,建議至少使用四層 PCB 來實現以太網應用和系統。對於四層、六層和八層板,建議使用以下疊層,盡管其他選項也是可能的。

12 注入電流

所有引脚均采用保護二極管,可防止靜電放電 (ESD)。在許多情况下,數字和模擬引脚都需要連接到高於器件引脚工作電壓的電壓。除了提供 ESD 保護外,這些二極管結構還將電壓鉗比特到高於該引脚段電源的二極管壓降。這是允許的,只要電流注入按照設備規範中的定義進行限制。可以通過在信號上添加一個串聯電阻來限制電流。只要低於最大注入電流規格,輸入保護二極管就會將引脚上的電壓保持在安全水平(根據器件的絕對最大額定值)。

如需更多參考,請參閱 AN4731。

13 參考

• 晶體振蕩器故障排除指南 - NXP Semiconductors

• AN2049 晶體反饋的一些特性和設計說明 ...

• AN10853 IC 的 ESD 和 EMC 靈敏度 - NXP Semiconductors

• AN2321:板級電磁兼容性設計 - NXP Semiconductors

• AN10897 ESD 和 EMC 設計指南

边栏推荐

- Flink 系例 之 TableAPI & SQL 与 MYSQL 数据查询

- TypeScript:const

- DirectX修复工具V4.1公测![通俗易懂]

- APK签名原理

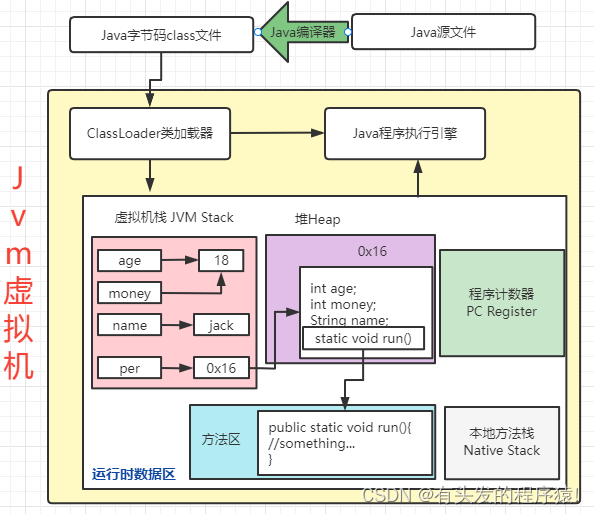

- JVM second conversation -- JVM memory model and garbage collection

- Configuration of ZABBIX API and PHP

- Mongodb second call -- implementation of mongodb high availability cluster

- MySQL service is starting. MySQL service cannot be started. Solution

- openssl客户端编程:一个不起眼的函数导致的SSL会话失败问题

- The first word of JVM -- detailed introduction to JVM and analysis of runtime data area

猜你喜欢

【ROS进阶篇】第五讲 ROS中的TF坐标变换

如何实现时钟信号分频?

The first word of JVM -- detailed introduction to JVM and analysis of runtime data area

Word2vec yyds dry goods inventory

Markdown编辑器使用基本语法

What are the books that have greatly improved the thinking and ability of programming?

JS中箭头函数和普通函数的区别

《QT+PCL第六章》点云配准icp系列2

Rearrangement of overloaded operators

Junda technology indoor air environment monitoring terminal PM2.5, temperature and humidity TVOC and other multi parameter monitoring

随机推荐

DirectX repair tool v4.1 public beta! [easy to understand]

JVM第二话 -- JVM内存模型以及垃圾回收

如何实现时钟信号分频?

opencv学习笔记六--图像拼接

Rearrangement of overloaded operators

opencv学习笔记五--文件扫描+OCR文字识别

[advanced ROS] lesson 5 TF coordinate transformation in ROS

Flink 系例 之 TableAPI & SQL 与 MYSQL 分组统计

tensorflow2-savedmodel convert to pb(frozen_graph)

Junda technology indoor air environment monitoring terminal PM2.5, temperature and humidity TVOC and other multi parameter monitoring

写在Doris毕业后的第一天

炎炎夏日,这份安全用气指南请街坊们收好!

Demand prioritization method based on value quantification

The first technology podcast month will be broadcast soon

How to realize clock signal frequency division?

Tableapi & SQL and Kafka message acquisition of Flink example

JS中箭头函数和普通函数的区别

Some thoughts on software testing

音乐播放器开发实例(可毕设)

职场太老实,总被欺负怎么办?