当前位置:网站首页>FPGA - 7系列 FPGA SelectIO -03- 逻辑资源之ILOGIC

FPGA - 7系列 FPGA SelectIO -03- 逻辑资源之ILOGIC

2022-06-21 05:57:00 【Vuko-wxh】

前言

本文主要翻译节选自UG471,主要对7系列FPGA SelectIO逻辑资源进行简要介绍,然后介绍了内部的SelectIO逻辑资源的ILOGIC 资源。

SelectIO逻辑资源简介

7 系列 FPGA 包含来自之前系列的 Xilinx FPGA 的基本 I/O 逻辑资源。 这些资源包括:

- Combinatorial input/output,组合输入/输出。

- 3-state output control,三态输出控制。

- Registered input/output,寄存输入/输出。

- Registered 3-state output control,寄存三态输出控制。

- Double-Data-Rate (DDR) input/output,双倍数据速率 (DDR) 输入/输出。

- DDR output 3-state control,DDR 输出三态控制。

- IDELAY provides users control of an adjustable, fine-resolution delay taps,IDELAY 为用户提供可调节、高分辨率延迟抽头的控制 。

- ODELAY provides users control of an adjustable, fine-resolution delay taps,ODELAY 为用户提供可调节、高分辨率延迟抽头的控制。

- SAME_EDGE output DDR mode,SAME_EDGE 输出 DDR 模式。

- SAME_EDGE and SAME_EDGE_PIPELINED input DDR mode,SAME_EDGE 和 SAME_EDGE_PIPELINED 输入 DDR 模式。

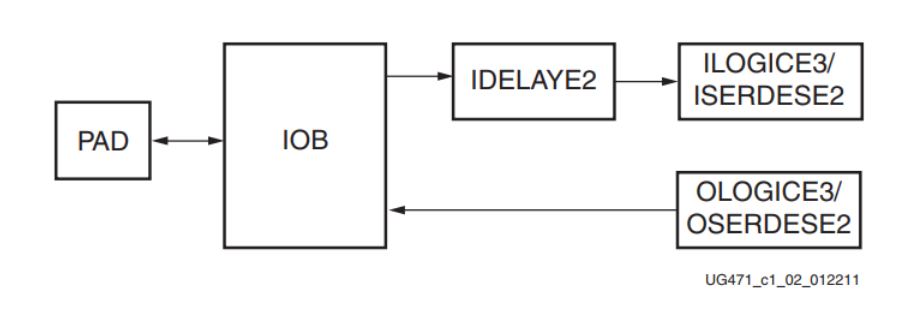

下图显示了用于 1.8V HP BANK。

下图显示了 3.3V HR bank 的 I/O 块。

SelectIO输入、输出和三态驱动器位于输入/输出缓冲器 (IOB) 中。 HP bank 具有单独的 IDELAY 和 ODELAY 块。 除了 ODELAY 块之外,HR bank 具有与 HP bank 相同的逻辑元素。

ILOGIC 资源

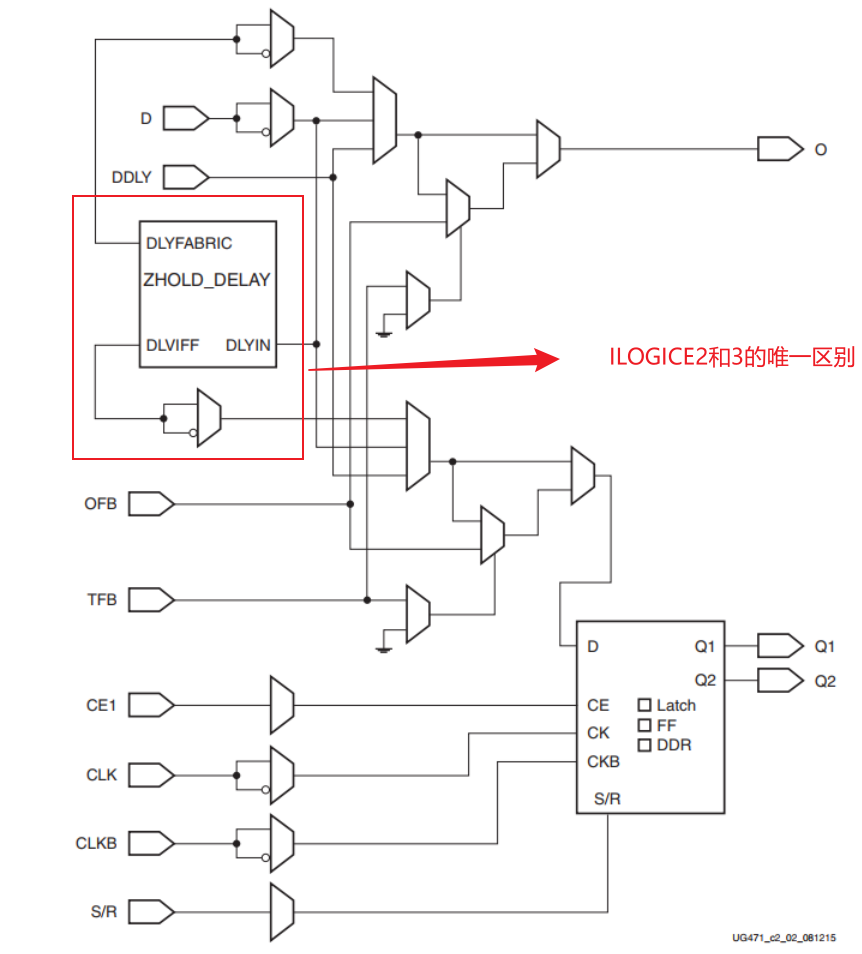

ILOGIC 块位于 I/O 块 (IOB) 旁边。ILOGIC 块包含用于在数据通过 IOB 进入 FPGA 时捕获数据的同步元素。 7 系列器件中 ILOGIC 配置的可能情况是 ILOGICE2(HP I/O bank)和 ILOGICE3(HR I/O bank)。但除非明确说明,否则 ILOGICE2 和 ILOGICE3 在功能上是相同的,它们的端口也是如此。 ILOGICE2 和 ILOGICE3 之间的唯一区别是:

- ILOGICE3 位于 HR 组中,并具有零保持延迟元件 (ZHOLD,zero hold delay element )。

- ILOGICE2 位于HP bank 中并且没有 ZHOLD元件。

这些差异如下图 2-3 和图 2-4 所示。 输入/输出互连 (IOI) 存储元件的 D 输入处的 ZHOLD 延迟消除了任何焊盘到焊盘保持时间要求。 ZHOLD 延迟与内部时钟分配延迟自动匹配,使用时可确保焊盘到焊盘保持时间为零。 ILOGIC 模块在输入端支持可选的静态无补偿零保持 (ZHOLD) 延迟线,以补偿时钟插入延迟。 当时钟路径直接来自同一 bank 或相邻 bank 中的 BUFG/BUFGCE 时,ZHOLD 功能经过优化以补偿时钟插入延迟。 ZHOLD 默认启用,除非时钟源是 MMCM 或 PLL,或者除非在 Xilinx 设计约束 (XDC) 中设置了 IOBDELAY 属性。

ZHOLD 可能不适用于所有应用,因此请查阅时序报告以验证对特定时钟方案的影响。

ILOGICE2 和 ILOGICE3 不是原语,因为它们不能被实例化。它们在布局和布线之后包含用户实例化的元素,例如输入触发器 (IFD) 或输入 DDR 元素 (IDDR)。

ILOGICE2 框图

ILOGICE3 框图

ILOGIC 可以支持以下操作:

- 边沿触发的 D 型触发器 。

- IDDR 模式(OPPOSITE_EDGE 或 SAME_EDGE 或 SAME_EDGE_PIPELINED)。

- 电平敏感锁存器。

- 异步/组合

ILOGIC 模块寄存器有一个公共时钟使能信号(CE1),默认为高电平有效。 如果未连接,任何存储元件的时钟使能引脚默认为活动状态。ILOGIC 块寄存器具有通用的同步或异步置位和复位(SR 信号)。设置/复位输入引脚 SR 强制存储元件进入 SRVAL 属性指定的状态。 复位条件优于设置条件。可以为 ILOGIC 块中的每个存储元素单独设置 SRVAL 属性,但不能为 ILOGIC 块中的每个存储元素单独设置同步或异步设置/重置 (SRTYPE) 的选择。以下部分讨论 ILOGIC 块中的各种资源。

组合输入路径

组合输入路径用于创建从输入驱动器到 FPGA 逻辑的直接连接。 在以下情况下,软件会自动使用此路径:

- 从输入数据到 FPGA 逻辑中的逻辑资源存在直接连接,未经过寄存。

- pack I/O register/latch into IOBs软件映射指令设置为OFF。

输入 DDR (IDDR)

概述

7 系列器件在 ILOGIC 模块中具有专用寄存器,用于实现输入双倍数据速率 (DDR) 寄存器。 **此功能通过实例化 IDDR 原语来使用。**输入 I/O 块的所有时钟都是完全多路复用的,即 ILOGIC 和 OLOGIC 块之间没有时钟共享。

IDDR 原语支持以下操作模式:

- OPPOSITE_EDGE 模式

- SAME_EDGE 模式

- SAME_EDGE_PIPELINED 模式

这些模式允许设计人员将下降沿数据传输到 ILOGIC 模块内的上升沿域,从而节省 CLB 和时钟资源,并提高性能。 这些模式是使用 DDR_CLK_EDGE 属性实现的。 以下部分详细介绍了每种模式。

OPPOSITE_EDGE 模式

传统输入 DDR 解决方案或 OPPOSITE_EDGE 模式是通过 ILOGIC 模块中的单个输入来实现的。 数据通过时钟上升沿的输出 Q1 和时钟下降沿的输出 Q2 提供给 FPGA 逻辑。下图显示了使用 OPPOSITE_EDGE 模式的输入 DDR 的时序图。

SAME_EDGE 模式

在 SAME_EDGE 模式下,数据在相同的时钟沿被呈现到 FPGA 逻辑中。 下图显示了使用 SAME_EDGE 模式的输入 DDR 的时序图。 在时序图中,输出对 Q1 和 Q2 不再是 (0) 和 (1)。 相反,呈现的第一对是 Q1 (0) 和 Q2 对(无关),然后是下一个时钟周期的对 (1) 和 (2)。

SAME_EDGE_PIPELINED 模式

在 SAME_EDGE_PIPELINED 模式下,数据在同一时钟沿呈现到 FPGA 逻辑中。与 SAME_EDGE 模式不同,数据对不被一个时钟周期分隔。 但是,需要额外的时钟延迟来消除 SAME_EDGE 模式的分离效应。 下图显示了使用 SAME_EDGE_PIPELINED 模式的输入 DDR 的时序图。 输出对 Q1 和 Q2 同时呈现给 FPGA 逻辑。

输入 DDR 资源 (IDDR)

下图显示了 IDDR 原语的框图。 不支持同时设置和重置。类似一个标准寄存器的的功能。

下表列出了 IDDR 端口信号。

| Port Name | Function | Description |

|---|---|---|

| Q1 and Q2 | Data outputs | IDDR 寄存器输出。 |

| C | Clock input port | C 引脚代表时钟输入引脚。 |

| CE | Clock enable port | 使能引脚影响将数据加载到 DDR 触发器中。 低电平时,时钟转换被忽略,新数据不会加载到 DDR 触发器中。 CE 必须为高电平才能将新数据加载到 DDR 触发器中。 |

| D | Data input (DDR) | 来自 IOB 的 IDDR 寄存器输入。 |

| S/R | Set/Reset | 同步/异步置位/复位引脚。 S/R 被断言为高电平。IDDR 原语包含置位和复位引脚。 但是,每个 IDDR 只能使用一个。 描述的是 S/R,而不是单独的置位和复位引脚。 |

下表描述了 IDDR 原语的各种可用属性和默认值。

| Attribute Name | Description | Possible Values |

|---|---|---|

| DDR_CLK_EDGE | 设置相对于时钟边沿的 IDDR 操作模式 | OPPOSITE_EDGE (default), SAME_EDGE, SAME_EDGE_PIPELINED |

| INIT_Q1 | 设置 Q1 端口的初始值 | 0 (default), 1 |

| INIT_Q2 | 设置 Q2 端口的初始值 | 0 (default), 1 |

| SRTYPE | 相对于时钟 的设置/复位类型 | ASYNC (default), SYNC |

可以使用 VHDL 和 Verilog 中实例化 IDDR 原语的模板,配置IDDR功能。

ILOGIC 时序模型

本节描述与 ILOGIC 块内各种资源相关的时序。

ILOGIC 时序特性

下图说明了 ILOGIC 寄存器时序。 使用 IDELAY 时,TIDOCK 被 TIDOCKD 替代。

ILOGIC 输入寄存器时序特性

时钟事件 1

- 在时钟事件 1 之前的时间 TICE1CK,输入时钟使能信号在输入寄存器的 CE1 输入处变为有效高电平,从而为输入数据启用输入寄存器。

- 在时钟事件 1 之前的时间 TIDOCK,输入信号在输入寄存器的 D 输入变为有效高电平,并在时钟事件 1 之后的时间 T ICKQ 反映在输入寄存器的 Q1 输出上。

时钟事件 4

- 在时钟事件 4 之前的时间 TISRCK,S/R 信号(在这种情况下配置为同步复位)变为有效高电平,复位输入寄存器并在时钟事件 4 之后的时间 TICKQ 反映在 IOB 的 Q1 输出。

总结

输入时钟使能信号需要延迟TICE1CK来稳定震荡输出,也即建立时间,数据则需要在时钟上升沿到来之前的TIDOCK的时间进行输入,以满足建立时间。这里的ICKQ为数据输入的保持时间,只有数据保持了ICKQ 的时间才能保证数据能够稳定输出。

ILOGIC 时序特性,DDR

下图说明了 IDDR 模式下的 ILOGIC 时序特性。 使用 IDELAY 时,TIDOCK 被 TIDOCKD 替代。 所示示例在 OPPOSITE_EDGE 模式下使用 IDDR。

时钟事件 1

- 在时钟事件1 之前的TICE1CK 时间,输入时钟使能信号在两个DDR 输入寄存器的CE1 输入处变为有效高电平,从而使它们能够接收输入数据。 由于 CE1 和 D 信号对两个 DDR 寄存器都是通用的,因此必须注意在 CLK 的上升沿和下降沿之间切换这些信号,并满足相对于两个沿的寄存器建立时间。

- 在时钟事件 1 之前的时间 TIDOCK(CLK 的上升沿),输入信号在两个寄存器的 D 输入处变为有效高电平,并在时钟事件 1 之后的时间 TICKQ 反映在输入寄存器 1 的 Q1 输出上。

时钟事件 4

- 在时钟事件 4 之前的时间 TIDOCK(CLK 的下降沿),输入信号在两个寄存器的 D 输入处变为有效低电平,并在时钟事件之后的时间 TICKQ 反映在输入寄存器 2 的 Q2 输出上 4(在这种情况下没有变化)。

时钟事件 9

- 在时钟事件 9 之前的时间 TISRCK,S/R 信号(在这种情况下配置为同步复位)变为有效高电平,在时钟事件 9 之后的时间 TICKQ 复位 Q1,在时钟事件 10 之后的时间 TICKQ 复位 Q2。

总结

类似输入寄存器的时序特性分析,这里使用的是OPPOSITE_EDGE模式,这里对应OPPOSITE_EDGE 模式绘制数据简要传输分析。

下表描述了 7 系列 FPGA 数据手册中 ILOGIC 开关特性的时序参数。

Setup/Hold

| Symbol | Description |

|---|---|

| TICE1CK/TICKCE1 | CE1 pin Setup/Hold with respect to CLK |

| TISRCK/TICKSR | S/R pin Setup/Hold with respect to CLK |

| TIDOCK/TIOCKD | D pin Setup/Hold with respect to CLK |

| TICOCKD/TIOCKDD | DDLY pin Setup/Hold with respect to CLK |

Combinatorial

| Symbol | Description |

|---|---|

| TIDI | D 引脚到 O 引脚传播延迟,无延迟 |

Sequential Delays

| Symbol | Description |

|---|---|

| TIDLO | D 引脚到 Q1 引脚使用触发器作为无延迟的锁存器 |

| T ICKQ | CLK 到 Q 输出 |

| T RQ | S/R 引脚到 OQ/TQ 输出 |

reference

- UG471

边栏推荐

- Microbial ecological sequencing analysis -- CCA analysis

- 复制 代码生成器 生成的代码到idea中,运行后网址报错怎么解决

- tf. AUTO_ Reuse effect

- [Prometheus] an optimization record of Prometheus Federation

- numpy.get_include()

- Hardware exploration -- Design and manufacture of digital clock

- ReturnType

- 应用在电子产品背光显示中的模拟环境光传感芯片

- Things to think about before using mysqldump

- 三维引擎软件Vizard入门

猜你喜欢

Gpushare- members are coming online~

Sub-Category Optimization for Multi-View Multi-Pose Object Detection

【数据挖掘】期末复习 第二章

图着色问题回溯法(最通俗易懂)

Touch chip applied in touch screen of washing machine

DDD 实践手册(4. Aggregate — 聚合)

simple_js 攻防世界

Attack and defense world PHP_ rce

simple_ JS attack and defense world

Metasploit intrusion win7

随机推荐

高德地图Loca 数据可视化 API 2.0的用法

tf.QueueBase

牛客-TOP101-BM26

DDD 实践手册(4. Aggregate — 聚合)

sqli-labs23

tf. compat. v1.global_ variables_ initializer

Detailed explanation of balanced binary tree is easy to understand

scala中函数和方法

DP backpack summary

tf.AUTO_REUSE作用

Microbial ecological sequencing analysis -- CCA analysis

图着色问题回溯法(最通俗易懂)

You have an error in your SQL syntax; check the manual that corresponds to your MYSQL server

398 hash table (242. valid alphabetic words & 349. intersection of two arrays & 202. happy numbers)

【数据挖掘】期末复习 第二章

硬件探索——数字钟的设计与制作

Quartz. Net getting started

Use of mysqldump in MySQL

[MYSQL] MYSQL文件结构,页与行记录

pyshark使用教程