当前位置:网站首页>[Verilog quick start of Niuke online question series] ~ bit splitting and operation

[Verilog quick start of Niuke online question series] ~ bit splitting and operation

2022-06-30 16:39:00 【AI is very good】

Contents of this chapter :

0. Poke an eye

vcs+verdi Joint simulation portal

1. VL5 Bit splitting and operation

1.1 Title Description

Now enter a compressed 16 Bit data , It actually contains four data [3:0][7:4][11:8][15:12],

Now please follow sel Choose to output the addition result of four data , And the output valid_out The signal ( Pull down when not output )

0: No output and only the input at this time is valid

1: Output [3:0]+[7:4]

2: Output [3:0]+[11:8]

3: Output [3:0]+[15:12]

1.1.1 Signal schematic diagram

1.1.2 Waveform diagram

1.1.3 Input description

Input signal d, clk, rst

type wire

stay testbench in ,clk For cycles 5ns The clock of ,rst Reset for low level

1.1.4 Output description

The output signal validout out

type wire

What needs to be noted here is , The official type is reg, When you submit it, you are stupid , Ha ha ha !!!

1.2 Their thinking

The idea is very similar to that of the previous question , Is to save a number , Operate it accordingly .

1.3 Code implementation

module data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,

output [4:0]out,

output validout

);

//*************code***********//

reg [15:0] d_reg;

reg [4:0] out_reg;

reg validout_reg;

always @ (posedge clk or negedge rst) begin

if(!rst) begin

out_reg <= 5'd0;

validout_reg <= 1'b0;

end

else begin

case (sel)

2'b00 : begin

validout_reg <= 1'b0;

d_reg <= d;

out_reg <= 5'd0;

end

2'b01 : begin

validout_reg <= 1'b1;

out_reg <= d_reg[3:0] + d_reg[7:4];

end

2'b10 : begin

validout_reg <= 1'b1;

out_reg <= d_reg[3:0] + d_reg[11:8];

end

2'b11 : begin

validout_reg <= 1'b1;

out_reg <= d_reg[3:0] + d_reg[15:12];

end

default : begin

validout_reg <= 1'b0;

out_reg <= 5'd0;

end

endcase

end

end

assign validout = validout_reg;

assign out = out_reg;

//*************code***********//

endmodule

1.4 The test file

module data_cal_tb();

2 reg clk=0;

3 reg rst;

4 reg [15:0]d;

5 reg [1:0]sel;

6 wire [4:0]out;

7 wire validout;

8

9 always #5 clk = ~clk; // Create clock with period=10

10

11 initial begin

12 #10 rst <= 0;

13 // repeat(10) @(posedge clk);

14 #50 rst <= 1;

15 #210 $finish;

16 end

17

18 data_cal dut(

19 .clk(clk),

20 .rst(rst),

21 .d(d),

22 .sel(sel),

23 .out(out),

24 .validout(validout)

25 );

26

27 initial begin

28 d <= 16'h0000;

29 @(posedge rst);

30 repeat(1) @(posedge clk);

31 d <= 16'b1000010000100001;

32 repeat(4) @(posedge clk);

33 d <= 16'b1000010000100011;

34 repeat(5) @(posedge clk);

35 d <= 16'b1000010000100111;

36 end

37

38 initial begin

39 sel <= 2'd0;

40 @(posedge rst);

41 repeat(2) @(posedge clk);

42 sel <= 2'd2;

43 repeat(3) @(posedge clk);

44 sel <= 2'd1;

45 repeat(3) @(posedge clk);

46 sel <= 2'd0;

47 repeat(1) @(posedge clk);

48 sel <= 2'd3;

49 end

50

51 initial begin

52 $fsdbDumpfile("tb.fsdb");

53 $fsdbDumpvars;

54 end

55 endmodule

1.5 Simulation waveform

This question ,rtl The code is not difficult , But the test file made me feel bad , And there are some small problems in the simulation , as follows :

Stop here , Finally, check the data and say that there is a deadlock in the code , As soon as I check , There is something wrong with the clock , Here again , The clock must be given an initial value , Otherwise everything will be in vain .

Important things are to be repeated for 3 times !!!

The clock must be given an initial value !!!

The clock must be given an initial value !!!

The clock must be given an initial value !!!

Okay , Let's write this article here first !!!

A triptych does not get lost ===>

边栏推荐

- 19:00 p.m. tonight, knowledge empowerment phase 2 live broadcast - control panel interface design of openharmony smart home project

- What are the reasons for the errors reported by the Flink SQL CDC synchronization sqlserver

- 【机器学习】K-means聚类分析

- Under the pressure of technology, you can quickly get started with eth smart contract development, which will take you into the ETH world

- Go zero micro Service Practice Series (VIII. How to handle tens of thousands of order requests per second)

- Explain in detail the use of for loop, break and continue in go language

- Arcmap操作系列:80平面转经纬度84

- Distributed machine learning: model average Ma and elastic average easgd (pyspark)

- 抖快B为啥做不好综艺

- RT-Thread 堆區大小設置

猜你喜欢

抖快B为啥做不好综艺

![Warning: [antd: Menu] `children` will be removed in next major version. Please use `items` instead.](/img/c1/99ad29789a669c4498fb93ce1fb009.png)

Warning: [antd: Menu] `children` will be removed in next major version. Please use `items` instead.

How the edge computing platform helps the development of the Internet of things

'&lt;', Hexadecimal value 0x3c, is an invalid problem solving

今晚19:00知识赋能第2期直播丨OpenHarmony智能家居项目之控制面板界面设计

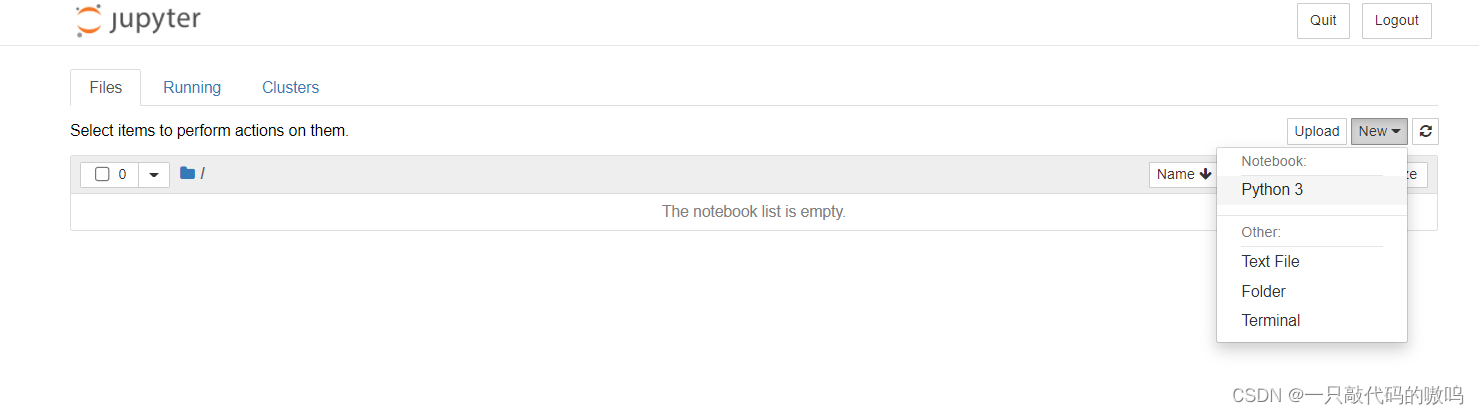

Anaconda下安装Jupyter notebook

Go zero micro Service Practice Series (VIII. How to handle tens of thousands of order requests per second)

搬运两个负载均衡的笔记,日后省的找

CloudXR如何推动XR的未来发展

边缘计算平台如何助力物联网发展

随机推荐

容联云首发基于统信UOS的Rphone,打造国产化联络中心新生态

中航无人机科创板上市:市值385亿 拳头产品是翼龙无人机

招标公告:深圳市财政局数据库异地灾备项目

Compulsory national standard for electronic cigarette GB 41700-2022 issued and implemented on October 1, 2022

【机器学习】K-means聚类分析

牛客网:有多少个不同的二叉搜索树

Dart: string replace related methods to solve replacement characters

KDD 2022 | how far are we from the general pre training recommendation model? Universal sequence representation learning model unisrec for recommender system

Bidding announcement: Taizhou Unicom Oracle all in one machine and database maintenance service project in 2022

Arcmap操作系列:80平面转经纬度84

Finally understand science! 200 pictures to appreciate the peak of human wisdom

Half year inventory of new consumption in 2022: the industry is cold, but these nine tracks still attract gold

2022蓝桥杯国赛B组-2022-(01背包求方案数)

2022 Blue Bridge Cup group B -2022- (01 backpack to calculate the number of schemes)

Does flinkcdc have to be a clustered version if the monitored database is Mongo

Unsupported major.minor version 52.0

Which direction should college students choose to find jobs after graduation?

Cesium-1.72 learning (add points, lines, cubes, etc.)

“低代码”在企业数字化转型中扮演着什么角色?

Li Zexiang, a legendary Chinese professor, is making unicorns in batches