当前位置:网站首页>SOC clock configuration

SOC clock configuration

2022-06-28 07:40:00 【youbin2013】

SOC Clock configuration

1 Working principle of PLL

Soc Of Clock generating unit (CGU) Through external input clock and internal phase-locked loop (PLL) And the frequency division selection logic generates clocks for different frequencies in the chip . The on-chip clock frequency is changed through configuration AHB Bus global control module unit internal PLL register implementation .

CGU The unit contains three phase locked loops , Generate system master clock respectively 、DDR Physical layer clock 、 Ethernet physical layer clock , Its configuration register is located in AHB Bus global control module .CGU The module also generates 1553 Module clock and UART The clock .

The PLL adopts 65nm In the process library PLLSM65LLFRAC PLL , Its maximum output frequency is 1.6GHz, Including decimal configuration mode and integer configuration mode , The PLL in the clock management unit adopts integer configuration mode , User configurable pins are shown in table 1 listed .

surface 1 Common PLL can be configured with pins

Pin name | Direction | A wide | explain |

REFDIV( Frequency divider ) | I | 6 | PLL frequency division coefficient |

FBDIV( Frequency multiplier ) | I | 12 | PLL frequency doubling coefficient |

Phase locked loop clock FOUTVCO Express , Crystal oscillator input clock CLKIN Express , Frequency multiplier coefficient is FBDIV Express , The frequency divider coefficient is REFDIV Express , The master clock uses MAINPLL Express ,DDR3 For clock DDRPLL Express , Ethernet clock ENETPLL Express . The PLL configuration formula is as follows :

PLL clock :FOUTVCO = CLKIN * FBDIV / REFDIV;

Master clock :MAINPLL = CLKIN * FBDIV / (2*REFDIV);

DDR3 The clock :DDRPLL = CLKIN * FBDIV / (2*REFDIV);

Ethernet clock :ENETPLL = CLKIN * FBDIV / (6*REFDIV);

What to pay attention to : The range of output clock is 400MHz ≤ FOUTVCO ≤ 1600MHz; For configuration signals REFDIV、FBDIV The requirements of :1 ≤ REFDIV ≤ 63;16 ≤ FBDIV ≤ 1600; Check the PLL status register to know whether the PLL is locked , At this time, configure the PLL .

2 The configuration process

Configuration of main PLL :

The master PLL generates the system master clock , The principle analysis of the master clock phase locked loop shows that it meets :

MAINPLL = CLKIN * FBDIV / (2*REFDIV).

Configuration steps :

- Read the master PLL register of the global control module , Check the PLL status register LOCK Bit information (0x40c00008 The first of the registers 21 position ), Until the bit is read as 0x1;

- To the master PLL register BYPASS Bit writing 0x1 operation (0x40c00008 The first of the registers 20 position ), To the master PLL register LOCK Bit writing 0x1 operation (0x40c00008 The first of the registers 21 position );

- Configure the master clock frequency multiplication coefficient of the master PLL register (FBDIV) And the frequency division coefficient of the master clock (REFDIV),MAINPLL = CLKIN * FBDIV / (2*REFDIV), Configure the main frequency as 400MHz, be FBDIV = 0xA0,REFDIV = 0x5(FBDIV For the register 19-8 position ,REFDIV For the register 5-0 position );

- Wait for the main PLL register frequency latch to complete , Read by loop LOCK You know , If LOCK Bit read as 0, Indicates that the frequency latch is completed ;

- To the master PLL register BYPASS Bit write 0, Indicates that the clock is in PLL mode , Non bypass mode .

DDR PLL configuration :

DDR PLL generation system DDR3 The clock , about DDR The principle analysis of PLL shows that it meets :

DDRPLL = CLKIN * FBDIV / (2*REFDIV).

Configuration steps :

- Read out the global control module DDR PLL register , Check the PLL status register LOCK Bit information (0x40c0000c The first of the registers 21 position ), Until the bit is read as 0x1;

- Yes DDR PLL register BYPASS Bit writing 0x1 operation (0x40c0000c The first of the registers 20 position ), To the master PLL register LOCK Bit writing 0x1 operation (0x40c0000c The first of the registers 21 position );

- To configure DDR PLL register DDR Clock frequency multiplication coefficient (FBDIV) and DDR Clock frequency division coefficient (REFDIV),DDRPLL = CLKIN * FBDIV / (2*REFDIV), Configure the main frequency as 533MHz, be FBDIV = 0x215,REFDIV = 0x32(FBDIV For the register 19-8 position ,REFDIV For the register 5-0 position );

- wait for DDR PLL register frequency latch complete , Read by loop LOCK You know , If LOCK Bit read as 0, Indicates that the frequency latch is completed ;

- towards DDR PLL register BYPASS Bit write 0, Indicates that the clock is in PLL mode , Non bypass mode .

3 Data structure encapsulation

According to the distribution of the clock module register address in the memory allocation diagram , Define its address as an integer macro definition , The register is defined as the structural union of each functional bit field . In this way, the integer address is converted to the structural union pointer of the register , You can write the underlying driver through the register bit field , chart 1 Represents the definition and type conversion of the macro definition register , chart 2 Represents the register structure union definition .

chart 1

chart 2

边栏推荐

- Section VII starting principle and configuration of zynq

- R 语言 ggmap

- Resizing node of rediscluster cluster cluster mode

- Flex layout

- What is EC blower fan?

- Flutter realizes the function of "shake"

- HTTP Caching Protocol practice

- A single node obtains the lock lock of the order number

- Is it reliable to register and open an account for stock speculation? Is it safe?

- R language ggmap visual cluster

猜你喜欢

flex布局

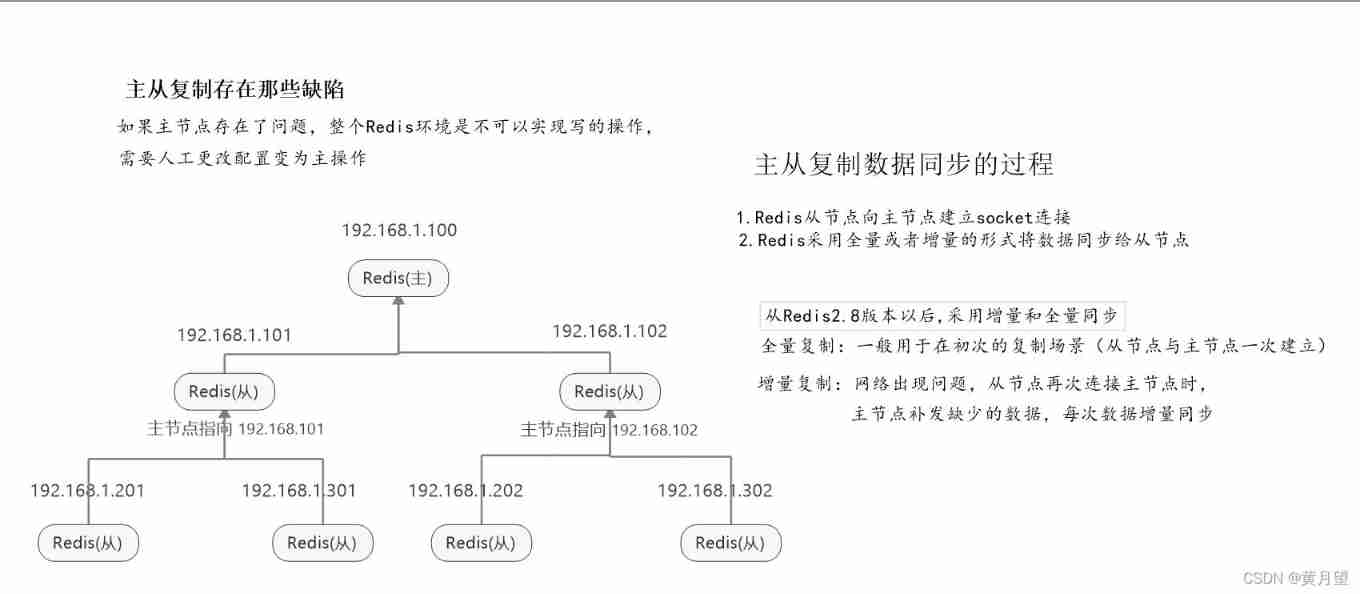

Redis one master multi slave cluster setup

云原生:云计算技术再次升级 开启全面云开发时代

Analyze 5 indicators of NFT project

本周二晚19:00战码先锋第8期直播丨如何多方位参与OpenHarmony开源贡献

Section 9: dual core startup of zynq

Hack the box:routerspace

Application and Optimization Practice of redis in vivo push platform

Construction and exploration of vivo database and storage platform

Section 5: zynq interrupt

随机推荐

大型项目中的Commit Message规范化控制实现

Design and implementation of spark offline development framework

代码提交规范

安全培训是员工最大的福利!2022新员工入职安全培训全员篇

Practice of traffic recording and playback in vivo

[thanos source code analysis series]thanos query component source code analysis

HJ字符串排序

Ice, protobuf, thrift -- Notes

Disposition Flex

Leetcode+ 66 - 70 high precision, two sub topics

R language hitters data analysis

云原生(待更新)

Can okcc call centers work without computers?

剑指Offer||:链表(简单)

NDK cross compilation

A single node obtains the lock lock of the order number

Recommended system series (Lecture 5): Optimization Practice of sorting model

XML serialization backward compatible

open62541直接导入NodeSet文件

What is EC blower fan?