当前位置:网站首页>[Verilog] HDLBits Problem Solution - Verification: Writing Testbenches

[Verilog] HDLBits Problem Solution - Verification: Writing Testbenches

2022-08-03 12:11:00 【wjh776a68】

Clock

module top_module ( );

reg clk;

initial begin

clk = 0;

forever #5 clk = ~clk;

end

dut dut_inst(.clk(clk)) ;

endmodule

Testbench1

module top_module ( output reg A, output reg B );//

// generate input patterns here

initial begin

A = 0;

B = 0;

#10

A = 1;

#5

B = 1;

#5

A = 0;

#20

B = 0;

end

endmodule

AND gate

module top_module();

reg [1:0] in;

wire out;

initial begin

in = 'b0;

#10;

in = 'b01;

#10;

in = 'b10;

#10;

in = 'b11;

#10;

//$finish;

end

andgate andgate_inst (

.in(in),

.out(out)

);

endmodule

Testbench2

module top_module();

reg clk;

reg in;

reg [2:0] s;

reg [5:0] STAT;

wire out;

initial begin

STAT = 0;

clk = 0;

in = 0;

s = 'h2;

forever #5 clk = ~clk;

end

always @ (negedge clk) begin

case (STAT)

0: begin

s <= 'h6;

end

1: begin

s <= 'h2;

in <= 1;

end

2: begin

s <= 'h7;

in <= 0;

end

3: begin

s <= 'h0;

in <= 1;

end

6: begin

s <= 'h0;

in <= 0;

end

default: begin

end

endcase

if (STAT < 6) begin

STAT <= STAT + 1;

end

end

q7 q7_inst(

.clk(clk),

.in(in),

.s(s),

.out(out)

);

endmodule

T flip-flop

module top_module ();

reg clk, reset, t;

reg [5:0] STAT;

wire q;

initial begin

clk = 0;

reset = 0;

t = 0;

STAT = 0;

forever #1 clk = ~clk;

end

always @ (posedge clk) begin

case (STAT)

0: begin

reset <= 1;

STAT <= 1;

end

1: begin

reset <= 0;

t <= 1;

STAT <= 2;

end

2: begin

t <= 0;

end

endcase

end

tff tff_inst(

.clk(clk),

.reset(reset), // active-high synchronous reset

.t(t), // toggle

.q(q)

);

endmodule

边栏推荐

猜你喜欢

随机推荐

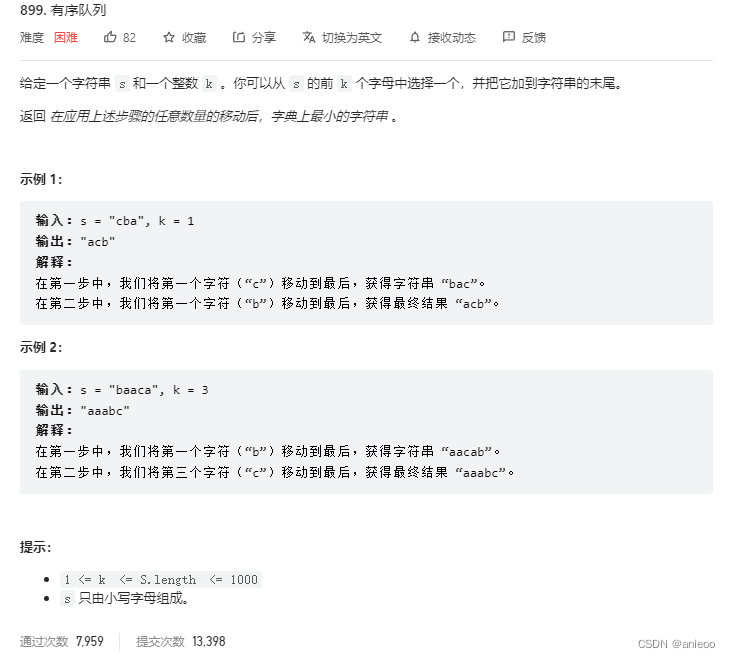

899. 有序队列

详解虚拟机!京东大佬出品HotSpot VM源码剖析笔记(附完整源码)

ssh 免密登录了解下

awk入门教程

TiKV & TiFlash 加速复杂业务查询丨TiFlash 应用实践

深入理解MySQL事务MVCC的核心概念以及底层原理

Matlab学习13-图像处理之可视化GUI程序

我在母胎SOLO20年

FE主导打造一个运营活动平台

想学自动化测试网课哪个好?过了人告诉你:适合自己的才是最重要

hystrix 服务熔断和服务降级

pandas连接oracle数据库并拉取表中数据到dataframe中、生成当前时间的时间戳数据、格式化为指定的格式(“%Y-%m-%d-%H-%M-%S“)并添加到csv文件名称中

当前页面的脚本发生错误如何解决_电脑出现当前页面脚本错误怎么办

【一起学Rust】Rust的Hello Rust详细解析

R语言拟合ARIMA模型并使用拟合模型进行预测推理、使用autoplot函数可视化ARIMA模型预测结果、可视化包含置信区间的预测结果

信创建设看广州|海泰方圆亮相2022 信创生态融合发展论坛

微信小程序获取手机号

opencv学习—VideoCapture 类基础知识「建议收藏」

为什么越来越多的开发者放弃使用Postman,而选择Eolink?

从器件物理级提升到电路级