当前位置:网站首页>Verilog daily question (vl6 data series to parallel circuit)

Verilog daily question (vl6 data series to parallel circuit)

2022-07-28 17:23:00 【Don't make any more errors】

Title Description

Realize serial parallel conversion circuit , Input end input sheet bit data , Whenever this module receives 6 After inputting data , The output end outputs the spliced 6bit data . The input end and upstream of this module adopt valid-ready Two way handshake system , The downstream and downstream outputs are used valid-only handshake mechanisms . When splicing data, the data received first is put into data_b Low position .

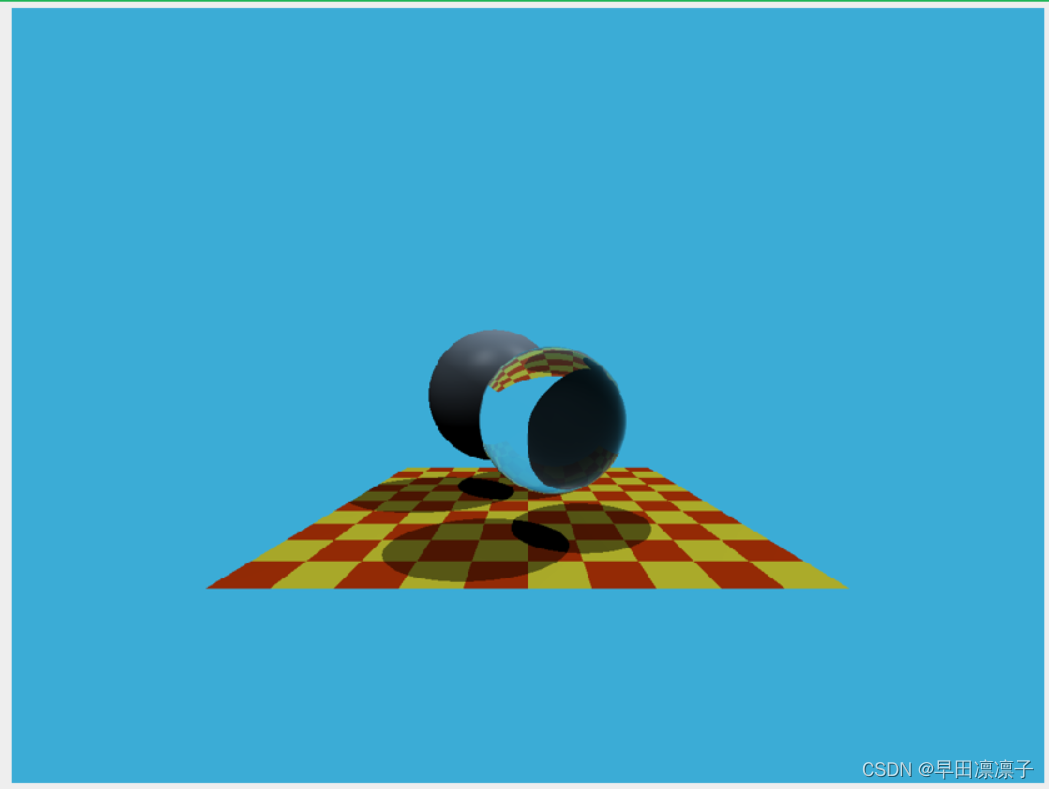

The interface of the circuit is shown in the figure below .valid_a Used to indicate data entry data_a The effectiveness of the ,valid_b Used to indicate data output data_b The effectiveness of the ;ready_a Used to indicate whether the module is ready to receive upstream data , Always pull up in this module ;clk It's a clock signal ;rst_n It is an asynchronous reset signal .

The principle of handshake agreement is : When Valid and Ready When the signal is highly effective at the same time , Data is transmitted on the rising edge of the clock .

The detailed code is as follows :

module s_to_p(

input clk ,

input rst_n ,

input valid_a ,

input data_a ,

output reg ready_a ,

output reg valid_b ,

output reg [5:0] data_b

);

// It can be seen from the oscillogram that ,ready_a Always set the high level , That is, it is always ready to receive

always @(posedge clk or negedge rst_n ) begin

if(!rst_n)

ready_a <= 0;

else

ready_a <= 1;

end

// Count the effective signals , And use a data_in To save the data

// also valid_a=0 Time does not clear , Will work with the follow-up valid_a=1 Data splicing when

reg [3:0] num;

reg [5:0] data_in;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

num <=0;

data_in <=0;

end

else if(valid_a) begin

num <= (num==5)? 0:num+1;

data_in = {data_a,data_in[5:1]}; // Store data and shift to save

end

end

// Output

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

data_b <=0;

valid_b <=0;

end

else if(num==5) begin

valid_b <= 1 ;

data_b <= data_in;

end

else

valid_b <=0;// High level signal with only one cycle

end

endmoduleDone!

边栏推荐

- 【impala】【报错解决】 Impala cannot read or execute the parent directory of dfs.domain.socket.path的解决方法

- Verilog 每日一题 (VL5 信号发生器)

- Goweb开发之Beego框架实战:第一节 Beego框架介绍

- Learn about service discovery in kubernetes

- The practice of the beego framework of goweb development: Section II project initialization configuration

- Asynchronous circuit design -- principle and example of synchronous pulser

- 线性代数及矩阵论(九)

- 线性代数及矩阵论(八)

- mysql 最大建议行数2000w,靠谱吗?

- Some attention code explanations

猜你喜欢

高速电路中电感的选型和应用

Unity editor learning (I) using features to change the display of fields in components

The practice of beego framework developed by goweb: Section 4 database configuration and connection

Unity shader realizes mirror effect with rendered texture

Games101-assignment05 ray tracing - rays intersect triangles

DGL Chapter 1 (official tutorial) personal notes

Visual Studio 2012/2015发布Web应用连同.cs源码一起发布

kubernetes service 原理解析

GEAR: Graph-based Evidence Aggregating and Reasoning for Fact Verification

Goweb开发之Beego框架实战:第二节 项目初始化配置

随机推荐

【CDH】通过 ClouderaManager 配置CDH组件用 prometheus 监控采集JMX信息

解决SQL Server数据库独占的问题

QR code generation of wechat applet with parameters

How to protect image security during construction

微服务架构-服务注册中心和服务网关(6.8) (转载)

总数据量超万亿行,玉溪卷烟厂通过正确选择时序数据库轻松应对

微信小程序现金红包返回“IP地址非你在商户平台设置的可用IP地址”错误终极解决方法

Andthen of function interface

Verilog daily question (vl27 settable counter)

net框架

利用SQL Server代理作业对数据库进行定时还原

Games101 assignment04 job 04

异步电路设计--同步脉冲器原理及例题

2022牛客多校第二场CDE

Use Alibaba cloud's free SSL certificate

Verilog 每日一题(VL4 移位运算与乘法)

Visual Studio 2015 团队开发之Azure DevOps篇

Unity3d shader achieves ablation effect

kubernetes service 原理解析

Visual Studio 2012/2015发布Web应用连同.cs源码一起发布