当前位置:网站首页>Door level modeling - after class exercises

Door level modeling - after class exercises

2022-07-01 23:33:00 【Jiangnan small workshop】

exercises

Using dual input nand door , use Verilog Write your own and or not gate , And verify the function of these doors with the excitation module .

And gate ,verilog Realization , Use three NAND gates

module my_add( output out, input a, input b ); wire w1,w2; nand na1(w1,a,b); nand na2(w2,a,b); nand na3(out,w1,w2); endmoduleRTL View

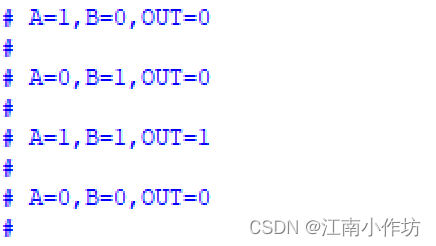

Simulation Implementation

The simulation results meet the and gate logic .

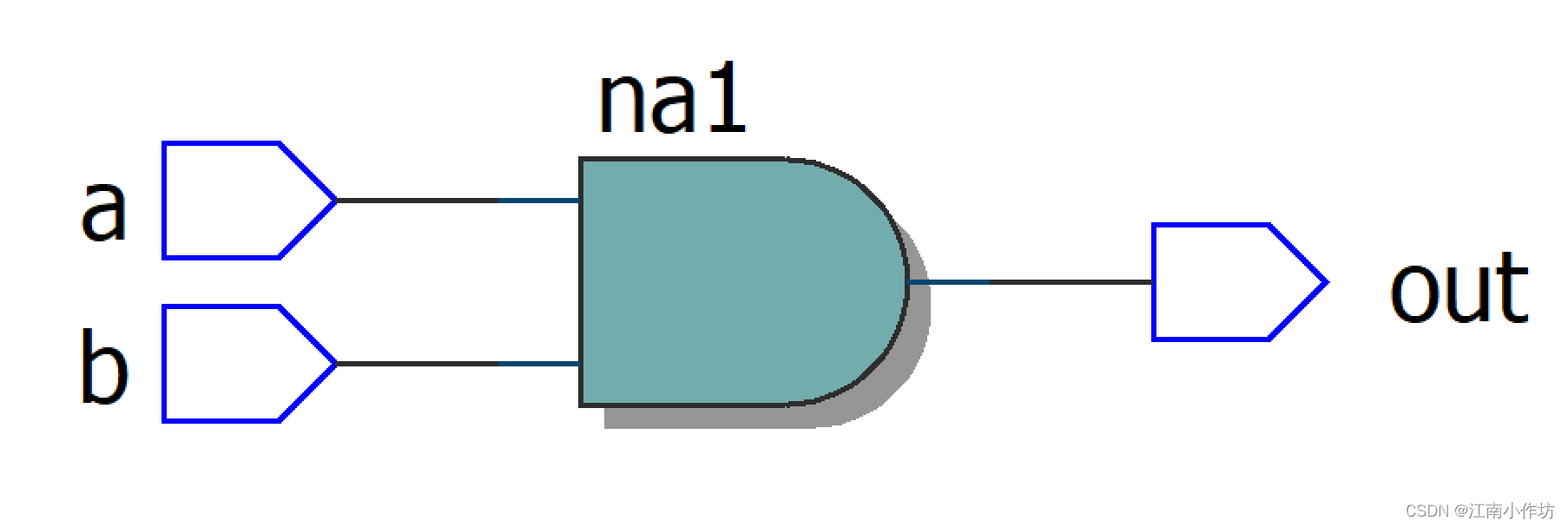

And gate ( The second way ),Verilog Realization , Two NAND gates

module my_and( output out, input a, input b ); wire w1; nand na1(w1,a,b); nand na2(out,w1,w1); endmoduleRTL View

Simulation results

Or gate ,verilog Realization

// Build or gate module my_or( output out, input a, input b ); // Input short circuit wire w1,w2; nand (w1,a,a); nand (w2,b,b); nand (out,w1,w2); endmoduleSimulation verification

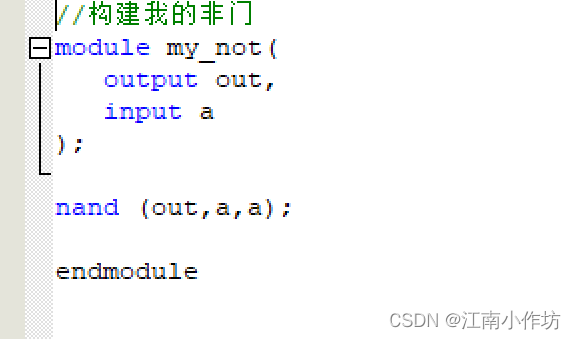

Not gate , It's very simple , Just short-circuit the NAND gate , We don't have to verify them one by one . I didn't want to write my_not Of , As a result, the second question needs , Stick its code .

Use the definition in the above question my_and,my_or,my_not, To build an XOR gate (xor), Function calculation z = x ˉ y + x y ˉ z=\bar{x}y+x\bar{y} z=xˉy+xyˉ, Write simulation signal to test it .

verilog Realization

// comprehensive my_and,my_or,my_not module my_xor( output out, input a, input b ); // Declare intranet wire w1,w2,w3,w4; my_not my_not_1(w1,a); my_not my_not_2(w2,b); my_and my_and_1(w3,w1,b); my_and my_and_2(w4,w2,a); my_or my_or_1(out,w3,w4); endmoduleRTL View

Simulation design

// Simulation definition module my_xor_tb(); reg x,y; wire z; my_xor my_xor_inst(z,x,y); initial begin x=1'b0; y=1'b1; #10 x=1'b0; y=1'b0; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b0; y=1'b1; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b1; y=1'b0; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b1; y=1'b1; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); end endmoduleSimulation results , Satisfy XOR gate logic

Too lazy to type , The title is as follows

Verilog Realization

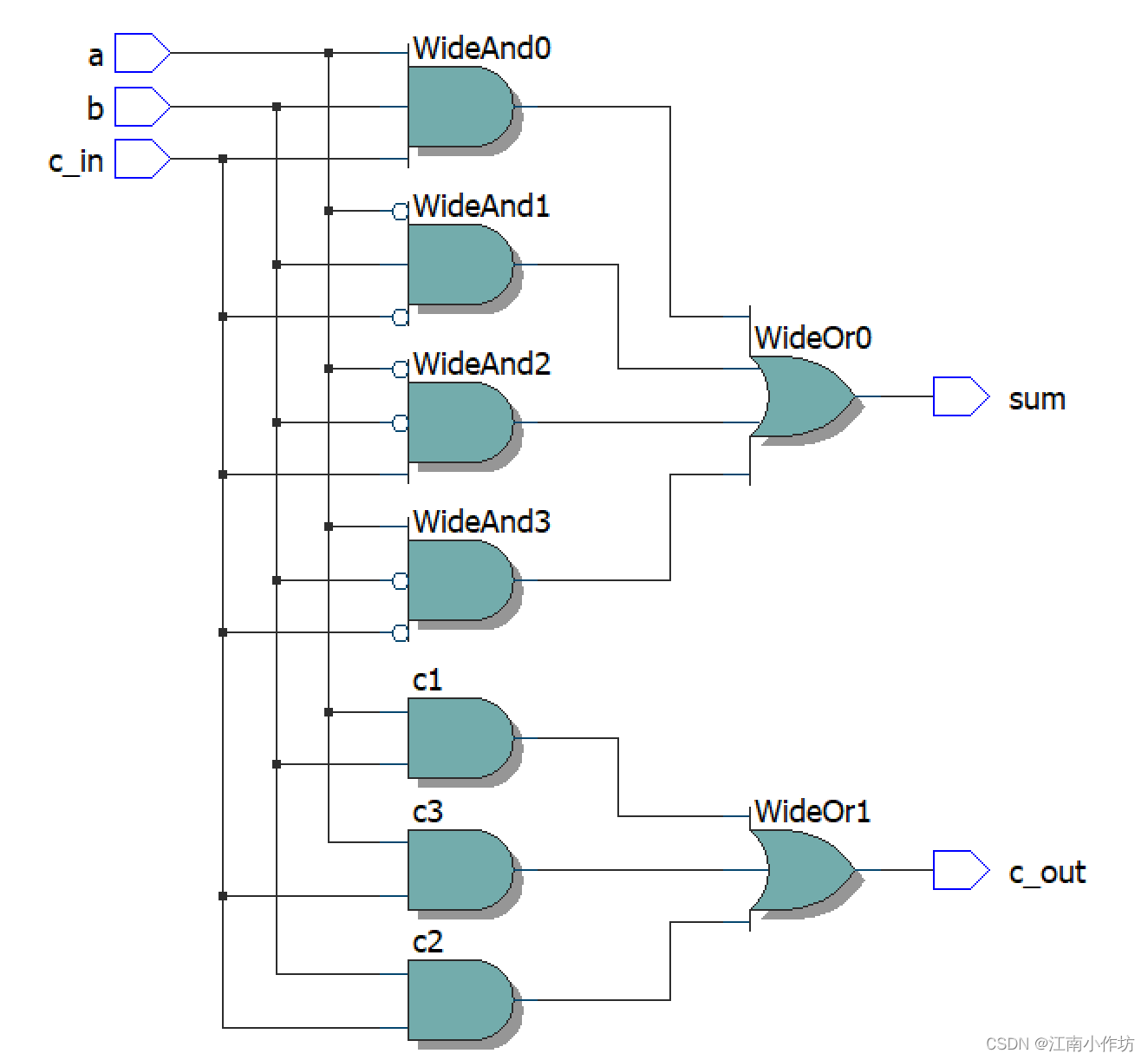

module my_fulladder( output sum, output c_out, input a, input b, input c_in ); wire a_1, b_1, c_in_1; wire s1, s2, s3, s4; wire c1, c2, c3; // First realize the not gate in the equation , And connect with the network defined above not (a_1, a); not (b_1, b); not (c_in_1, c_in); // Realize sum and (s1,a,b,c_in); and (s2,a_1,b,c_in_1); and (s3,a_1,b_1,c_in); and (s4,a,b_1,c_in_1); or (sum,s1,s2,s3,s4); // Realize c_out and (c1,a,b); and (c2,b,c_in); and (c3,a,c_in); or (c_out,c1,c2,c3); endmoduleRTL View

Simulation Implementation

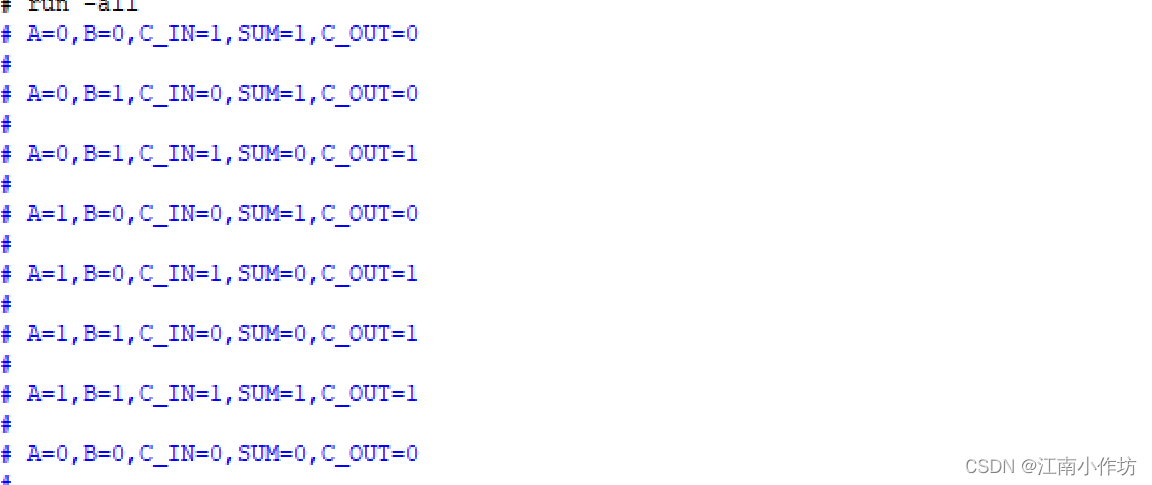

module my_fulladder_tb(); reg A,B,C_IN; wire C_OUT,SUM; my_fulladder my_fulladder_inst(SUM, C_OUT, A, B, C_IN); initial begin A = 1'b0; B = 1'b0; C_IN = 1'b0; #10 A = 1'b0; B = 1'b0; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b1; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b1; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b0; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b0; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b1; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b1; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b0; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); end endmoduleSimulation results , Meet the design requirements

Directly above

verilog Realization

module my_rs_latch( output q, output qbar, input set, input reset ); nor #(1) (q,reset,qbar); nor #(1) (qbar,q,set); endmoduleSimulation

module my_rs_latch_tb(); reg SET,RESET; wire Q,QBAR; my_rs_latch my_rs_latch_inst(Q,QBAR,SET,RESET); initial begin SET=1'b0; RESET = 1'b0; #10 SET=1'b0; RESET = 1'b1; #10 SET=1'b1; RESET = 1'b0; #10 SET=1'b1; RESET = 1'b1; end endmoduleSimulation results , After two time units (2 ps),q Change

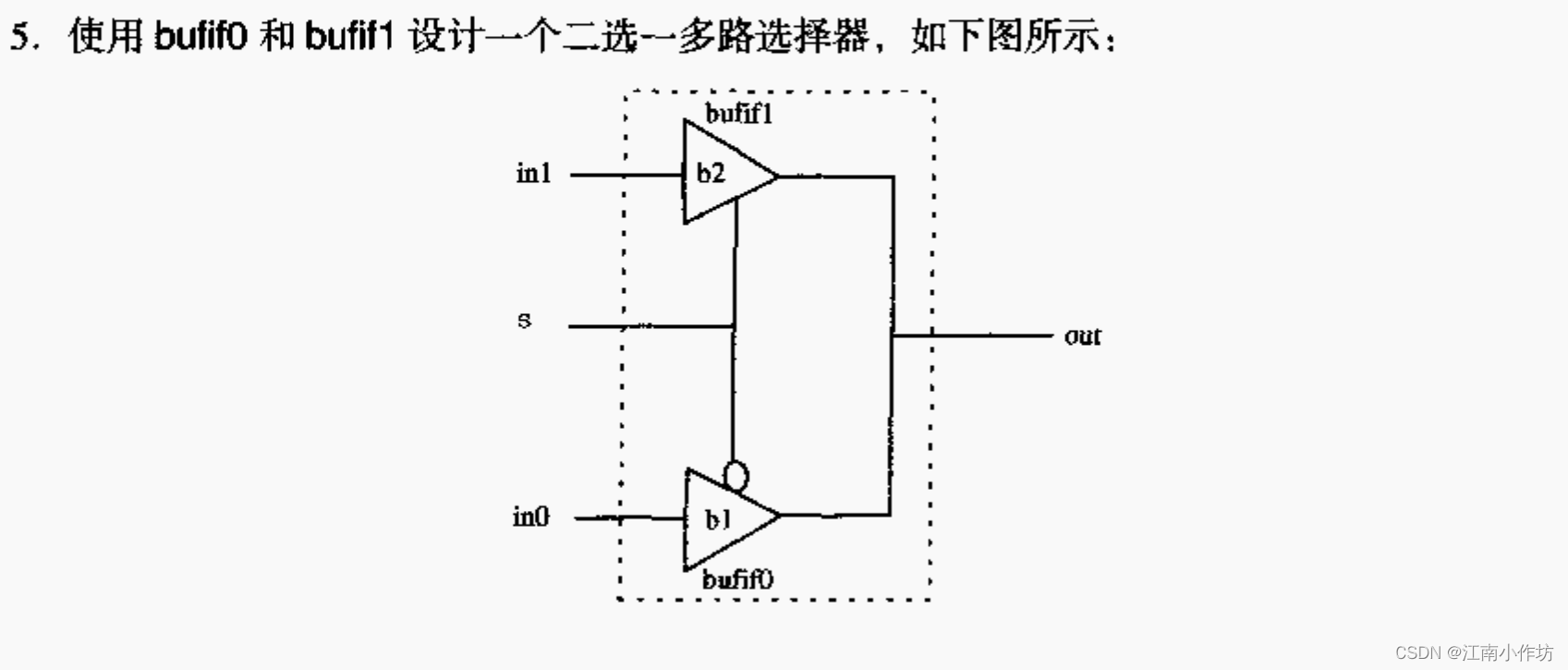

Upper figure

This multiplexer , When s by 1 When , Output in1;s by 0 When , Output in2.

verilog Realization

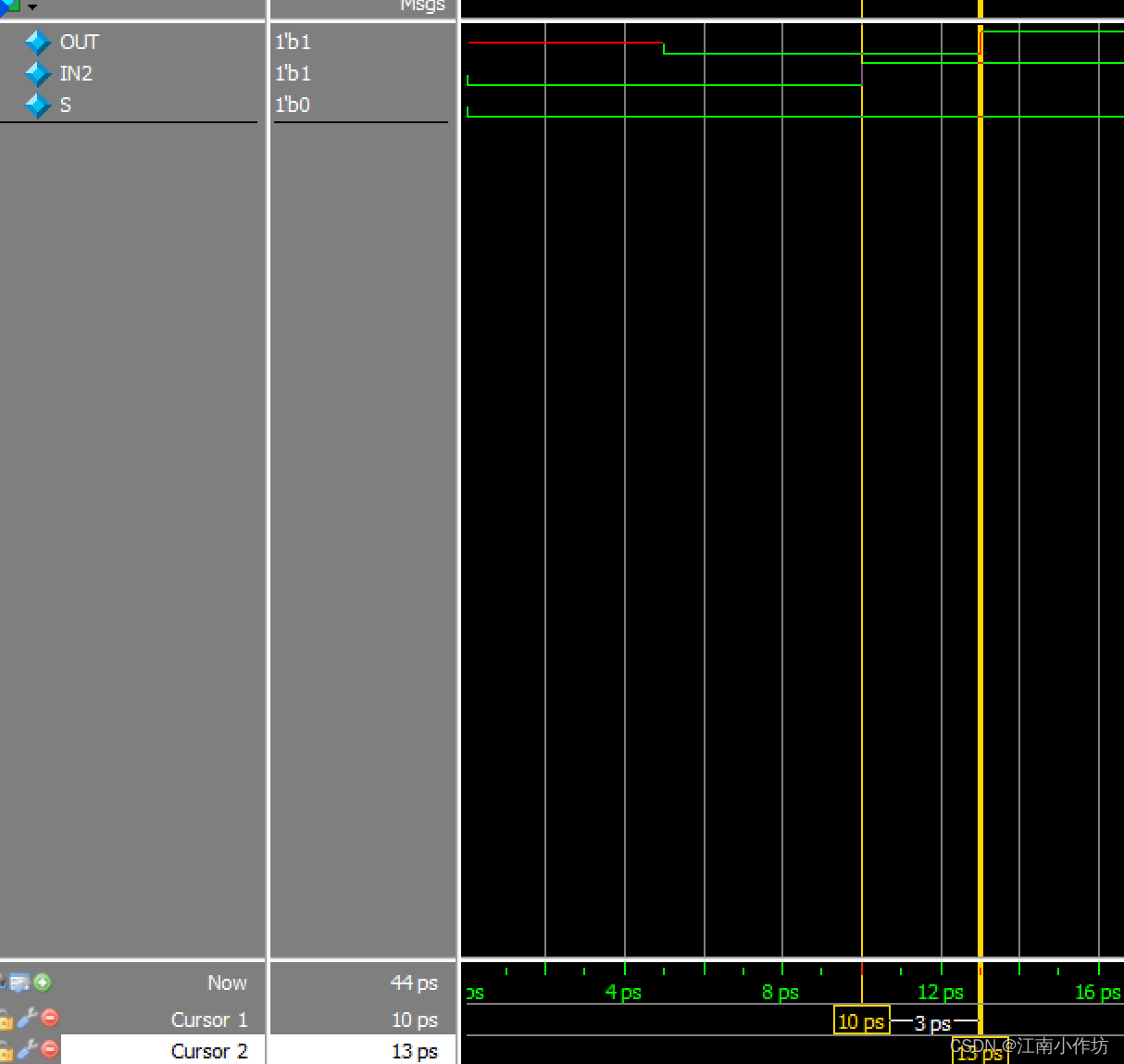

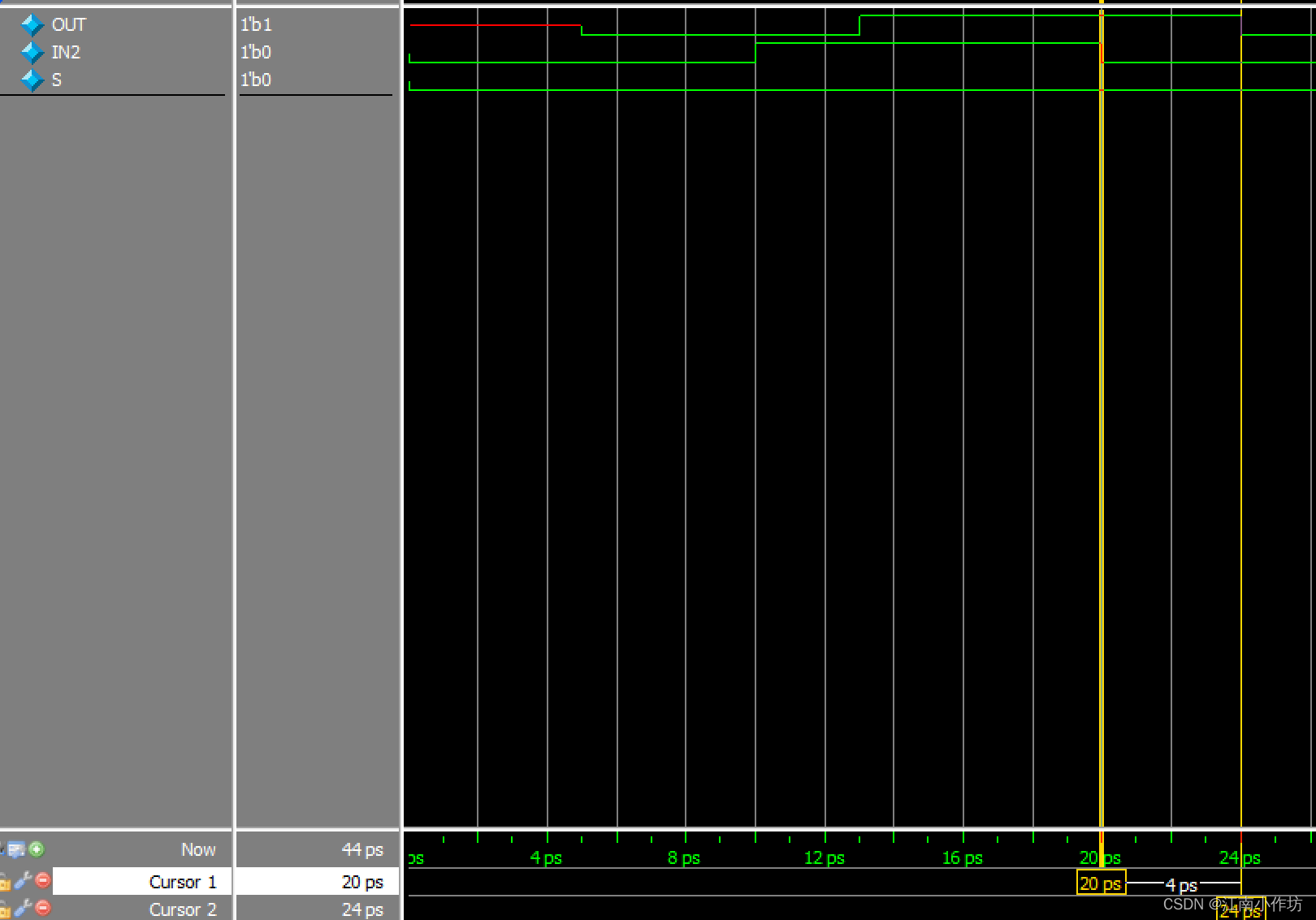

module my_mux2_to_1( output out, input in1,in2, input s ); bufif1 #(1:3:5,2:4:6,3:5:7) buf1(out,in1,s); bufif0 #(1:3:5,2:4:6,3:5:7) buf0(out,in2,s); endmoduleSimulation results

- When s by 0 when , Output in2, When in2 by 1 when , It's delayed 3 In time units ,in2 by 1

- When s by 0 when , Output in2, When in2 by 0 when , It's delayed 4 In time units ,in2 by 0

- When s by 1 when , Empathy .

- When s by 0 when , Output in2, When in2 by 1 when , It's delayed 3 In time units ,in2 by 1

边栏推荐

- CADD course learning (3) -- target drug interaction

- What category does the Internet of things application technology major belong to

- 问题随记 —— file /usr/share/mysql/charsets/README from install of MySQL-server-5.1.73-1.glibc23.x86_64 c

- 2022年危险化学品经营单位安全管理人员考试题及在线模拟考试

- 通过Go语言创建CA与签发证书

- SWT/ANR问题--SWT 导致 low memory killer(LMK)

- 2022 crane driver (limited to bridge crane) examination questions and simulation examination

- SWT/ANR问题--SWT 导致 kernel fuse deadlock

- Matplotlib常用图表

- 字典、哈希表、数组的概念

猜你喜欢

随机推荐

2022-07-01: at the annual meeting of a company, everyone is going to play a game of giving bonuses. There are a total of N employees. Each employee has construction points and trouble points. They nee

Matplotlib常用設置

Three development trends of enterprise application from the perspective of the third technological revolution

dat. GUI

Notes on problems - /usr/bin/perl is needed by mysql-server-5.1.73-1 glibc23.x86_ sixty-four

力扣今日题-241. 为运算表达式设计优先级

硅谷产品实战学习感触

What are the common types of points mall games?

SQL optimization

股票开户哪个证券公司最好,有安全保障吗

Zero foundation tutorial of Internet of things development

Daily three questions 6.30

Microservice stability management

图的遍历之深度优先搜索和广度优先搜索

mt管理器测试滑雪大冒险

mysql binlog的清理

【C#】依赖注入及Autofac

STM32F030F4驱动TIM1637数码管芯片

JS - use of arguments

ConcurrentSkipListMap——跳表原理