当前位置:网站首页>第一章:ARM公司Cortex-M 系列处理器介绍,第二章:嵌入式软件开发介绍和第三章:Cortex-M3和Cortex-M4处理器的一般介绍

第一章:ARM公司Cortex-M 系列处理器介绍,第二章:嵌入式软件开发介绍和第三章:Cortex-M3和Cortex-M4处理器的一般介绍

2022-08-03 05:55:00 【qqssss121dfd】

C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器使用32位体系结构, R e g i s t e r b a n k Register\quad bank Registerbank里面的内部寄存器和, d a t a p a t h data\quad path datapath和总线接口都是32位的。 C o r t e x − M Cortex-M Cortex−M系列处理器的指令集体系结构 ( I n s t r u c t i o n S e t A r c h i t e c t u r e , I S A ) (Instruction\quad Set\quad Architecture,ISA) (InstructionSetArchitecture,ISA)叫做 T h u m b I S A Thumb\quad ISA ThumbISA,它是基于 T h u m b − 2 Thumb-2 Thumb−2技术。这种技术支持16位指令和32位指令的混合。 C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器是哈弗体系结构(最明显的特征是指令和数据的存储是分开的,接入路径也是分开的,这一点和冯洛伊曼体系结构是不同的),32位寻址,支持 4 G B 4GB 4GB存储空间,支持 B i t B a n d Bit\quad Band BitBand特性。当然还有很多其它的特性我这里没有提到,有需要的可以直接查询文档。

C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器广泛应用于现代微控制器产品,以及 S y s t e m o n C h i p , S o C System\quad on\quad Chip,SoC SystemonChip,SoC和 A p p l i c a t i o n S p e c i f i c S t a n d a r d P r o d u c t , A S S P Application\quad Specific\quad Standard\quad Product,ASSP ApplicationSpecificStandardProduct,ASSP。根据知乎的这篇文章, S o C SoC SoC和微控制器的区别是:微控制器是单一内核集成一些通用的外设,应用范围广, S o C SoC SoC是在这些芯片的基础上,集成了其他的核或电路,为某一特定领域打造的。也就是说微控制器的通用性更高, S o C SoC SoC的专用性更高,比如 S o C SoC SoC可以是在 C o r t e x − M 4 Cortex-M4 Cortex−M4内核基础上集成了视频处理功能的专门用来进行视频处理的芯片,而一般的微控制器可能是基于 C o r t e x − M 4 Cortex-M4 Cortex−M4内核而整合了一些通用外设(比如 I 2 C , U S A R T I^2C,USART I2C,USART)的芯片。

这里是维基百科上面的ARM公司的全系列产品列表。 A R M ARM ARM公司不生产微控制器( m i c r o c o n t r o l l e r microcontroller microcontroller),它设计处理器( p r o c e s s o r processor processor)以及相关所需,并将这些授权给芯片设计公司。 A R M ARM ARM公司的这种相关设计叫做知识产权( I n t e l l e c t u a l y P r o p e r t y , I P Intellectualy\quad Property,IP IntellectualyProperty,IP),我们也知道目前有很多的芯片设计公司,例如 S T M 32 STM32 STM32系列的意法半导体,购买 A R M ARM ARM公司的这种设计,这种商业模式叫做 I P IP IP授权。前面所说的 p r o c e s s o r processor processor应该就是我们在谈到某个基于 A R M ARM ARM公司生产的某个芯片的时候都会问的:这个芯片是基于上面内核的, C o r t e x − M 4 Cortex-M4 Cortex−M4?当某个公司得到 A R M ARM ARM公司的授权之后, A R M ARM ARM公司会把 p r o c e s s o r processor processor设计的源代码( V e r i l o g − H D L , H a r d w a r e D e s c r i p t i o n L a n g u a g e ) Verilog-HDL,Hardware\quad Description\quad Language) Verilog−HDL,HardwareDescriptionLanguage)交给这个公司,然后该公司将它们自己对外设或存储的设计代码整合到该 p r o c e s s o r processor processor设计的源代码中,整合完毕之后再使用 E D A EDA EDA工具将设计代码转换为最后的晶体管布局就可以进行实际的芯片生产了。

A R M ARM ARM公司的所有 C o r t e x − M Cortex-M Cortex−M处理器都是32位的 R e d u c e d I n s t r u c t i o n S e t C o m p u t i n g , R I S C Reduced\quad Instruction\quad Set\quad Computing,RISC ReducedInstructionSetComputing,RISC处理器,这些处理器都是32位的寄存器,32位的总线接口,32位的内部数据路径。除了32位数据,所有 C o r t e x − M Cortex-M Cortex−M处理器,也包括其它 A R M ARM ARM公司的处理器,也可以处理8比特和16比特数据。 C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器也支持一些64比特的数据操作。 C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器都是三级流水线设计(取指令,解码,执行),并且都是哈弗总线架构,也就是取指令和数据接入可以同时进行。 C o r t e x − M Cortex-M Cortex−M处理器的存储系统使用32比特寻址,因为这样多以它最有只能有最大 4 G B 4GB 4GB的地址空间。和其它 A R M ARM ARM公司的处理器一样, C o r t e x − M Cortex-M Cortex−M处理器基于 L o a d − S t o r e Load-Store Load−Store架构,这就意味着数据先要从存储空间中取出来,然后处理,最后再写入到存储空间中。取出,操作,写入的每一步都有对应的指令去操作。

处 理 器 , p r o c e s s o r 处理器,processor 处理器,processor仅仅是微控制器的一部分,存储系统,外设以及其它的接口由微控制器生产上来设计。因此 A R M ARM ARM公司的 处 理 器 , p r o c e s s o r 处理器,processor 处理器,processor广泛应用在各种各样的领域。但是这些设备共享同样的架构,在 A R M ARM ARM公司的处理器中, 架 构 , A r c h i t e c t u r e 架构,Architecture 架构,Architecture这个词有两方面的含义:

- Architecture: Instruction Set Architecture (ISA), programmer’s model (what the software sees), and debug methodology (what the debugger sees).

- Micro-architecture: Implementation-specific details such as interface signals, instruction execution timing, pipeline stages. Micro-architecture is processor design-specific.

这些年 A R M ARM ARM公司发布了很多不同的处理器,针对这些不同的处理器它们的 A R M ARM ARM架构也有很多不同的版本。例如, C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器都是基于 A R M v 7 − M ARMv7-M ARMv7−M架构的,一种指令集架构可以有不同的具体的实现,也就是不同的 微 架 构 , M i c r o − a r c h i t e c t u r e 微架构,Micro-architecture 微架构,Micro−architecture(不同的流水线等级,不同的总线协议)。

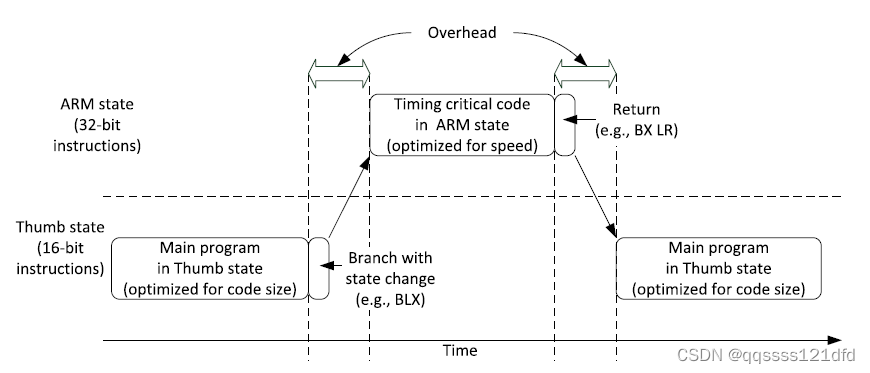

C o r t e x − M Cortex-M Cortex−M处理器使用的指令集叫做 T h u m b Thumb Thumb(它覆盖了16位和32位的 T h u m b Thumb Thumb指令,最新的 T h u m b − 2 Thumb-2 Thumb−2有同时覆盖16位和32位的指令)。 C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器包含了 T h u m b − 2 Thumb-2 Thumb−2技术(它允许16位和32位指令的混合,这样可以达到更高的代码密度和效率)。像 A R M 7 T D M I ARM7TDMI ARM7TDMI这种经典的 A R M ARM ARM处理器,处理器有两个操作状态:32位的 A R M ARM ARM状态和16位的 T h u m b Thumb Thumb状态。在 A R M ARM ARM状态(执行32位的 A R M ARM ARM指令集),指令是32位的且此时核可以高效执行所有支持的指令。在 T h u m b Thumb Thumb状态(执行16位的 T h u m b Thumb Thumb指令集),指令是16位的,这种情况下具有比较好的代码密度,但是此时 T h u m b Thumb Thumb指令没有 A R M ARM ARM指令的所有功能,这样有些操作就需要更多的指令来执行。为了在以上两种状态之间保持平衡,也就是为了在代码密度和效率之间达到最好的效果,经典的 A R M ARM ARM处理器的很多应用混合了 A R M ARM ARM代码和 T h u m b Thumb Thumb代码,然而这种混合不是在所有情况下都是可取的,因为在这两种状态之间的切换也是有开销的,如图所示。这两种状态的分离也增加了编译过程的复杂性。

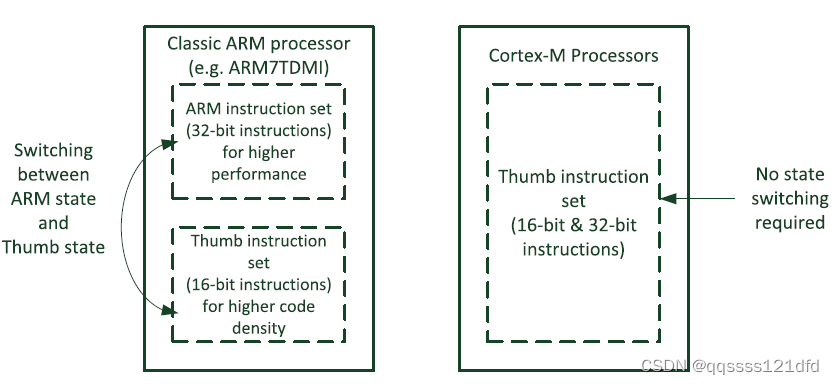

随着 T h u m b − 2 Thumb-2 Thumb−2技术的引进, T h u m b Thumb Thumb指令集被扩展到同时支持16比特和32比特的指令编码,现在 T h u m b − 2 Thumb-2 Thumb−2就可以满足所有的处理需求且不需要在两种状态之间进行切换。其实实际上 C o r t e x − M Cortex-M Cortex−M处理器是不支持32位的 A R M ARM ARM指令的。 C o r t e x − M Cortex-M Cortex−M处理器的中断处理也是在 T h u m b Thumb Thumb状态,但是经典的 A R M ARM ARM处理器的中断处理是在 A R M ARM ARM状态。图是经典的 A R M ARM ARM处理器和 C o r t e x − M Cortex-M Cortex−M处理器的指令集的区别对比,从图中可以看出经典的 A R M ARM ARM处理器同时支持32位的 A R M ARM ARM指令和16位的 T h u m b Thumb Thumb指令集, C o r t e x − M Cortex-M Cortex−M处理器只支持16位和32位混合的 T h u m b Thumb Thumb指令集。有了 T h u m b − 2 Thumb-2 Thumb−2技术之后,有以下几项好处:

- 不需要进行状态的切换,节省了执行时间和指令空间

- 不需要在代码源文件中指定 A R M ARM ARM和 T h u m b Thumb Thumb这两种状态,便于软件开发

- 便于更好的同时得到最好的代码密度,效率以及性能。

C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4处理器本身是没有储存器的,但是它们提供了总线接口,因此微控制器生产商可以自己根据自己的需求来配置相应的存储系统。一般微控制器生产商需要添加以下模块到自己的存储系统:

- Program memory, typically flash

- Data memory, typically SRAM

- Peripherals

边栏推荐

猜你喜欢

随机推荐

学会可视化大屏布局技巧,让领导都赞不绝口

Flutter | 判断 Text 组件是否显示完

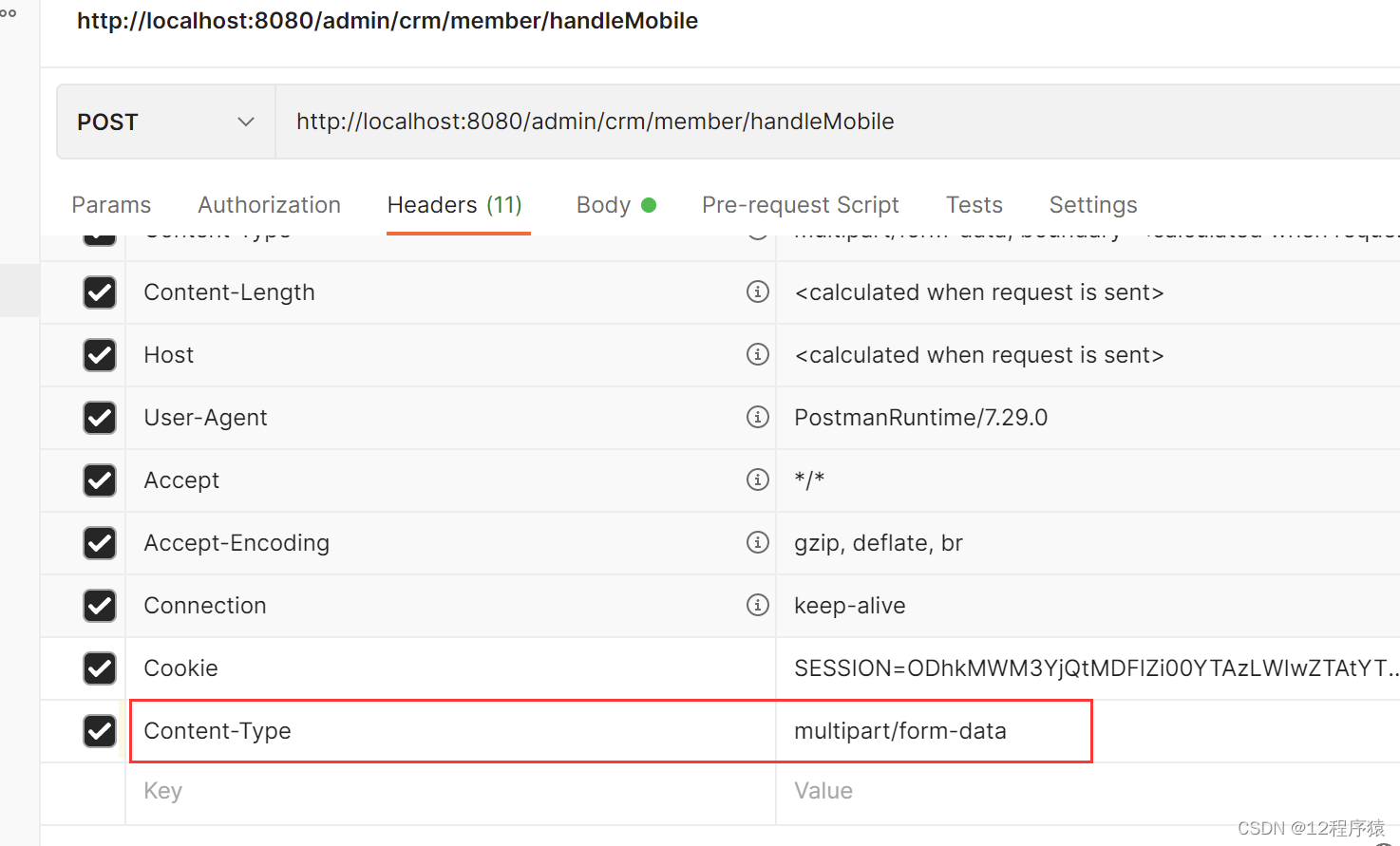

PostMan测试接口-----上传文件、导出excel

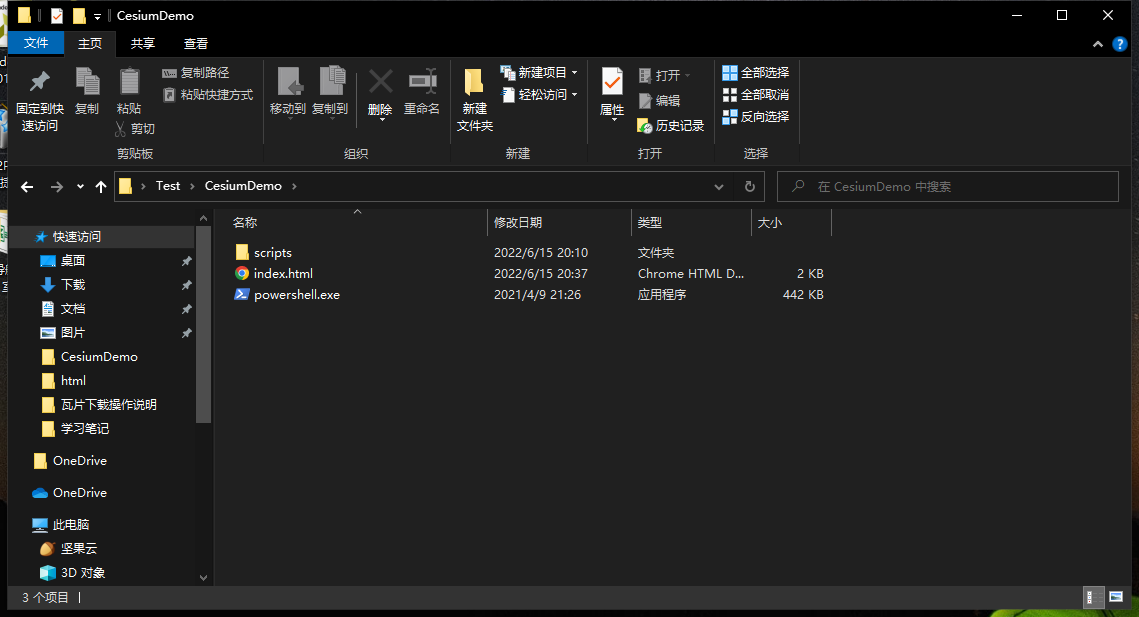

Cesium加载离线地图和离线地形

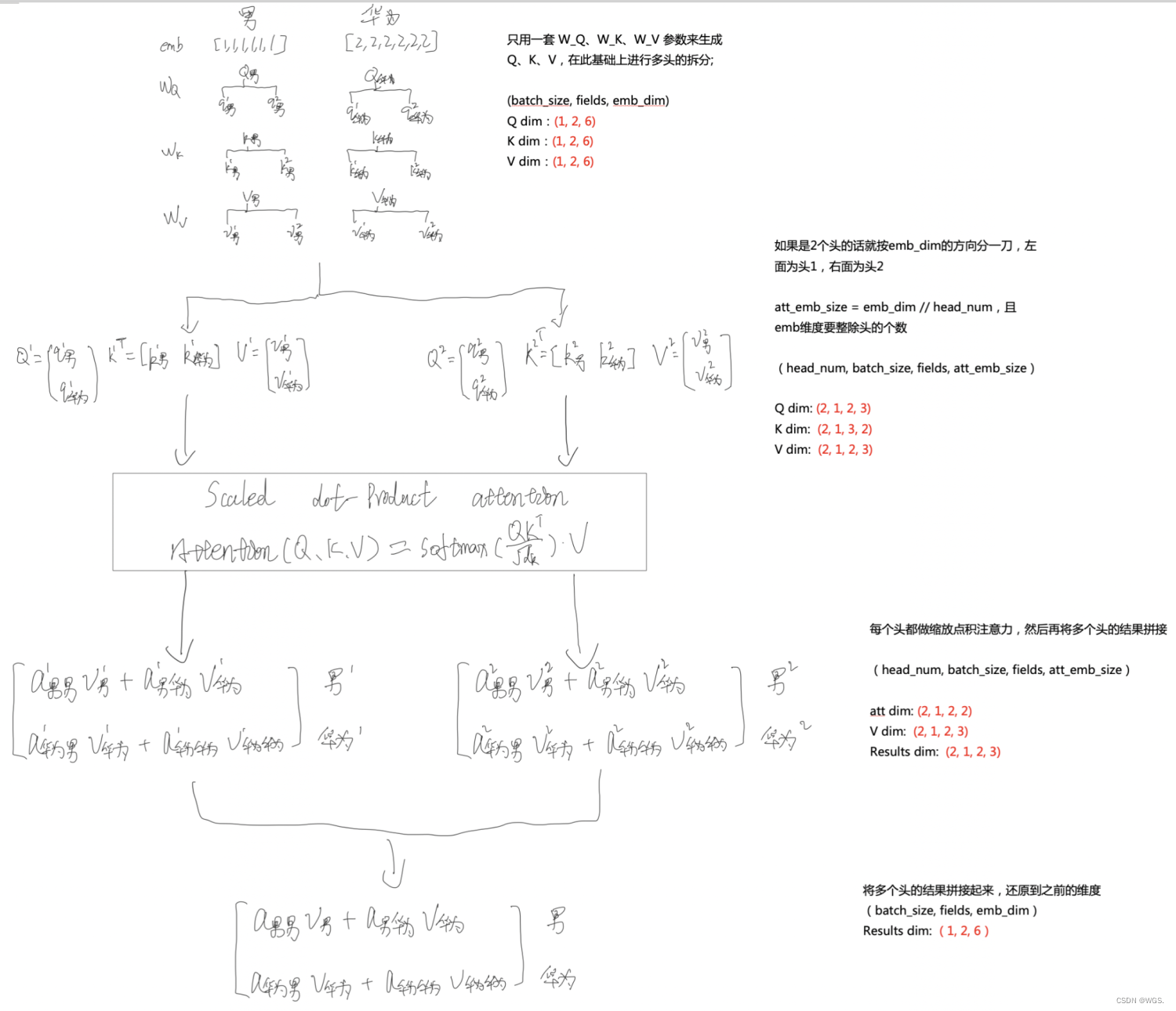

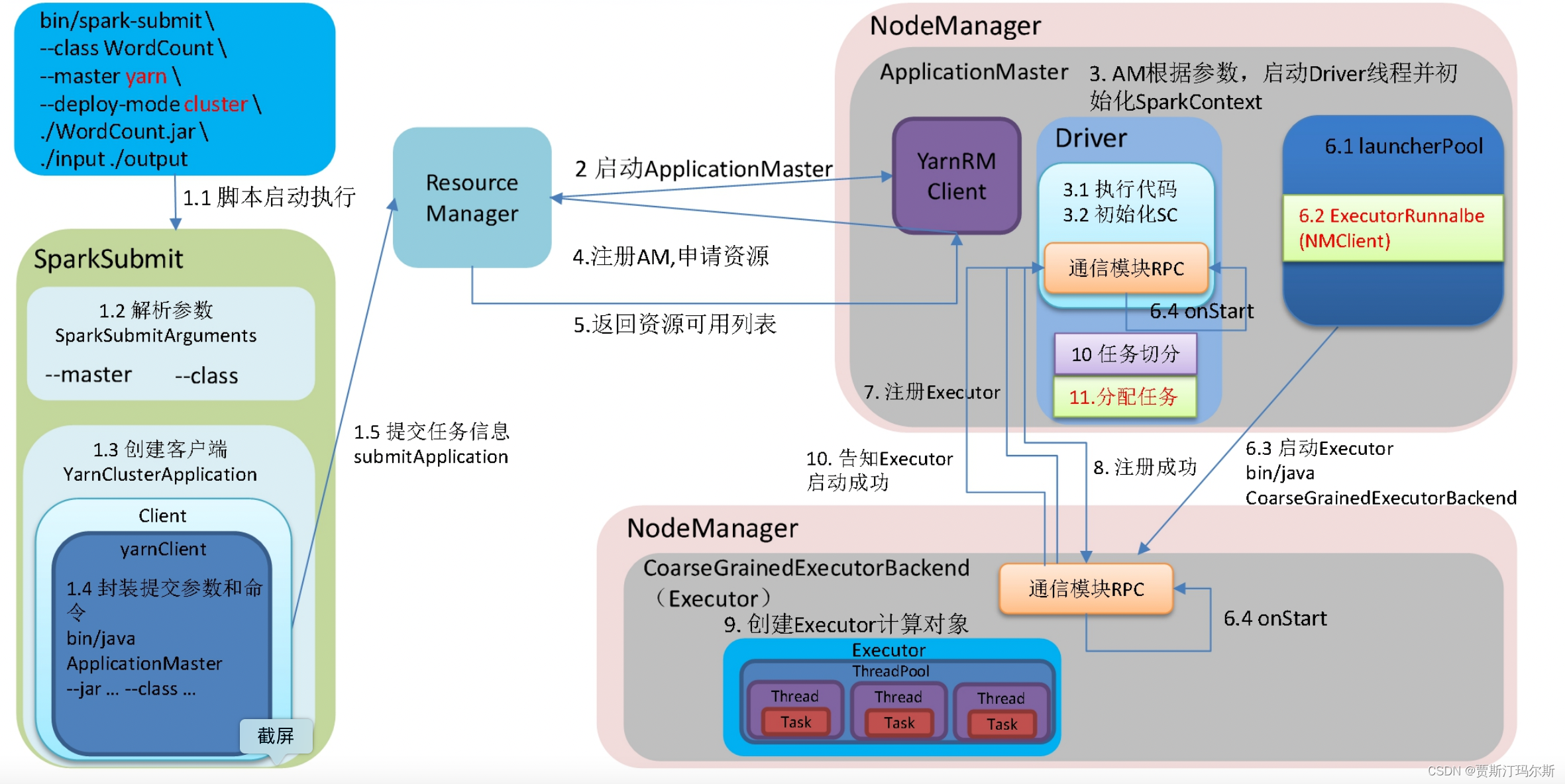

Multi-Head-Attention原理及代码实现

CISP-PTE Zhenti Demonstration

用代码构建UI界面

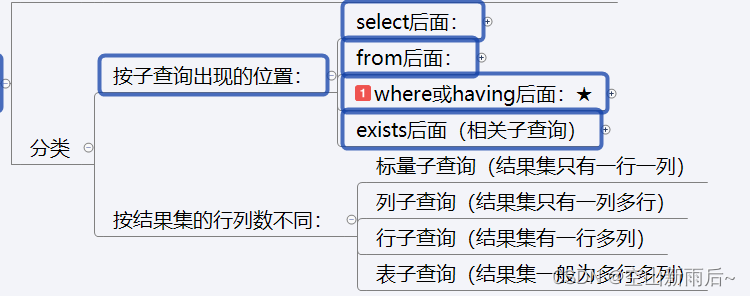

MySQL的 DDL和DML和DQL的基本语法

nvm 卸载详细流程

IFM网络详解及torch复现

MySQL的on duplicate key update 的使用

mysql的配置文件(my.ini或者 my.cnf)所在位置

SQL——左连接(Left join)、右连接(Right join)、内连接(Inner join)

MySql的安装配置超详细教程与简单的建库建表方法

Chrome 配置samesite=none方式

AutoInt网络详解及pytorch复现

502 bad gateway原因、解决方法

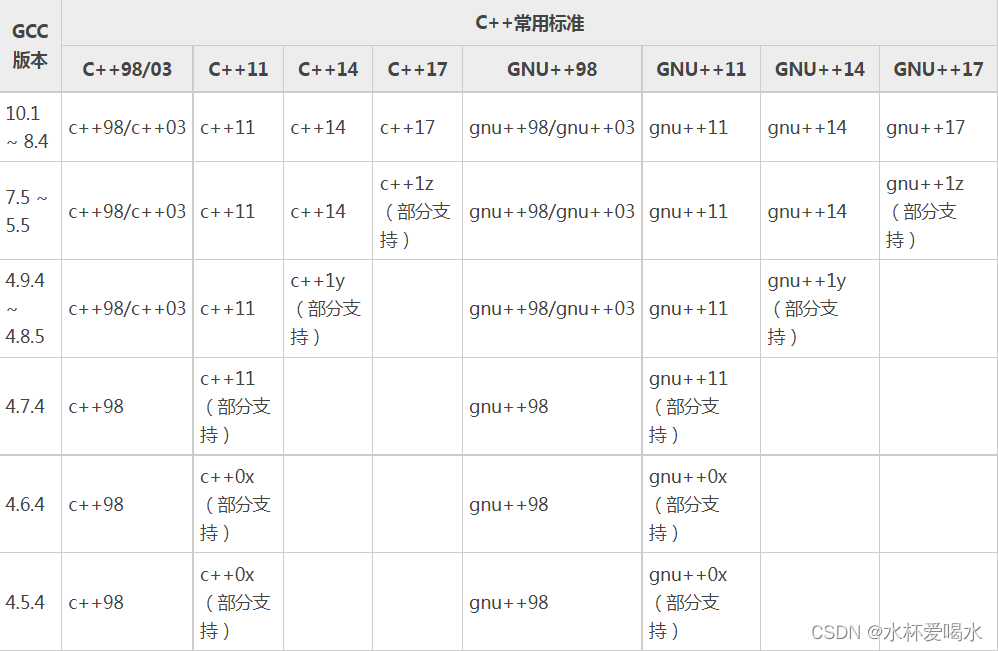

qt学习之旅--MinGW编译FFmpeg(32bit)

Detailed explanation and reproduction of AlexNet network

El - table column filter functions, control columns show and hide (effect and easy to implement full marks)